Next186 SoC PC

Project maintainers

Details

Created: Jun 10, 2013

Updated: May 7, 2019

SVN Updated: May 7, 2019

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 7 reported / 5 solved

Other project properties

Language:Verilog

Development status:Stable

Additional info:Design done, FPGA proven, Specification done

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

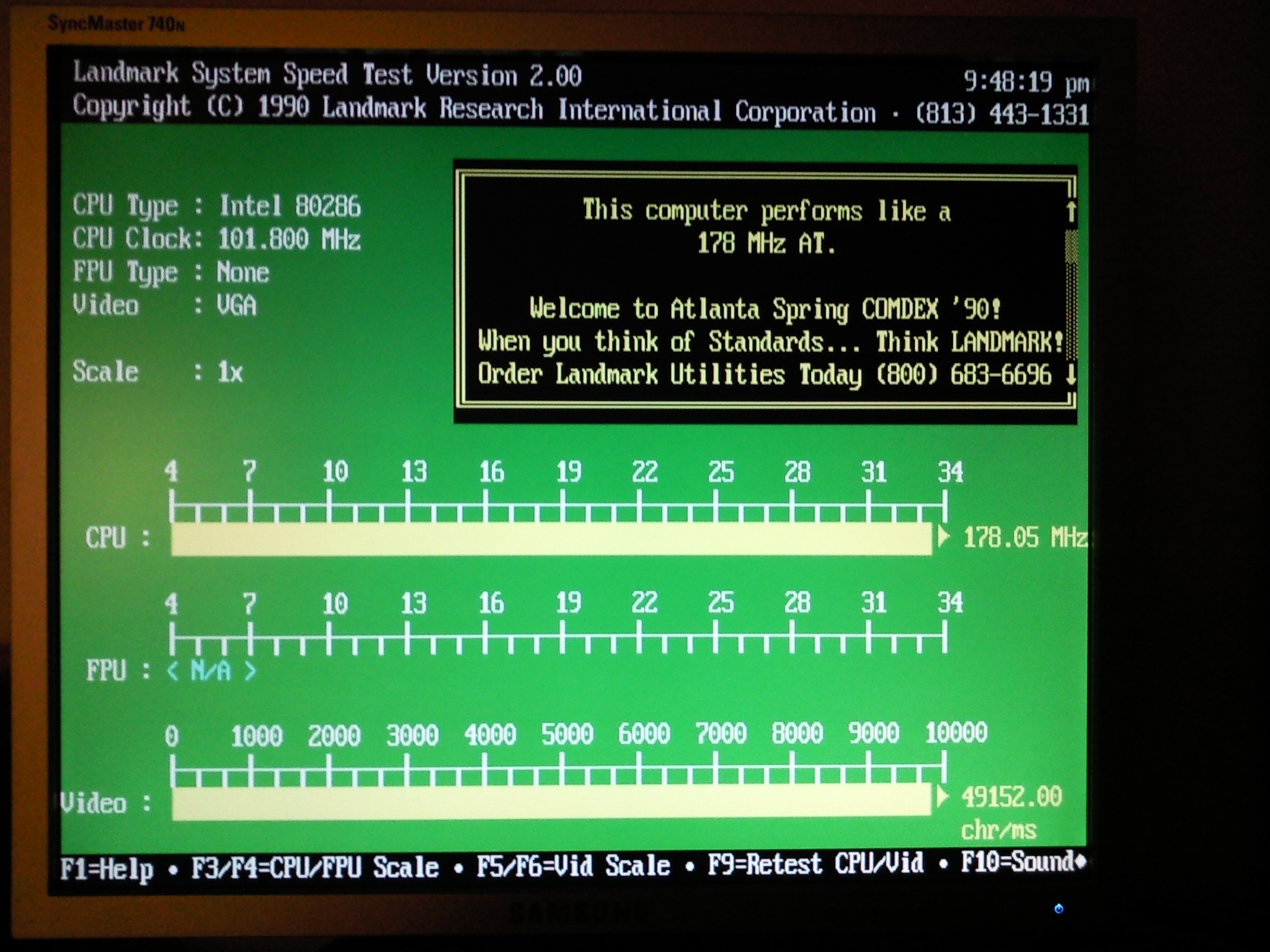

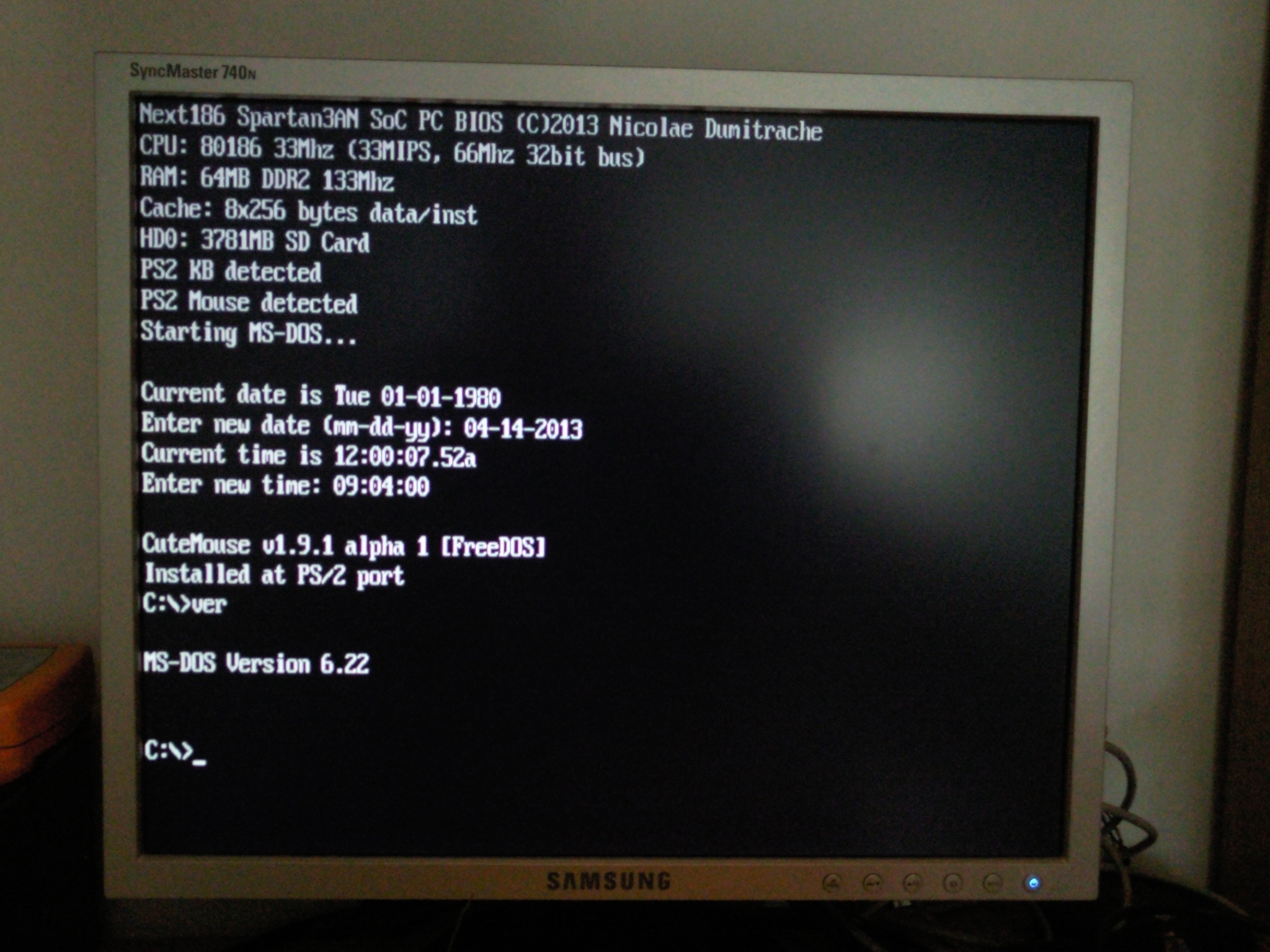

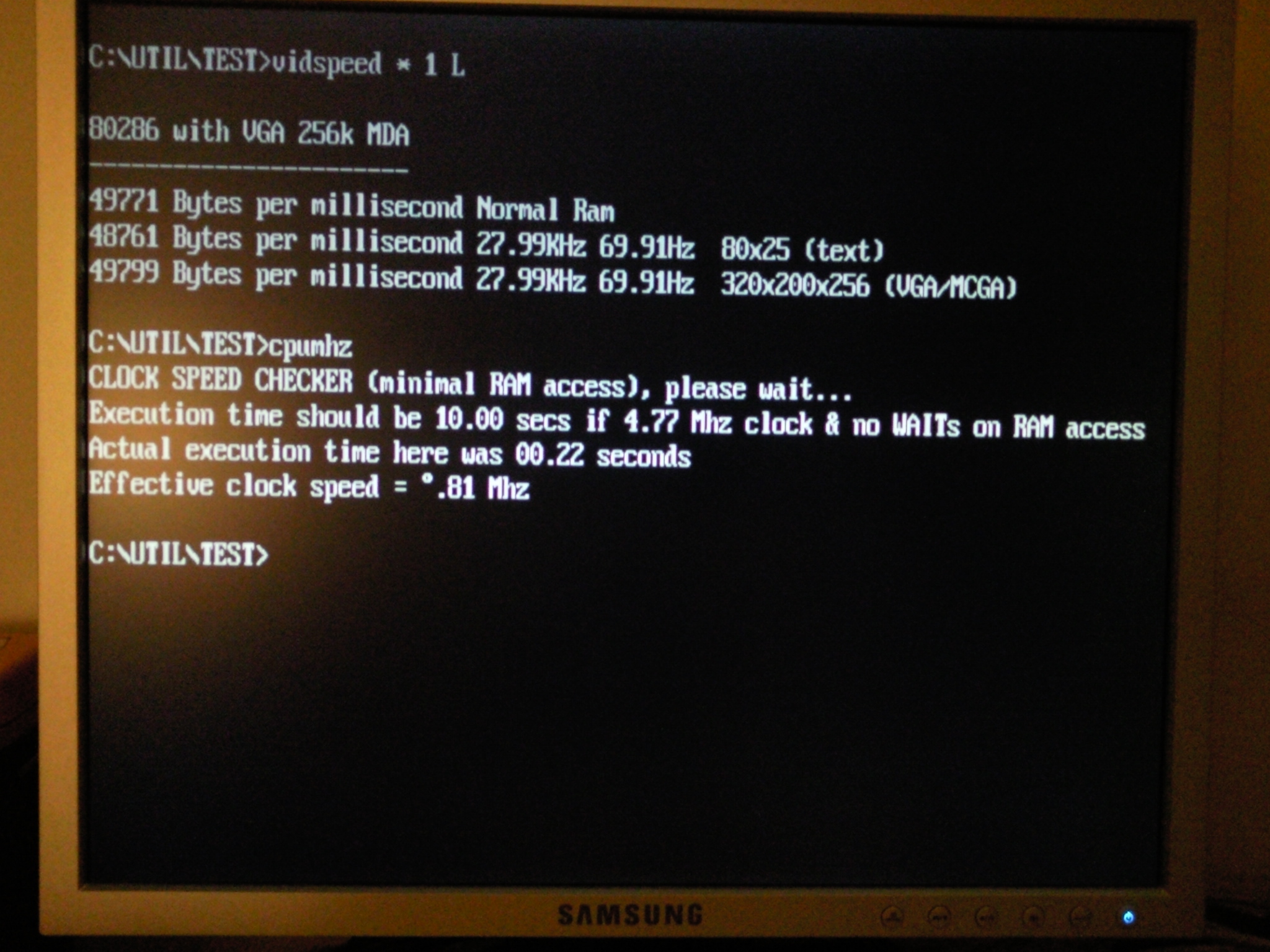

PC AT SoC based on Next186 core. CPU runs at up to 80 MHz (80 MIPS), up to 64MB of RAM, HMA available.

Able to run DOS6.22, FreeDos, Windows3.0, GeOS.

Able to run DOS 8086, 80186 applications (most of 80286 applications/games are running ok). May run real mode 32bit 386 applications with a 32bit software extender (see EMU386).

Video modes available: 80x25x256 text, 320x200x256 MCGA, 640x480x256 VESA VBE mode 101h, 640x480x16 VGA planar, 320x200x16 EGA planar, ModeX support.

PS2 8042 controller for keyboard and mouse.

Simplified 8259 PIC, 8253 timer.

44100Khz stereo sound, compatible with Disney Sound Source.

32bit DSP - allows real time mp3 play (mp3 player sources provided).

8bit GPIO.

UART 8250 - COM1.

Bootstrap and BIOS ASM code provided.

Besides the FPGA board, a SD HC card is required for the hard disk implementation.

The system is able to run Windows3.0 in real mode.

Contents

CPU: Next186 core, (C) Nicolae Dumitrache, available on OpenCores.

VGA: A custom VGA core which implements the text mode 3h 80x25x256, the MCGA graphic mode 13h 320x200x256, VESA graphic mode 101h 640x480x256, mode 12h 640x480x16 planar, mode 0dH 320x200x16 planar, ModeX. Unlike the standard VGA, the mode 13h can support 8 hardware pages.

TIMER: a simplified 8253

PIC: a simplified 8259 programmable interrupt controller

Kb, Mouse: a simplified 8042 PS2 controller

Hard Disk - a SD HC 4GB external memory card is used as HD. For simplicity, I access it in SPI mode, being able to get a transfer rate up to 2 MB/s. All the transfer work is done by the CPU, with a minimal hardware interface.

RS232 - 8250 compatible COM1.

Speaker sound, Disney Sound Source and 44100Khz stereo custom output.

Reset button

NMI button (useful for debugging, see Turbo Debugger)

HALT LED

No DMA is necessary, as Next186 CPU is able to transfer up to 33MB/s with REP MOVSW.

More details are commented in the Verilog sources and in the BIOS code.

As for the IP cores, I used:

2KB FIFO (32bit in, 16bit out, independent clocks) for VGA

MIG memory interface

4KB true dual port 8bit SRAM for text mode font

2KB true dual port 8/32bit SRAM for 256bit VGA DAC color palette

16KB true dual port 32bit SRAM for CPU cache

DCM and PLL

The CPU clock is independent from DDRAM clock. The bus interface between CPU and the cache memory is 32bit width and it is working at double the CPU frequency.

Booting

The system have no ROM, only 64MB of dynamic RAM and 4KB of code/data cache (8 lines of 256 bytes). In order to be able to boot, the cache is preloaded with the bootstrap code and marked as "dirty". At the first flush, the cache content will be transferred to RAM. The bootstrap code tries to load the BIOS (8KB) from the latest 16 sectors of the SD card, at 0F000h:0E000h. If the SD card is not present, or BIOS is unavailable, the bootstrap code waits on RS232 (115200bps) an executable, loads it at 0f000h:100h and executes it.

Memory

The memory is split as follows:

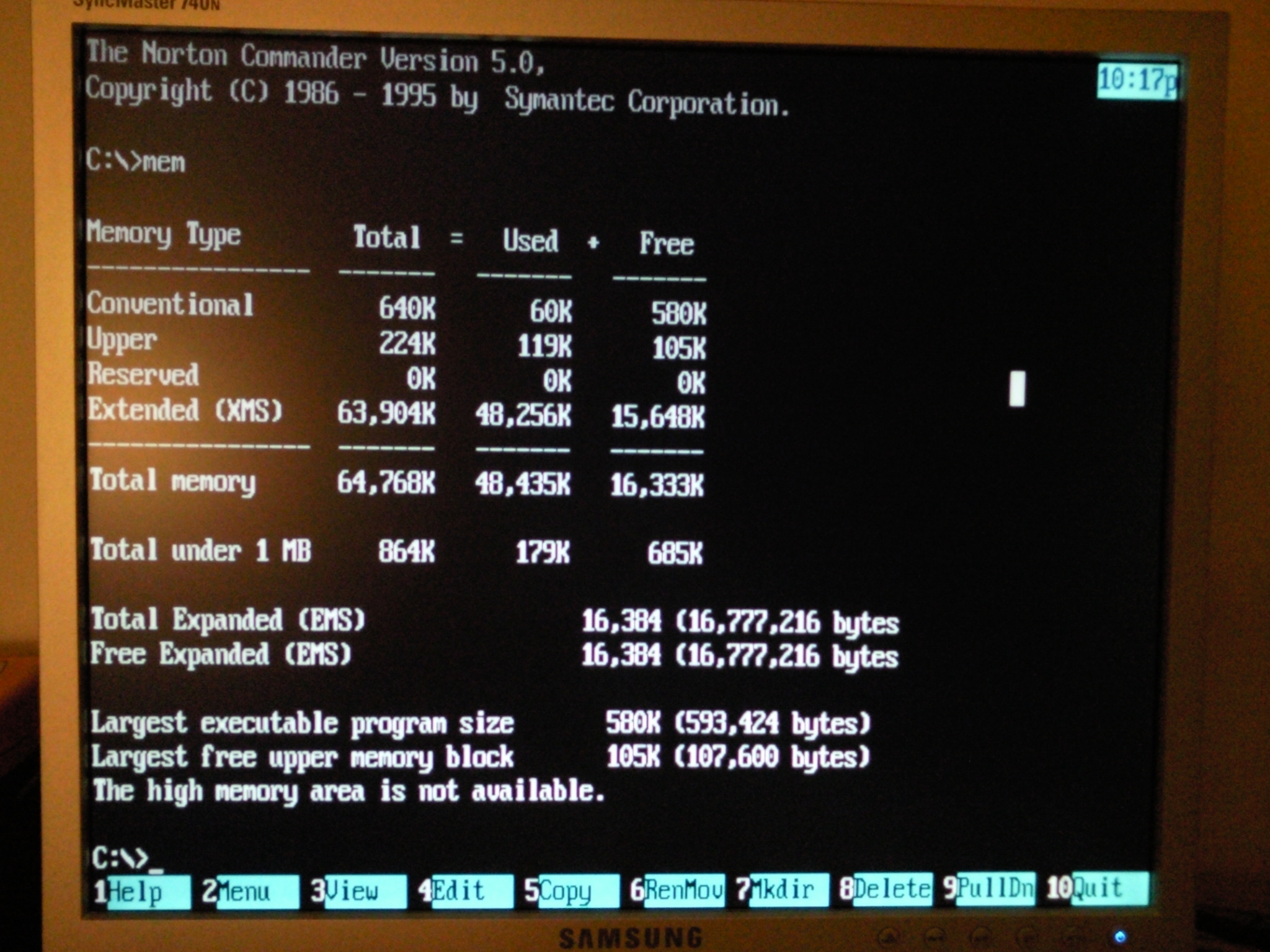

640KB low DOS memory

512KB video memory (which can be mapped over segments 0a000h and 0b000h)

224KB upper memory, available to DOS through the XMM manager

32KB ROM area, from which only the latest 8KB are actually used by the BIOS code.

64KB HMA

512KB available for the old INT15h extended memory mechanism

The rest up to 64MB is available as extended memory (XMM), and in my DOS configuration, is used as follows:

2MB for smartdrv (increases a lot the disk access)

28MB RAM disk (not really necessary, as the SD hard disk + smartdrv is fast enough, but 64MB RAM is too much for DOS)

16MB EMM (I use a LIMulator for 286)

15MB XMM

The RAM is accessed in parallel by the CPU and the VGA. VGA uses a 2KB FIFO and have priority over CPU when the FIFO is empty.

When the FIFO is not empty, the CPU have priority.

The RAM is divided in 64Kb pages. Each page can be mapped over each of the first 16 64Kb segment addresses. This mechanism is used for accessing the video memory in mode 13h (8 pages) and mode 101h VESA, and also for the extended/expanded memory access.

Software

I provided in the package the assembler source code for the boot loader and for the BIOS.

The BIOS code is quite small, taking only 8KB beginning with 0f000h:0e000h. All the rest of the RAM upper memory is available for DOS.

The VESA VBE interface and all required paged memory access code for XMM is contained inside the BIOS.

A RS232 communication application executable is also provided (SerialComm.exe). It can be used to transfer applications or files from a PC to the Next186 SoC through a serial link.

Lately I installed GEOS (Geoworks Ensemble v2.0 and Breadbox Ensemble v4.1.2). With 16MB XMS swap space, almost 900KB global heap (in the first megabyte), and a CPU ~80 times faster than standard XT, it's working like a charm in VESA 640x480x256 colors.

Screenshots

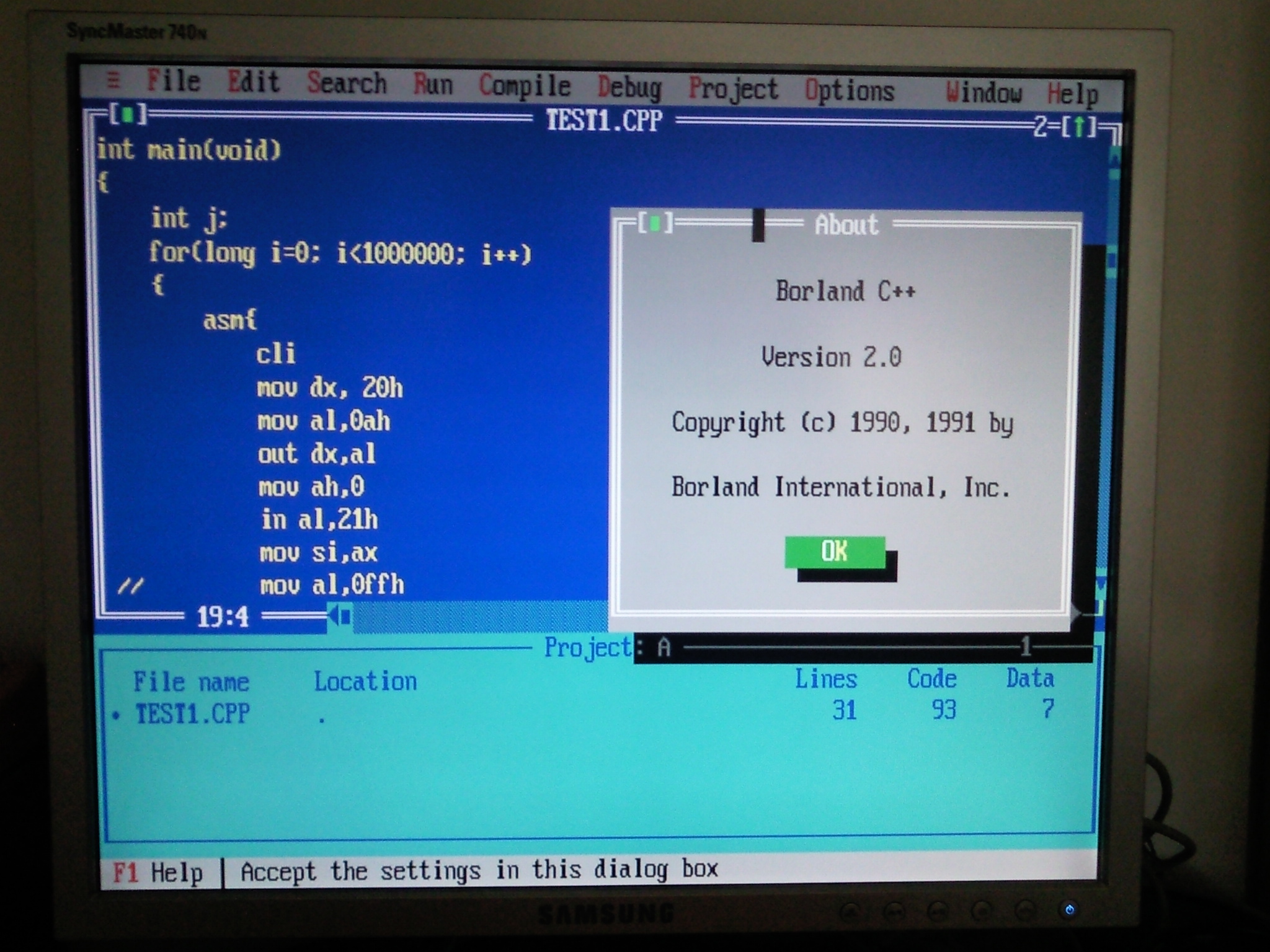

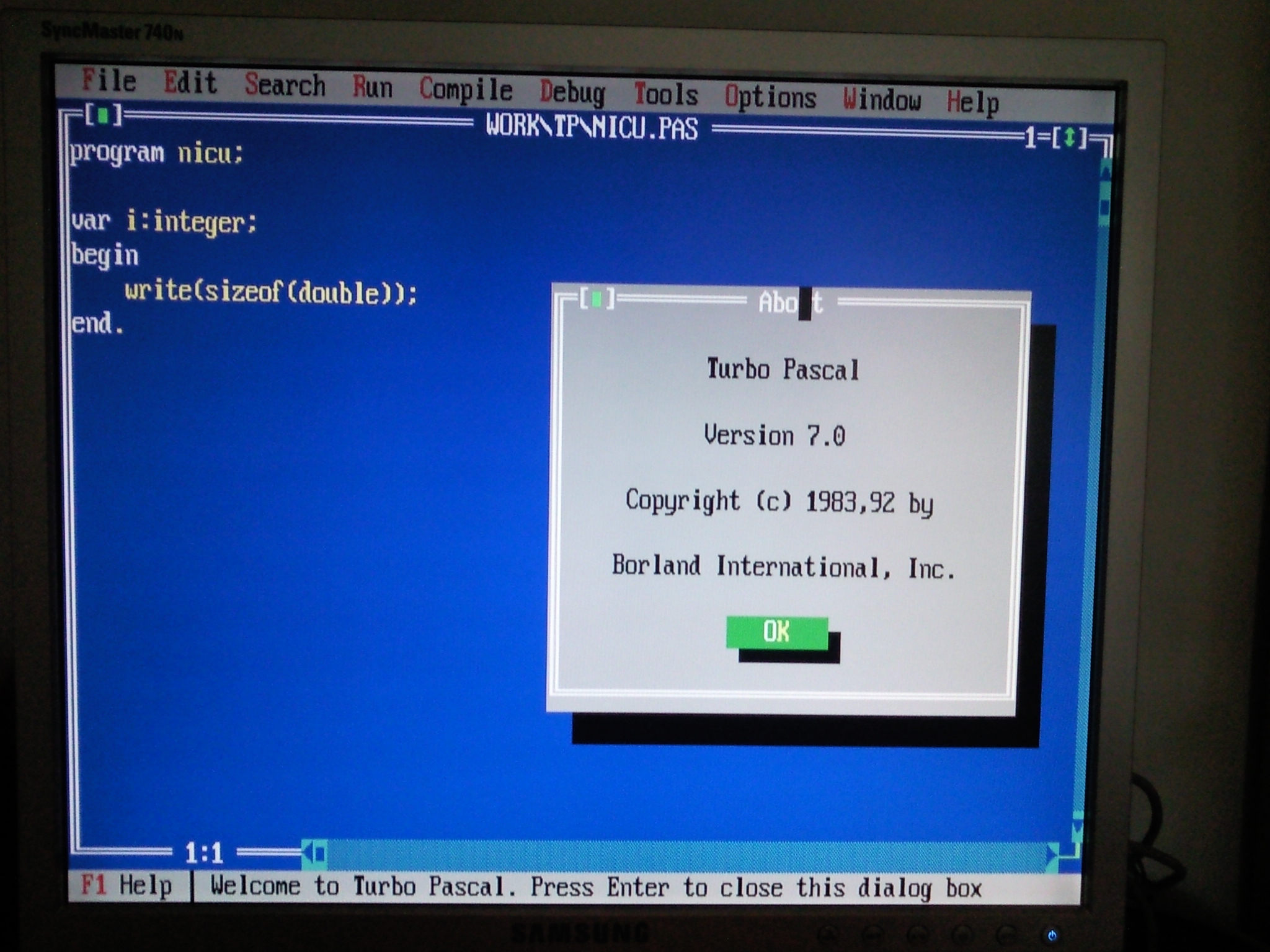

Borland C++ v2.0, Turbo Pascal v7.0

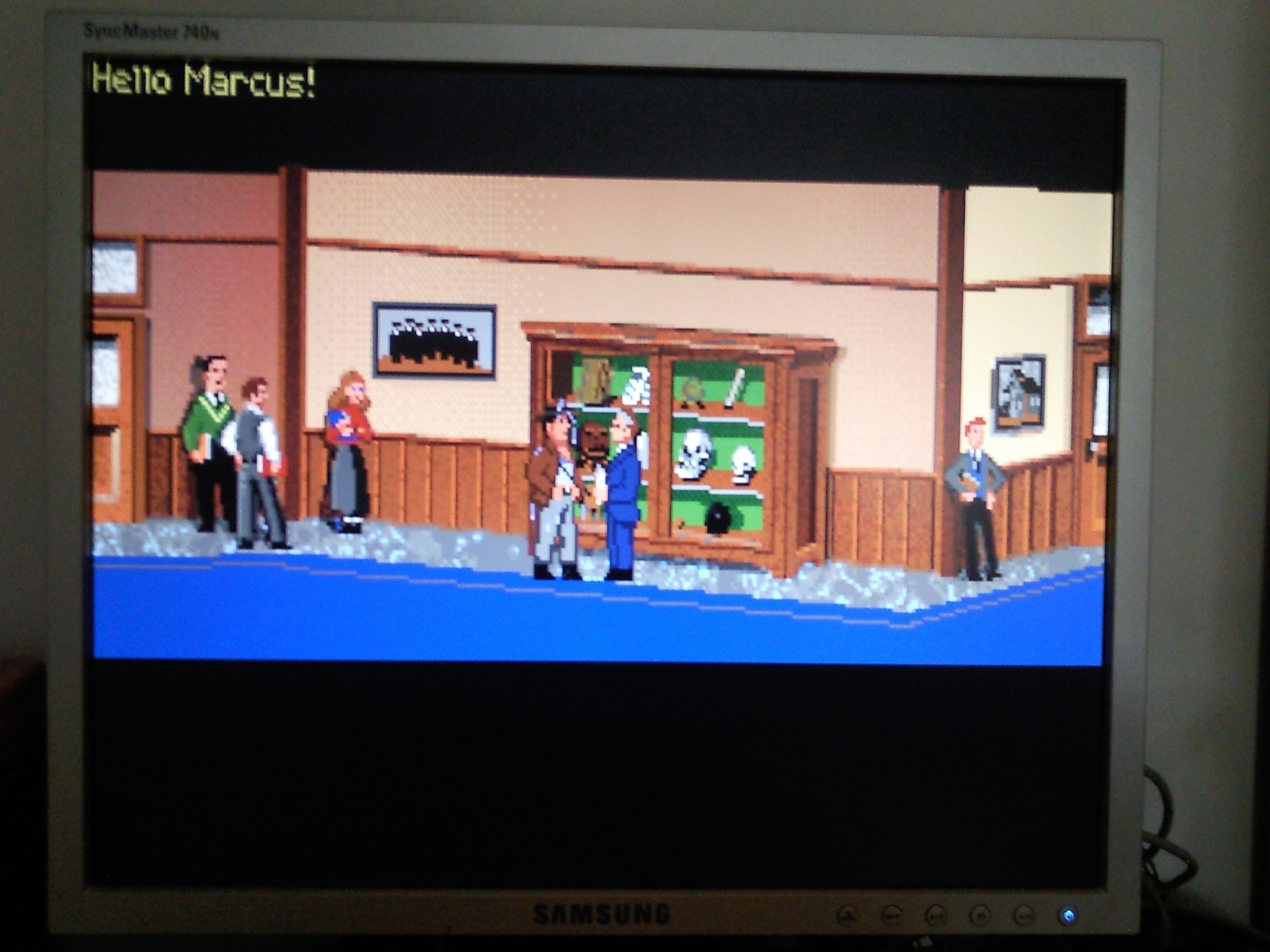

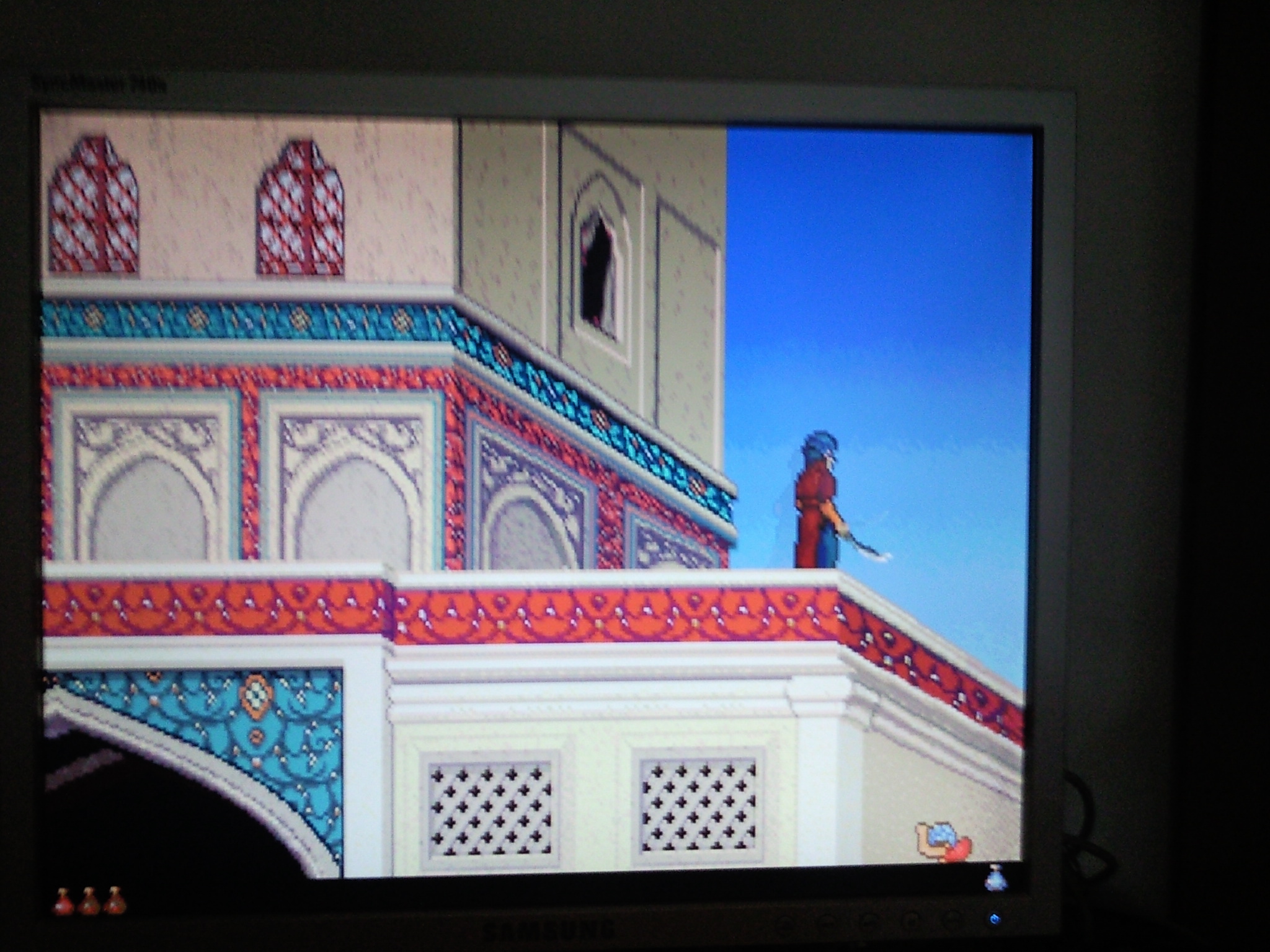

Indy MCGA, Prince of Persia 2 MCGA

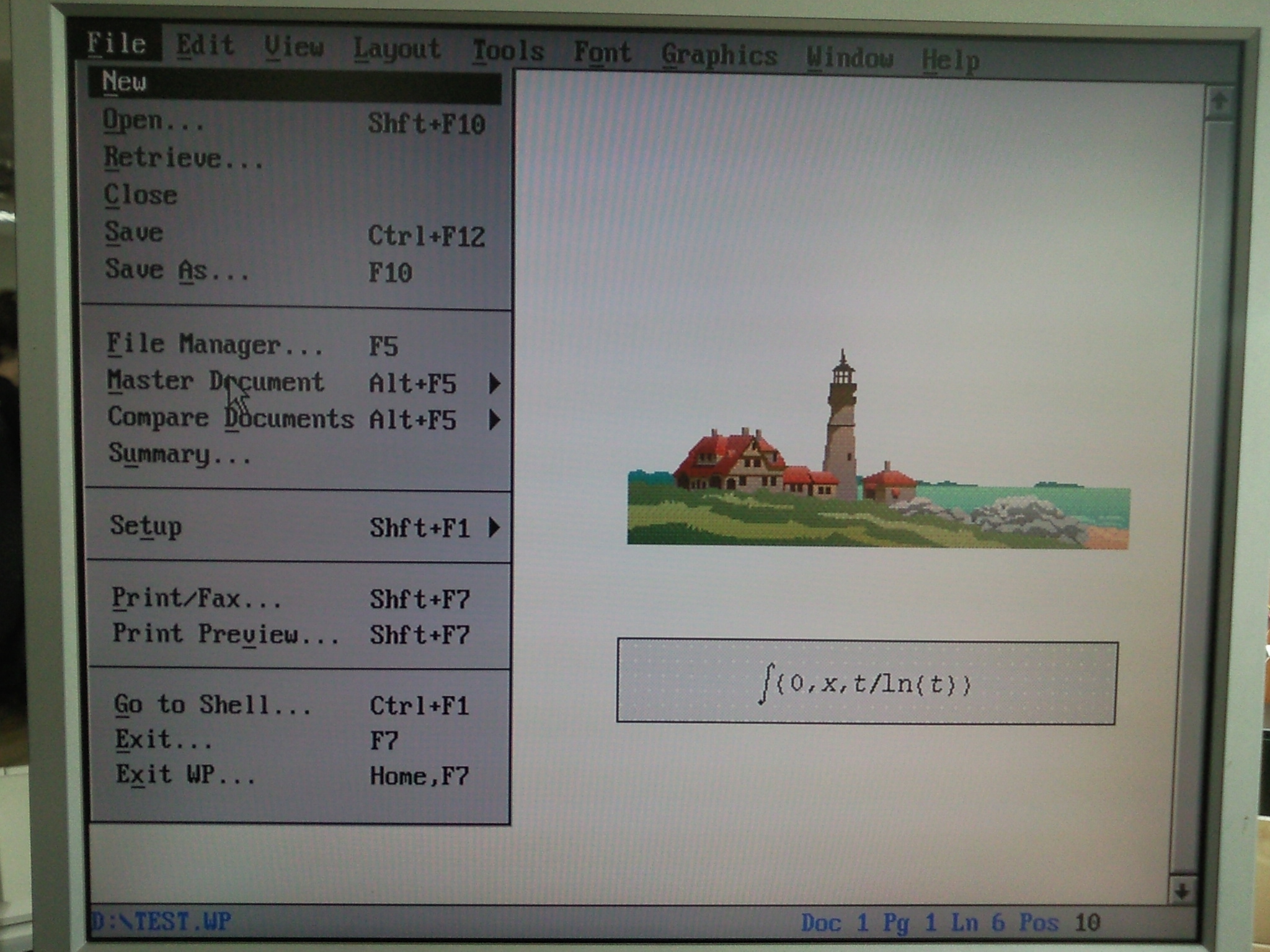

WordPerfect 6.0 VESA 640x480x256, BattleChess4000 VESA 640x480x256

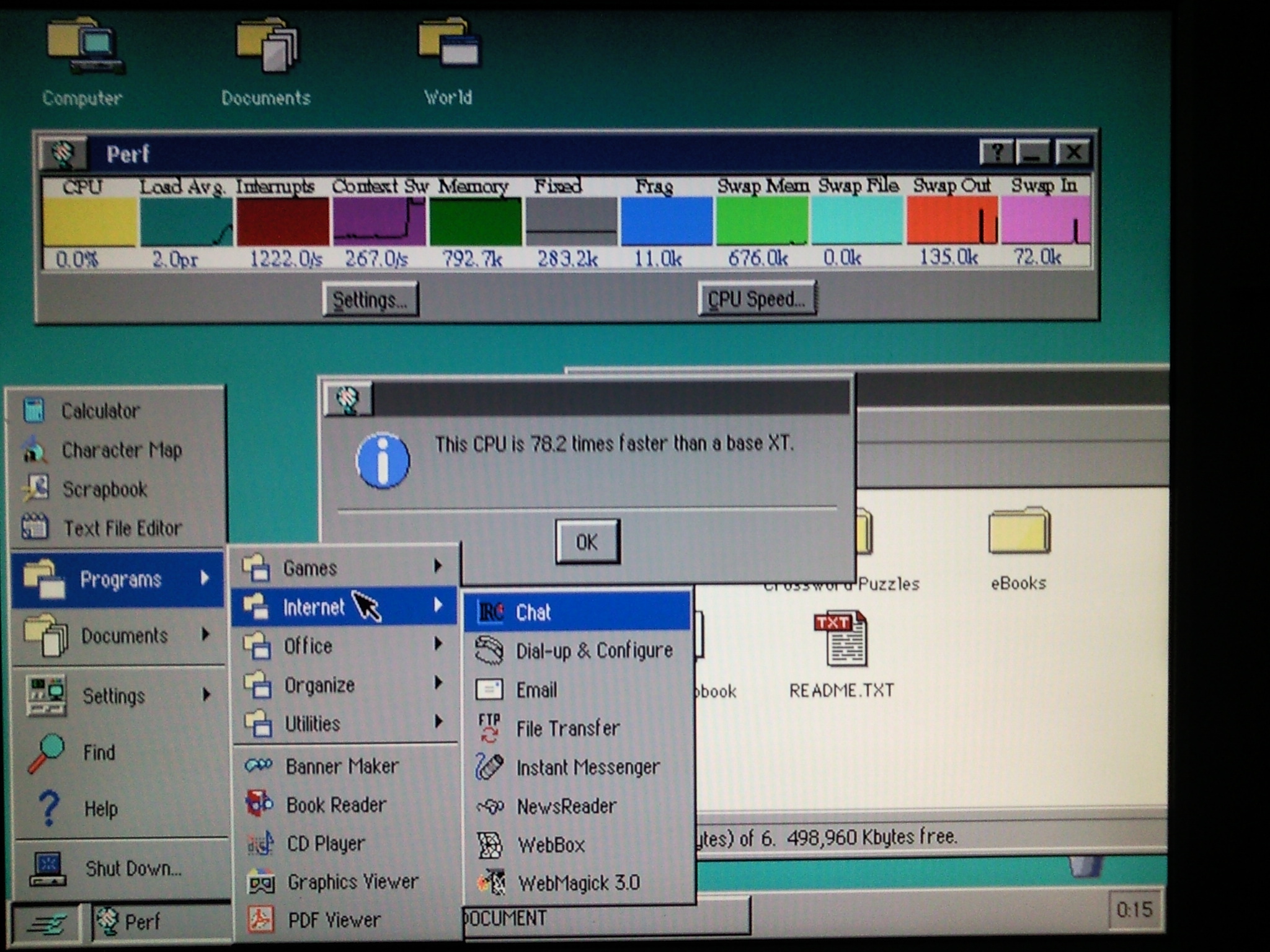

GeoWorks Ensemble 2.0 VESA 640x480x256, Breadbox Ensemble v4.1.2 VESA 640x480x256

LATTICE MachXO2 -7000HE port

I uploaded the latest port of Next186 SoC, on the Valentin Angelovski's tiny but great FleaFPGA board (Lattice MachXO2-7000H, 32MB SDRAM, http://www.fleasystems.com/fleaFPGA.html

It is working at 100Mhz SDRAM, 50Mhz bus, 25Mips) ~20000 Dhrystone 2.1

It takes ~95% FPGA area.

Ported on other FPGA boards

Some new features added to the newest ports:

- 16KB cache

- 44100Khz stereo sound, compatible with Disney Sound Source

- 32bit DSP - allows real time mp3 play (mp3 player sources provided in the project archives)

- 8bit GPIO

- UART 8250 - COM1

- Full projects with pre-built images available for download (some images were obtained by manually overclocking the PLLs after build).

Ported on the following FPGA platforms:

- Papilio Pro(Spartan6 xc6slx9-2) - runs at 94Mhz bus, 47Mhz CPU, 144Mhz(288MB/s) SDRAM (8MB), 85Mhz DSP, 5000LUT6 (82% from 5720), VGA18bit

- Pipistrello(Spartan6 xc6slx45-3) - runs at 105Mhz bus, 52.5Mhz CPU, 200Mhz(800MB/s) DDRAM (64MB), 100Mhz DSP, 5060LUT6 (18% from 27288), HDMI

- FleaFPGA (Lattice MachXO2-7000HE) - runs at 50Mhz bus, 25Mhz CPU, 100Mhz(200MB/s) SDRAM (32MB), no DSP, 6541LUT4 (95% from 6864), VGA12bit

- DE2-115 (Altera EP4CE115F29C7) - runs at 105Mhz bus, 52.5Mhz CPU, 135Mhz(540MB/s) SDRAM (64MB), 97Mhz DSP, 9248LE (8% from 114480), VGA24bit

- Nexys4 (Artix7 xc7a100t-1) - runs at 160Mhz bus, 80Mhz CPU, 110Mhz(220MB/s) CellularRAM (16MB), 150Mhz DSP, 4656LUT6 (7% from 63400), VGA12bit

- DE0-Nano (Altera EP4CE22F17C6N) - runs at 100Mhz bus, 50Mhz CPU, 147Mhz(294MB/s) SDRAM (32MB), 100Mhz DSP, 13691LUT4 (61% from 22320), VGA18bit, Adlib - requires interface similar with Papilio Pro one

- FleaFPGA 'Ohm' (Lattice LFE5U-25F) - runs at 90Mhz bus, 45Mhz CPU, 166Mhz(333MB/s) SDRAM (32MB), 75Mhz DSP, ~11329LUT4 (47% from 24288), HDMI

Adlib/OPL3

An Adlib/OPL3 implementation was added on Nexys4 version.

- Nexys4 (Artix7 xc7a100t-1) - runs at 160Mhz bus, 80Mhz CPU, 110Mhz(220MB/s) CellularRAM (16MB), 150Mhz DSP, ~6100LUT6 (9% from 63400), VGA12bit

The 160Mhz/150MHz FPGA image is obtained from the 120MHz/120MHz image by overclocking the routed design DCMs.

The OPL3 engine takes around 500LUT6, and the interface between the Next186 CPU and OPL3 is done with a NextZ80 CPU (~800LUT6).

The OPL3 engine drives 18 channels and 36 operators and needs at least 45Mhz clock. The 2-nd part of 4 operator channels is simplified, and the OPL3 rhythm is not yet implemented.

The access ports are 0x388 (bank 0 address), 0x389(bank 0 data), 0x38A(bank 1 address), 0x38B(bank 1 data). No delay is required between writes.

All supported DOS games and applications should be able play Adlib music with this Next186 SoC version.

I want to give credit to the MAME emulator developers. The MAME OPL3 emulator was the starting point for this Verilog implementation.

Internet browsing

You need an ESP8266 board, programmed with the following SLIP Router firmware:

https://github.com/martin-ger/esp_slip_router

and configure it with your ssid/password.

Connect ESP8266 to the RS232 external interface of Next186SoC (TX_EXT, RX_EXT).

COM1 port is multiplexed with the internal RS232 (usually embedded on dev board) and the external RS232. In order to use the external RS232 you need to write 1 to port 1 (use debug.exe, or make a simple .com executable):

mov al, 1

out (1), al

Install Kermit

http://www.columbia.edu/kermit

and use SLIP8250.COM packet driver inside (in autoexec.bat):

lh slip8250 0x60 SLIP 4 0x3f8 115200 16384

Install Arachne 16bit DOS browser, configure it with the IP addresses and start browsing (you will need few MB of XMS free in order to work well, otherwise Arachne will sometimes crash on bigger pages). The screen can be configured in VGA640x480x16 or VESA640x480x256.

You can also use telnet from the Kermit package.

You can write your net apps with WATTCP library, but take care that it uses for DNS query an invalid source port address (997). The ESP8266 DNS firmware requires a port bigger than 1024, so if you are using a precompiled executable made with WATTCP you net to patch it (search for 0x03e5 - usually you will find a mov ax,0x03e5 - and replace it with 0x23e5).

USB

I optionally provide a USB interface for mouse and keyboard instead of the PS/2 one. For the moment only low speed devices are supported (hot plug and hot swap, and even two mices or two keyboards in parallel). The USB interface is driven by one Next8080 core (a stripped down NextZ80 with some additions). I uploaded the Lattice Diamond project for FleaFPGA Ohm board: https://fleasystems.com/fleaFPGA_Ohm.html