Ethernet SMII

Project maintainers

Details

Name: smii

Created: Mar 19, 2009

Updated: Mar 19, 2009

SVN Updated: Apr 28, 2009

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Created: Mar 19, 2009

Updated: Mar 19, 2009

SVN Updated: Apr 28, 2009

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Star6you like it: star it!

Other project properties

Category:Communication controller

Language:Verilog

Development status:Beta

Additional info:Specification done

WishBone compliant: No

WishBone version: n/a

License:

Language:Verilog

Development status:Beta

Additional info:Specification done

WishBone compliant: No

WishBone version: n/a

License:

Overview

The Serial Media Independent Interface, SMMI, is a low pin count version of the MII normally used between ethernet MAC and PHY.

The Serial Media Independent Interface (SMII) is designed to satisfy the following requirements:- Convey complete MII information between a 10/100 PHY and MAC with two pins per port

- allow multi port MAC/PHY communications with one system clock

- Operate in both half and full duplex

- per packet switching between 10 Mbit and 100 Mbit data rates

- allow direct MAC to MAC communication

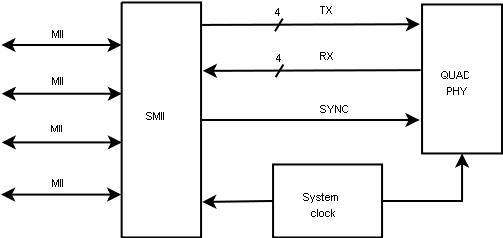

SMII is composed of two signals per port, global synchronization signal, and a global 125 MHz reference clock.

All signals are synchronous to the clock.

| Name | From | To | Use |

|---|---|---|---|

| RX | PHY | MAC | Receive data and control |

| TX | MAC | PHY | Transmit data and control |

| SYNC | MAC | PHY | Synchronization |

| CLOCK | System | MAC & PHY | Synchronization |

Typical application

The picture above shows a typical application with an external quad Ethernet PHY that connects to four Ethernet MACs inside a FPGA.

This example uses a total of 10 signal to implement this function.

Resource usage

| Target | smii_sync | smii_rxtx |

|---|---|---|

| ACTEL ProASIC3 | 10 slices | 117 slices |

| ALTERA Cyclone III | Combinatorial functions 2 DFFs 10 |

Combinatorial functions 52 DFFs 36 |

Status

- 2009 March 13

initial design commited to repository.

Limited testing performed on OpenRISC hardware platform

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.