PlTbUtils

PlTbUtils

Project maintainers

Details

Created: Apr 14, 2013

Updated: May 12, 2020

SVN Updated: May 12, 2020

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:VHDL

Development status:Stable

Additional info:Design done, Specification done

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

PlTbUtils makes it easy to create automatic, self-checking simulation testbenches, and to locate bugs during a simulation. It is a collection of functions, procedures and testbench components that simplifies creation of stimuli and checking results of a device under test.

Features:

- Simulation status printed in transcript windows as well as in waveform window (error count, checks count, number and name of current test, etc).

- Check procedures which output meaningful information when a check fails.

- Clear SUCCESS/FAIL message at end of simulation.

- Easy to locate point in time of bugs, by studying increments of the error counter in the waveform window.

- User-defined information messages in the waveform window about what is currently going on.

- Transcript outputs prepared for parsing by scripts, e.g. in regression tests.

- Configurable status messages for use in continuous integration environments, e.g. TeamCity.

- Reduces amount of code in tests, which makes them faster to write and easier to read.

- Tests can easily be included or skipped in a test run.

- Supports VHDL-93 and later.

- Supports most popular VHDL simulators, including ModelSim, ISE ISim and Vivado XSim.

It is intended that PlTbUtils will constantly expand by adding more and more functions, procedures and testbench components. Comments, feedback and suggestions are welcome to pela.opencores@gmail.com .

Project web page: http://opencores.org/project,pltbutils

Subversion repository URL: http://opencores.org/ocsvn/pltbutils/pltbutils/trunk

Subversion export command:

svn export http://opencores.org/ocsvn/pltbutils/pltbutils/trunk pltbutils

See the PlTbUtils Specification.

A quick look

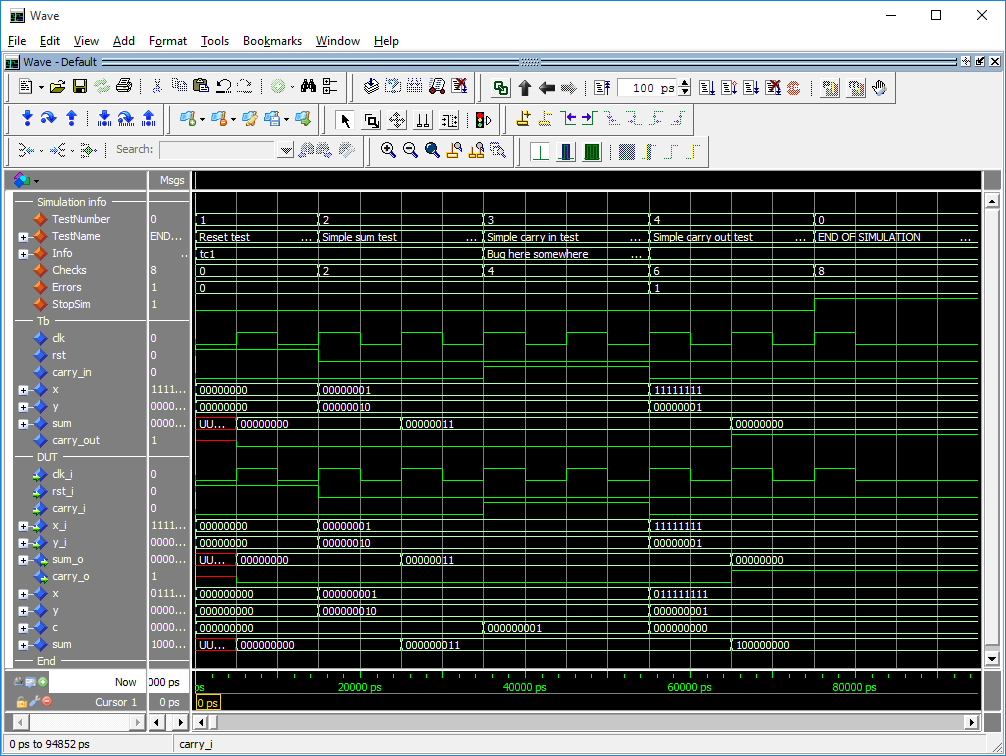

During a simulation, the waveform window shows current test number, test name, user-defined info, accumulated number of checks and errors. When the error counter increments, a bug has been found in that point in time.

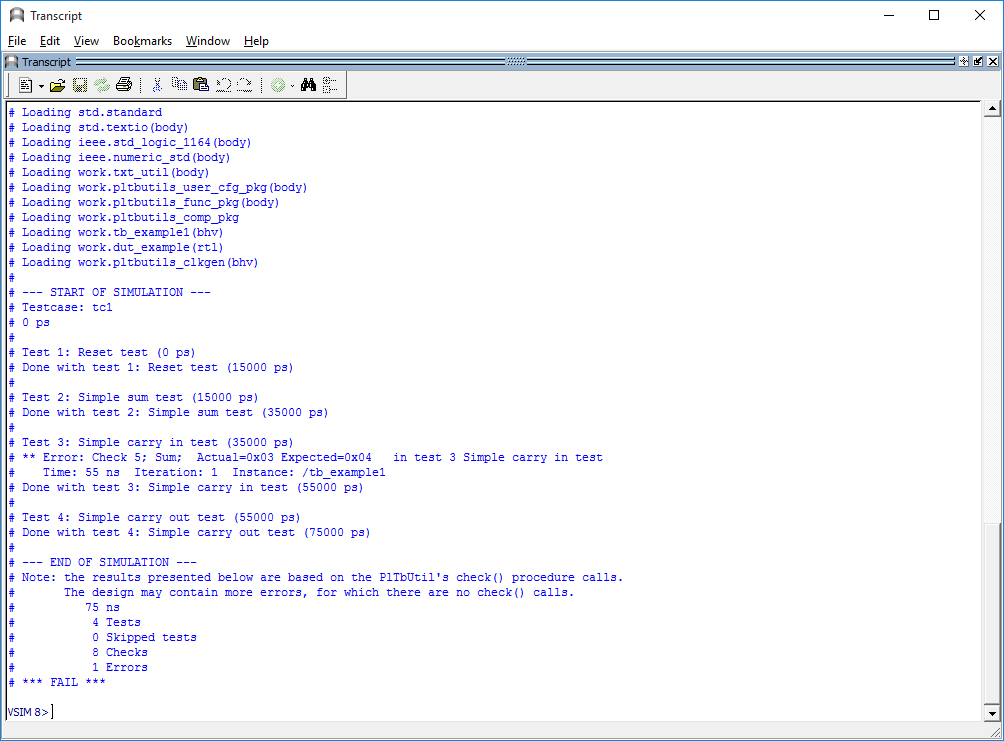

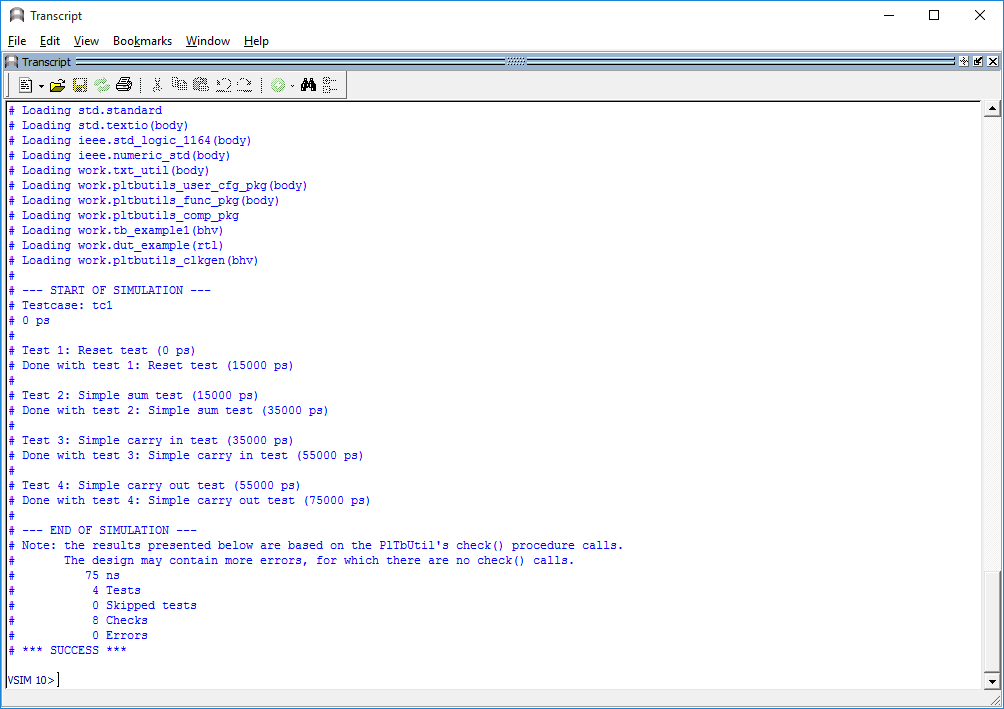

The transcript window clearly shows points in time where the simulation starts, ends, and where errors are detected. The simulation stops with a clear SUCCESS/FAIL message, specifically formatted for parsing by scripts.

The testcase code is compact and to the point, which results in less code to write, and makes the code easier to read, as in the following example.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use work.txt_util.all;

use work.pltbutils_func_pkg.all;

-- NOTE: The purpose of the following code is to demonstrate some of the

-- features of PlTbUtils, not to do a thorough verification.

architecture tc1 of tc_example2 is

begin

p_tc1 : process

variable pltbv : pltbv_t := C_PLTBV_INIT;

begin

startsim("tc1", "", pltbv, pltbs);

rst <= '1';

carry_in <= '0';

x <= (others => '0');

y <= (others => '0');

starttest(1, "Reset test", pltbv, pltbs);

waitclks(2, clk, pltbv, pltbs);

check("Sum during reset", sum, 0, pltbv, pltbs);

check("Carry out during reset", carry_out, '0', pltbv, pltbs);

rst <= '0';

endtest(pltbv, pltbs);

starttest(2, "Simple sum test", pltbv, pltbs);

carry_in <= '0';

x <= std_logic_vector(to_unsigned(1, x'length));

y <= std_logic_vector(to_unsigned(2, x'length));

waitclks(2, clk, pltbv, pltbs);

check("Sum", sum, 3, pltbv, pltbs);

check("Carry out", carry_out, '0', pltbv, pltbs);

endtest(pltbv, pltbs);

starttest(3, "Simple carry in test", pltbv, pltbs);

print(G_DISABLE_BUGS=0, pltbv, pltbs, "Bug here somewhere");

carry_in <= '1';

x <= std_logic_vector(to_unsigned(1, x'length));

y <= std_logic_vector(to_unsigned(2, x'length));

waitclks(2, clk, pltbv, pltbs);

check("Sum", sum, 4, pltbv, pltbs);

check("Carry out", carry_out, '0', pltbv, pltbs);

print(G_DISABLE_BUGS=0, pltbv, pltbs, "");

endtest(pltbv, pltbs);

starttest(4, "Simple carry out test", pltbv, pltbs);

carry_in <= '0';

x <= std_logic_vector(to_unsigned(2**G_WIDTH-1, x'length));

y <= std_logic_vector(to_unsigned(1, x'length));

waitclks(2, clk, pltbv, pltbs);

check("Sum", sum, 0, pltbv, pltbs);

check("Carry out", carry_out, '1', pltbv, pltbs);

endtest(pltbv, pltbs);

endsim(pltbv, pltbs, true);

wait;

end process p_tc1;

end architecture tc1;