Phrases recognition with Machine Learning #ML using #MYO device based on #FPGA

✅ Read related topics: https://vasanza.blogspot.com/2019/10/diseno-de-sistemas-digitales-proyectos.html

✅ Objectives: Characterize the acceleration signals in the time domain. Compare the performance of one or more classification algorithms. Measure the processing times,% of CPU used and% of memory used, in the NIOSII processor, ARM or both, as the case may be (radar chart).

✅ Goals: Implement an Embedded System based on FPGA that reads preprocessed data (.csv or .mat) stored in memory Double Data Rate 3 Synchronous Dynamic Random-Access Memory (DDR3-SDRAM), access will be done through the Hard Processor System (HPS ). The classifier training process can be done on a conventional computer, then the model trained in C ++ must be executed by the NIOSII processor in the FPGA. The system must have a VGA or HDMI monitor as output that shows the results of the classification clearly, the classification algorithms that the student can use are: k-means, k-medoids, DBSCAN, Spectral Clustering, Hierarchical Clustering, SVM or Neural Network (NN). The FPGA-based system is the one who executes the classifier blocks, but the groups that have telematics students will not use the VGA or HDMI output but must access the visual interface through a web application deployed on a web application server running on a linux operating system with an ARM processor.

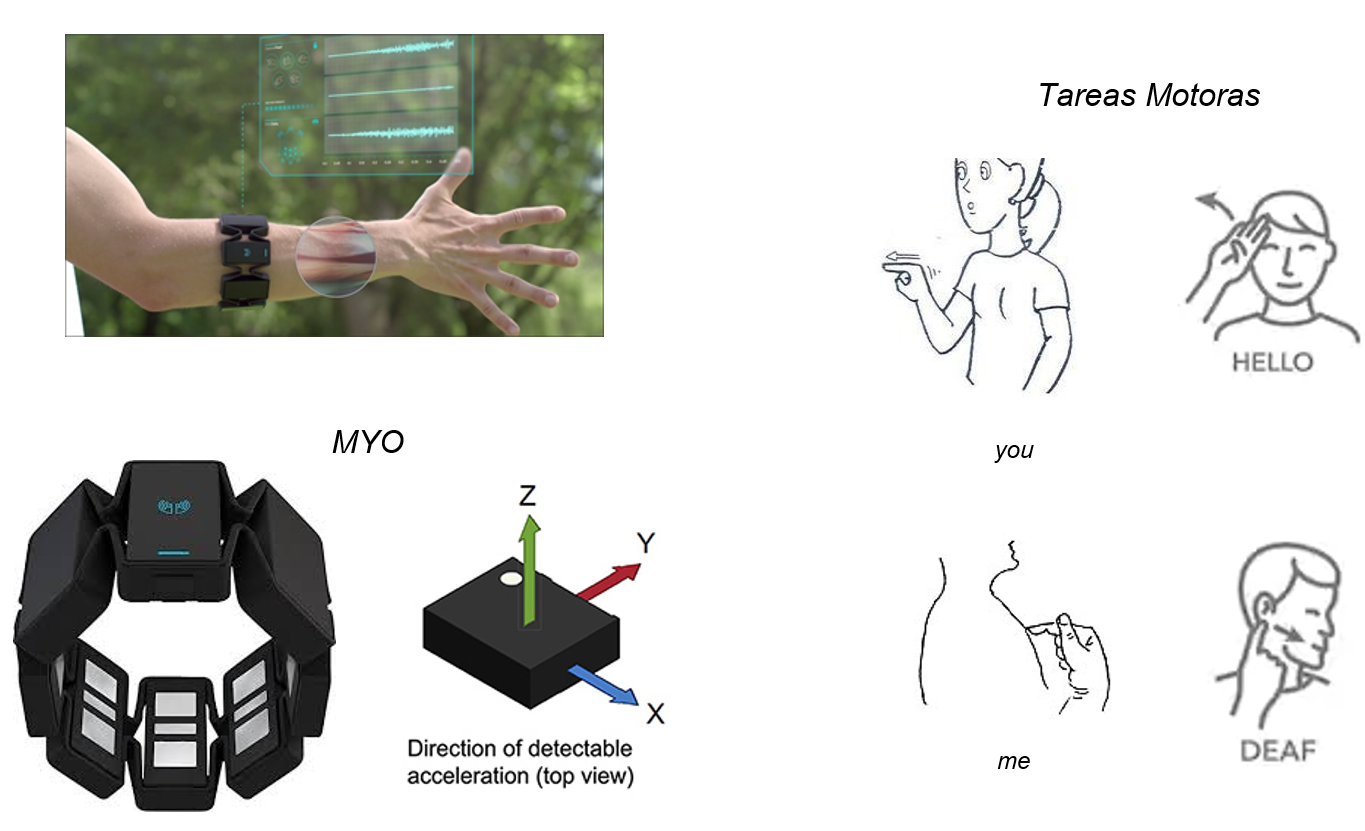

✅ Abstract: The acceleration signals measured by the MYO commercial device that represent motor activity during the execution of sentences in sign language of any subject, these signals contain information in the time and frequency domain corresponding to the execution of a certain sentence. The temporal acceleration signals of three axes (x, y, z) can be analyzed using classification algorithms to automatically determine what type of phrase the subject is performing, this detection is used for the interpretation and visualization of the meaning (VGA monitor / HDMI) for someone who does not know sign language. The present work does not include the acceleration signal acquisition stage, we will use previously acquired signals measured from the forearm by the MYO device. A post acquisition processing will be carried out that includes: characterization and classification 1. Characterization is the process of extracting relevant information during time windows equivalent to the execution of motor tasks, it is recommended to use RMS values of each of the e axes of the accelerometer incorporated in the MYO device. The time windows are defined in the experiment during the acquisition of the acceleration signals. The most representative characteristics with which the algorithms perform best are used in the classification. The classification algorithms that require previous stages of preprocessing and characterization belong to Machine Learning algorithms such as: KNN, Kmeans, dbscan, etc. 3-9

✅ Reference: 1 C ++ machine learning library for embedded electronics and robotics: https://github.com/FidoProject/Fido 2 Asanza, V., Peláez, E., Loayza, F., Mesa, I., Díaz, J., & Valarezo, E. (2018, October). EMG Signal Processing with Clustering Algorithms for motor gesture Tasks. In 2018 IEEE Third Ecuador Technical Chapters Meeting (ETCM) (pp. 1-6). IEEE. 3 Navarría, L., Rapallini, J. A., & Quijano, A. A. (2009). Development of neural networks in FPGA. 4 Muñoz, G. T., Chávez, S. J. Z., & Casrua, V. H. B. (2008). Neural Network Implemented in FPGA. ELECTRONICS — UNMSM, 9. 5 Santos, P., Ouellet-Poulin, D., Shapiro, D., & Bolic, M. (2011, May). Artificial neural network acceleration on FPGA using custom instruction. In Electrical and Computer Engineering (CCECE), 2011 24th Canadian Conference on (pp. 000450-000455). IEEE. 6 https://inaoe.repositorioinstitucional.mx/jspui/bitstream/1009/94/1/PanoAAD.pdf 7 Gadea-Gironés, R., Colom-Palero, R., & Herrero-Bosch, V. (2018). Optimization of Deep Neural Networks Using SoCs with OpenCL. Sensors (Basel, Switzerland), 18 (5). 8 Aliaga, R. J., Gadea, R., Colom, R. J., Monzó, J. M., Lerche, C. W., & Martínez, J. D. (2009). System-on-chip Implementation of Neural network Training on FPGA. International Journal On Advances in Systems and Measurements Volume 2, Number 1, 2009. 9 C. Cedeño Z., J. Cordova-Garcia, V. Asanza A., R. Ponguillo and L. Muñoz M., "k-NN-Based EMG Recognition for Gestures Communication with Limited Hardware Resources," 2019 IEEE SmartWorld, Ubiquitous Intelligence & Computing, Advanced & Trusted Computing, Scalable Computing & Communications, Cloud & Big Data Computing, Internet of People and Smart City Innovation (SmartWorld / SCALCOM / UIC / ATC / CBDCom / IOP / SCI), Leicester, United Kingdom , 2019, pp. 812-817.

✅ Hardware: (1) # DE10_Standard or # DE10_Nano (1) VGA / HDMI monitor

✅ Database: https://drive.google.com/open?id=1RZRXbVOn2QL987879lfD4_g5ZLt_E0ad