| 1 |

40 |

zero_gravi |

[](https://github.com/stnolting/neorv32)

|

| 2 |

2 |

zero_gravi |

|

| 3 |

37 |

zero_gravi |

# The NEORV32 RISC-V Processor

|

| 4 |

|

|

|

| 5 |

43 |

zero_gravi |

[](https://github.com/stnolting/neorv32/actions?query=workflow%3A%22Processor+Check%22)

|

| 6 |

|

|

[](https://github.com/stnolting/neorv32/actions?query=workflow%3A%22RISC-V+Compliance%22)

|

| 7 |

2 |

zero_gravi |

[](https://github.com/stnolting/neorv32/blob/master/LICENSE)

|

| 8 |

|

|

[](https://github.com/stnolting/neorv32/releases)

|

| 9 |

|

|

|

| 10 |

32 |

zero_gravi |

* [Overview](#Overview)

|

| 11 |

47 |

zero_gravi |

* [Status](#Status)

|

| 12 |

2 |

zero_gravi |

* [Features](#Features)

|

| 13 |

|

|

* [FPGA Implementation Results](#FPGA-Implementation-Results)

|

| 14 |

|

|

* [Performance](#Performance)

|

| 15 |

30 |

zero_gravi |

* [Top Entities](#Top-Entities)

|

| 16 |

2 |

zero_gravi |

* [**Getting Started**](#Getting-Started)

|

| 17 |

40 |

zero_gravi |

* [Contribute/Feedback/Questions](#ContributeFeedbackQuestions)

|

| 18 |

2 |

zero_gravi |

* [Legal](#Legal)

|

| 19 |

|

|

|

| 20 |

|

|

|

| 21 |

|

|

|

| 22 |

32 |

zero_gravi |

## Overview

|

| 23 |

2 |

zero_gravi |

|

| 24 |

23 |

zero_gravi |

The NEORV32 Processor is a customizable microcontroller-like system on chip (SoC) that is based

|

| 25 |

36 |

zero_gravi |

on the RISC-V-compliant NEORV32 CPU. The processor is intended as *ready-to-go* auxiliary processor within a larger SoC

|

| 26 |

37 |

zero_gravi |

designs or as stand-alone custom microcontroller.

|

| 27 |

2 |

zero_gravi |

|

| 28 |

47 |

zero_gravi |

:label: The project’s change log is available in the [CHANGELOG.md](https://github.com/stnolting/neorv32/blob/master/CHANGELOG.md) file in the root directory of this repository.

|

| 29 |

40 |

zero_gravi |

To see the changes between releases visit the project's [release page](https://github.com/stnolting/neorv32/releases).

|

| 30 |

45 |

zero_gravi |

|

| 31 |

47 |

zero_gravi |

:books: The doxygen-based documentation of the software framework is available online at [GitHub-pages](https://stnolting.github.io/neorv32/files.html).

|

| 32 |

11 |

zero_gravi |

|

| 33 |

47 |

zero_gravi |

:page_facing_up: For more detailed information take a look at the [NEORV32 data sheet (pdf)](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf).

|

| 34 |

40 |

zero_gravi |

|

| 35 |

47 |

zero_gravi |

|

| 36 |

32 |

zero_gravi |

### Key Features

|

| 37 |

2 |

zero_gravi |

|

| 38 |

47 |

zero_gravi |

* RISC-V 32-bit `rv32i` [**NEORV32 CPU**](#NEORV32-CPU-Features), compliant to

|

| 39 |

49 |

zero_gravi |

* subset of the *Unprivileged ISA Specification* [(Version 2.2)](https://github.com/stnolting/neorv32/blob/master/docs/riscv-privileged.pdf)

|

| 40 |

|

|

* subset of the *Privileged Architecture Specification* [(Version 1.12-draft)](https://github.com/stnolting/neorv32/blob/master/docs/riscv-spec.pdf)

|

| 41 |

|

|

* the [offcial RISC-V compliance tests](#Status) (*passing*)

|

| 42 |

45 |

zero_gravi |

* Configurable RISC-V-compliant CPU extensions

|

| 43 |

47 |

zero_gravi |

* [`A`](#Atomic-memory-access-a-extension) - atomic memory access instructions (optional)

|

| 44 |

|

|

* [`B`](#Bit-manipulation-instructions-B-extension) - Bit manipulation instructions (optional)

|

| 45 |

|

|

* [`C`](#Compressed-instructions-C-extension) - compressed instructions (16-bit) (optional)

|

| 46 |

|

|

* [`E`](#Embedded-CPU-version-E-extension) - embedded CPU (reduced register file size) (optional)

|

| 47 |

|

|

* [`I`](#Integer-base-instruction-set-I-extension) - base integer instruction set (always enabled)

|

| 48 |

|

|

* [`M`](#Integer-multiplication-and-division-hardware-M-extension) - integer multiplication and division hardware (optional)

|

| 49 |

|

|

* [`U`](#Privileged-architecture---User-mode-U-extension) - less-privileged *user mode* (optional)

|

| 50 |

|

|

* [`X`](#NEORV32-specific-CPU-extensions-X-extension) - NEORV32-specific extensions (always enabled)

|

| 51 |

|

|

* [`Zicsr`](#Privileged-architecture---CSR-access-Zicsr-extension) - control and status register access instructions (+ exception/irq system) (optional)

|

| 52 |

|

|

* [`Zifencei`](#Privileged-architecture---Instruction-stream-synchronization-Zifencei-extension) - instruction stream synchronization (optional)

|

| 53 |

|

|

* [`PMP`](#Privileged-architecture---Physical-memory-protection-PMP) - physical memory protection (optional)

|

| 54 |

|

|

* [`HPM`](#Privileged-architecture---Hardware-performance-monitors-HPM-extension) - hardware performance monitors (optional)

|

| 55 |

39 |

zero_gravi |

* Full-scale RISC-V microcontroller system / **SoC** [**NEORV32 Processor**](#NEORV32-Processor-Features) with optional submodules

|

| 56 |

41 |

zero_gravi |

* optional embedded memories (instructions/data/bootloader, RAM/ROM) and caches

|

| 57 |

37 |

zero_gravi |

* timers (watch dog, RISC-V-compliant machine timer)

|

| 58 |

47 |

zero_gravi |

* serial interfaces (SPI, TWI, UART)

|

| 59 |

|

|

* general purpose IO and PWM channels

|

| 60 |

37 |

zero_gravi |

* external bus interface (Wishbone / [AXI4](#AXI4-Connectivity))

|

| 61 |

48 |

zero_gravi |

* subsystem for custom co-processors

|

| 62 |

37 |

zero_gravi |

* [more ...](#NEORV32-Processor-Features)

|

| 63 |

36 |

zero_gravi |

* Software framework

|

| 64 |

37 |

zero_gravi |

* core libraries for high-level usage of the provided functions and peripherals

|

| 65 |

|

|

* application compilation based on [GNU makefiles](https://github.com/stnolting/neorv32/blob/master/sw/example/blink_led/makefile)

|

| 66 |

46 |

zero_gravi |

* GCC-based toolchain ([pre-compiled toolchains available](https://github.com/stnolting/riscv-gcc-prebuilt))

|

| 67 |

45 |

zero_gravi |

* bootloader with UART interface console

|

| 68 |

36 |

zero_gravi |

* runtime environment

|

| 69 |

|

|

* several example programs

|

| 70 |

49 |

zero_gravi |

* [doxygen-based](https://github.com/stnolting/neorv32/blob/master/docs/doxygen_makefile_sw) software documentation: available on [GitHub pages](https://stnolting.github.io/neorv32/files.html)

|

| 71 |

36 |

zero_gravi |

* [FreeRTOS port](https://github.com/stnolting/neorv32/blob/master/sw/example/demo_freeRTOS) available

|

| 72 |

34 |

zero_gravi |

* [**Full-blown data sheet**](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf) (pdf)

|

| 73 |

32 |

zero_gravi |

* Completely described in behavioral, platform-independent VHDL - no primitives, macros, etc.

|

| 74 |

|

|

* Fully synchronous design, no latches, no gated clocks

|

| 75 |

|

|

* Small hardware footprint and high operating frequency

|

| 76 |

15 |

zero_gravi |

|

| 77 |

22 |

zero_gravi |

|

| 78 |

2 |

zero_gravi |

### Design Principles

|

| 79 |

|

|

|

| 80 |

39 |

zero_gravi |

* From zero to *hello_world*: Completely open source and documented.

|

| 81 |

2 |

zero_gravi |

* Plain VHDL without technology-specific parts like attributes, macros or primitives.

|

| 82 |

|

|

* Easy to use – working out of the box.

|

| 83 |

|

|

* Clean synchronous design, no wacky combinatorial interfaces.

|

| 84 |

23 |

zero_gravi |

* Be as small as possible – but with a reasonable size-performance tradeoff.

|

| 85 |

40 |

zero_gravi |

* Be as RISC-V-compliant as possible.

|

| 86 |

|

|

* The processor has to fit in a Lattice iCE40 UltraPlus 5k low-power FPGA running at 20+ MHz.

|

| 87 |

2 |

zero_gravi |

|

| 88 |

|

|

|

| 89 |

36 |

zero_gravi |

### Status

|

| 90 |

3 |

zero_gravi |

|

| 91 |

31 |

zero_gravi |

The processor is [synthesizable](#FPGA-Implementation-Results) (tested on *real hardware* using Intel Quartus Prime, Xilinx Vivado and Lattice Radiant/Synplify Pro) and can successfully execute

|

| 92 |

30 |

zero_gravi |

all the [provided example programs](https://github.com/stnolting/neorv32/tree/master/sw/example) including the [CoreMark benchmark](#CoreMark-Benchmark).

|

| 93 |

2 |

zero_gravi |

|

| 94 |

47 |

zero_gravi |

**RISC-V Compliance**: The processor passes the official `rv32_m/C`, `rv32_m/I`, `rv32_m/M`, `rv32_m/privilege` and `rv32_m/Zifencei`

|

| 95 |

|

|

[RISC-V compliance](https://github.com/riscv/riscv-compliance) tests. More information regarding the NEORV32 port of the compliance framework can be found in

|

| 96 |

|

|

[`riscv-compliance/README.md`](https://github.com/stnolting/neorv32/blob/master/riscv-compliance/README.md).

|

| 97 |

2 |

zero_gravi |

|

| 98 |

43 |

zero_gravi |

| Project component | CI status |

|

| 99 |

|

|

|:----------------- |:----------|

|

| 100 |

|

|

| [NEORV32 processor](https://github.com/stnolting/neorv32) | [](https://github.com/stnolting/neorv32/actions?query=workflow%3A%22Processor+Check%22) |

|

| 101 |

49 |

zero_gravi |

| [SW Framework Documentation (online @GH-pages)](https://stnolting.github.io/neorv32/files.html) | [](https://stnolting.github.io/neorv32/files.html) |

|

| 102 |

46 |

zero_gravi |

| [Pre-built toolchains](https://github.com/stnolting/riscv-gcc-prebuilt) | [](https://github.com/stnolting/riscv-gcc-prebuilt/actions?query=workflow%3A%22Test+Toolchains%22) |

|

| 103 |

43 |

zero_gravi |

| [RISC-V compliance test](https://github.com/stnolting/neorv32/blob/master/riscv-compliance/README.md) | [](https://github.com/stnolting/neorv32/actions?query=workflow%3A%22RISC-V+Compliance%22) |

|

| 104 |

6 |

zero_gravi |

|

| 105 |

|

|

|

| 106 |

43 |

zero_gravi |

|

| 107 |

39 |

zero_gravi |

### To-Do / Wish List / Help Wanted

|

| 108 |

7 |

zero_gravi |

|

| 109 |

35 |

zero_gravi |

* Use LaTeX for data sheet

|

| 110 |

44 |

zero_gravi |

* Further size and performance optimization

|

| 111 |

48 |

zero_gravi |

* Further expand associativity configuration of instruction cache (4x/8x set-associativity)?

|

| 112 |

|

|

* Add data cache?

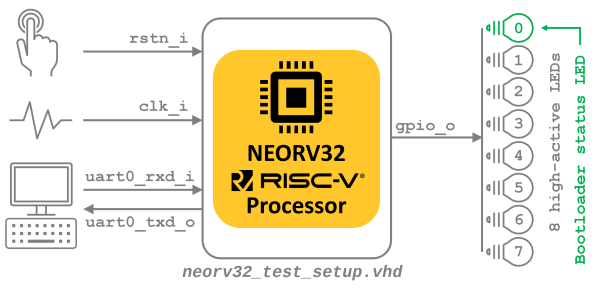

|

| 113 |

|

|

* Burst mode for the external memory/bus interface?

|

| 114 |

45 |

zero_gravi |

* RISC-V `F` (using [`Zfinx`](https://github.com/riscv/riscv-zfinx/blob/master/Zfinx_spec.adoc)?) CPU extension (single-precision floating point)

|

| 115 |

49 |

zero_gravi |

* Add template (HW module + SW intrinsics skeleton) for custom instructions?

|

| 116 |

|

|

* Implement further RISC-V CPU extensions?

|

| 117 |

48 |

zero_gravi |

* More support for FreeRTOS (like *all* traps)?

|

| 118 |

|

|

* Port additional RTOSs (like [Zephyr](https://github.com/zephyrproject-rtos/zephyr) or [RIOT](https://www.riot-os.org))?

|

| 119 |

|

|

* Add debugger ([RISC-V debug spec](https://github.com/riscv/riscv-debug-spec))?

|

| 120 |

|

|

* Add encryption/decryption/hash accelerator (maybe [XTEA](https://en.wikipedia.org/wiki/XTEA))?

|

| 121 |

36 |

zero_gravi |

* ...

|

| 122 |

40 |

zero_gravi |

* [Ideas?](#ContributeFeedbackQuestions)

|

| 123 |

7 |

zero_gravi |

|

| 124 |

|

|

|

| 125 |

36 |

zero_gravi |

|

| 126 |

2 |

zero_gravi |

## Features

|

| 127 |

|

|

|

| 128 |

34 |

zero_gravi |

The full-blown data sheet of the NEORV32 Processor and CPU is available as pdf file:

|

| 129 |

40 |

zero_gravi |

[:page_facing_up: NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf).

|

| 130 |

31 |

zero_gravi |

|

| 131 |

44 |

zero_gravi |

|

| 132 |

36 |

zero_gravi |

### NEORV32 Processor Features

|

| 133 |

2 |

zero_gravi |

|

| 134 |

11 |

zero_gravi |

|

| 135 |

|

|

|

| 136 |

23 |

zero_gravi |

The NEORV32 Processor provides a full-scale microcontroller-like SoC based on the NEORV32 CPU. The setup

|

| 137 |

37 |

zero_gravi |

is highly customizable via the processor's top generics and already provides the following *optional* modules:

|

| 138 |

2 |

zero_gravi |

|

| 139 |

41 |

zero_gravi |

* processor-internal data and instruction memories (**DMEM** / **IMEM**) & cache (**iCACHE**)

|

| 140 |

|

|

* bootloader (**BOOTLDROM**) with UART console and automatic application boot from SPI flash option

|

| 141 |

37 |

zero_gravi |

* machine system timer (**MTIME**), RISC-V-compliant

|

| 142 |

|

|

* watchdog timer (**WDT**)

|

| 143 |

|

|

* universal asynchronous receiver and transmitter (**UART**) with simulation output option via text.io

|

| 144 |

|

|

* 8/16/24/32-bit serial peripheral interface controller (**SPI**) with 8 dedicated chip select lines

|

| 145 |

|

|

* two wire serial interface controller (**TWI**), with optional clock-stretching, compatible to the I²C standard

|

| 146 |

|

|

* general purpose parallel IO port (**GPIO**), 32xOut & 32xIn, with pin-change interrupt

|

| 147 |

|

|

* 32-bit external bus interface, Wishbone b4 compliant (**WISHBONE**), *standard* or *pipelined* handshake/transactions mode

|

| 148 |

|

|

* wrapper for **AXI4-Lite Master Interface** (see [AXI Connectivity](#AXI4-Connectivity))

|

| 149 |

|

|

* PWM controller with 4 channels and 8-bit duty cycle resolution (**PWM**)

|

| 150 |

47 |

zero_gravi |

* ring-oscillator-based true random number generator (**TRNG**)

|

| 151 |

|

|

* custom functions subsystem (**CFS**) for tightly-coupled custom co-processor extensions

|

| 152 |

49 |

zero_gravi |

* numerically-controlled oscillator (**NCO**) with three independent channels

|

| 153 |

37 |

zero_gravi |

* system configuration information memory to check hardware configuration by software (**SYSINFO**, mandatory - not *optional*)

|

| 154 |

23 |

zero_gravi |

|

| 155 |

44 |

zero_gravi |

|

| 156 |

36 |

zero_gravi |

### NEORV32 CPU Features

|

| 157 |

2 |

zero_gravi |

|

| 158 |

40 |

zero_gravi |

The NEORV32 CPU is **compliant** to the

|

| 159 |

12 |

zero_gravi |

[official RISC-V specifications (2.2)](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/riscv-spec.pdf) including a subset of the

|

| 160 |

40 |

zero_gravi |

[RISC-V privileged architecture specifications (1.12-draft)](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/riscv-spec.pdf)

|

| 161 |

|

|

tested via the [official RISC-V Compliance Test Framework](https://github.com/riscv/riscv-compliance)

|

| 162 |

|

|

(see [`riscv-compliance/README`](https://github.com/stnolting/neorv32/blob/master/riscv-compliance/README.md)).

|

| 163 |

2 |

zero_gravi |

|

| 164 |

11 |

zero_gravi |

More information regarding the CPU including a detailed list of the instruction set and the available CSRs can be found in

|

| 165 |

40 |

zero_gravi |

the [:page_facing_up: NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf).

|

| 166 |

11 |

zero_gravi |

|

| 167 |

|

|

|

| 168 |

47 |

zero_gravi |

#### General Features

|

| 169 |

|

|

|

| 170 |

26 |

zero_gravi |

* Modified Harvard architecture (separate CPU interfaces for data and instructions; NEORV32 processor: Single processor-internal bus via I/D mux)

|

| 171 |

12 |

zero_gravi |

* Two stages in-order pipeline (FETCH, EXECUTE); each stage uses a multi-cycle processing scheme

|

| 172 |

15 |

zero_gravi |

* No hardware support of unaligned accesses - they will trigger an exception

|

| 173 |

40 |

zero_gravi |

* BIG-ENDIAN byte-order, processor's external memory interface allows endianness configuration to connect to system with different endianness

|

| 174 |

23 |

zero_gravi |

* All reserved or unimplemented instructions will raise an illegal instruction exception

|

| 175 |

15 |

zero_gravi |

* Privilege levels: `machine` mode, `user` mode (if enabled via `U` extension)

|

| 176 |

33 |

zero_gravi |

* Official [RISC-V open-source architecture ID](https://github.com/riscv/riscv-isa-manual/blob/master/marchid.md)

|

| 177 |

11 |

zero_gravi |

|

| 178 |

|

|

|

| 179 |

47 |

zero_gravi |

#### Atomic memory access (`A` extension)

|

| 180 |

2 |

zero_gravi |

|

| 181 |

47 |

zero_gravi |

* Supported instructions: `LR.W` (load-reservate) `SC.W` (store-conditional)

|

| 182 |

|

|

|

| 183 |

|

|

|

| 184 |

|

|

#### Bit manipulation instructions (`B` extension)

|

| 185 |

|

|

|

| 186 |

|

|

* :warning: Extension is not officially ratified yet by the RISC-V foundation!

|

| 187 |

|

|

* Implies `Zbb` extension (base bit manipulation instruction set)

|

| 188 |

|

|

* Compatible to [v0.94-draft](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/bitmanip-draft.pdf) of the bit manipulation spec

|

| 189 |

|

|

* Support via intrisc library (see [`sw/example/bit_manipulation`](https://github.com/stnolting/neorv32/tree/master/sw/example/bit_manipulation))

|

| 190 |

|

|

* Only the `Zbb` base instructions subset is supported yet

|

| 191 |

|

|

* Supported instructions: `CLZ` `CTZ` `CPOP` `SEXT.B` `SEXT.H` `MIN[U]` `MAX[U]` `ANDN` `ORN` `XNOR` `ROL` `ROR` `RORI` `zext`(*pseudo-instruction* for `PACK rd, rs, zero`) `rev8`(*pseudo-instruction* for `GREVI rd, rs, -8`) `orc.b`(*pseudo-instruction* for `GORCI rd, rs, 7`)

|

| 192 |

|

|

|

| 193 |

|

|

|

| 194 |

|

|

#### Compressed instructions (`C` extension)

|

| 195 |

|

|

|

| 196 |

2 |

zero_gravi |

* ALU instructions: `C.ADDI4SPN` `C.ADDI` `C.ADD` `C.ADDI16SP` `C.LI` `C.LUI` `C.SLLI` `C.SRLI` `C.SRAI` `C.ANDI` `C.SUB` `C.XOR` `C.OR` `C.AND` `C.MV` `C.NOP`

|

| 197 |

7 |

zero_gravi |

* Jump and branch instructions: `C.J` `C.JAL` `C.JR` `C.JALR` `C.BEQZ` `C.BNEZ`

|

| 198 |

2 |

zero_gravi |

* Memory instructions: `C.LW` `C.SW` `C.LWSP` `C.SWSP`

|

| 199 |

25 |

zero_gravi |

* System instructions: `C.EBREAK` (only with `Zicsr` extension)

|

| 200 |

40 |

zero_gravi |

* Pseudo-instructions are not listed

|

| 201 |

2 |

zero_gravi |

|

| 202 |

47 |

zero_gravi |

#### Embedded CPU version (`E` extension)

|

| 203 |

|

|

|

| 204 |

2 |

zero_gravi |

* Reduced register file (only the 16 lowest registers)

|

| 205 |

|

|

|

| 206 |

47 |

zero_gravi |

|

| 207 |

|

|

#### Integer base instruction set (`I` extension)

|

| 208 |

|

|

|

| 209 |

|

|

* ALU instructions: `LUI` `AUIPC` `ADDI` `SLTI` `SLTIU` `XORI` `ORI` `ANDI` `SLLI` `SRLI` `SRAI` `ADD` `SUB` `SLL` `SLT` `SLTU` `XOR` `SRL` `SRA` `OR` `AND`

|

| 210 |

|

|

* Jump and branch instructions: `JAL` `JALR` `BEQ` `BNE` `BLT` `BGE` `BLTU` `BGEU`

|

| 211 |

|

|

* Memory instructions: `LB` `LH` `LW` `LBU` `LHU` `SB` `SH` `SW`

|

| 212 |

|

|

* System instructions: `ECALL` `EBREAK` `FENCE`

|

| 213 |

|

|

* Pseudo-instructions are not listed

|

| 214 |

|

|

|

| 215 |

|

|

|

| 216 |

|

|

#### Integer multiplication and division hardware (`M` extension)

|

| 217 |

|

|

|

| 218 |

2 |

zero_gravi |

* Multiplication instructions: `MUL` `MULH` `MULHSU` `MULHU`

|

| 219 |

|

|

* Division instructions: `DIV` `DIVU` `REM` `REMU`

|

| 220 |

19 |

zero_gravi |

* By default, the multiplier and divider cores use an iterative bit-serial processing scheme

|

| 221 |

|

|

* Multiplications can be mapped to DSPs via the `FAST_MUL_EN` generic to increase performance

|

| 222 |

2 |

zero_gravi |

|

| 223 |

39 |

zero_gravi |

|

| 224 |

47 |

zero_gravi |

#### Privileged architecture - User mode (`U` extension)

|

| 225 |

44 |

zero_gravi |

|

| 226 |

47 |

zero_gravi |

* Requires `Zicsr` extension

|

| 227 |

|

|

* Privilege levels: `M` (machine mode) + less-privileged `U` (user mode)

|

| 228 |

|

|

|

| 229 |

|

|

|

| 230 |

|

|

#### NEORV32-specific CPU extensions (`X` extension)

|

| 231 |

|

|

|

| 232 |

|

|

* The NEORV32-specific extensions are always enabled and are indicated via the `X` bit set in the `misa` CSR.

|

| 233 |

48 |

zero_gravi |

* 16 *fast interrupt* request channels with according control/status bits in `mie` and `mip` and custom exception codes in `mcause`

|

| 234 |

47 |

zero_gravi |

* `mzext` CSR to check for implemented `Z*` CPU extensions (like `Zifencei`)

|

| 235 |

|

|

* All undefined/umimplemented/malformed/illegal instructions do raise an illegal instruction exception

|

| 236 |

|

|

|

| 237 |

|

|

|

| 238 |

|

|

#### Privileged architecture - CSR access (`Zicsr` extension)

|

| 239 |

|

|

|

| 240 |

2 |

zero_gravi |

* Privilege levels: `M-mode` (Machine mode)

|

| 241 |

|

|

* CSR access instructions: `CSRRW` `CSRRS` `CSRRC` `CSRRWI` `CSRRSI` `CSRRCI`

|

| 242 |

8 |

zero_gravi |

* System instructions: `MRET` `WFI`

|

| 243 |

40 |

zero_gravi |

* Pseudo-instructions are not listed

|

| 244 |

42 |

zero_gravi |

* Counter CSRs: `[m]cycle[h]` `[m]instret[m]` `time[h]` `[m]hpmcounter*[h]`(3..31, configurable) `mcounteren` `mcountinhibit` `mhpmevent*`(3..31, configurable)

|

| 245 |

|

|

* Machine CSRs: `mstatus[h]` `misa`(read-only!) `mie` `mtvec` `mscratch` `mepc` `mcause` `mtval` `mip` `mvendorid` [`marchid`](https://github.com/riscv/riscv-isa-manual/blob/master/marchid.md) `mimpid` `mhartid` `mzext`(custom)

|

| 246 |

2 |

zero_gravi |

* Supported exceptions and interrupts:

|

| 247 |

|

|

* Misaligned instruction address

|

| 248 |

38 |

zero_gravi |

* Instruction access fault (via unacknowledged bus access after timeout)

|

| 249 |

2 |

zero_gravi |

* Illegal instruction

|

| 250 |

4 |

zero_gravi |

* Breakpoint (via `ebreak` instruction)

|

| 251 |

2 |

zero_gravi |

* Load address misaligned

|

| 252 |

38 |

zero_gravi |

* Load access fault (via unacknowledged bus access after timeout)

|

| 253 |

4 |

zero_gravi |

* Store address misaligned

|

| 254 |

38 |

zero_gravi |

* Store access fault (via unacknowledged bus access after timeout)

|

| 255 |

40 |

zero_gravi |

* Environment call from U-mode (via `ecall` instruction in user mode)

|

| 256 |

|

|

* Environment call from M-mode (via `ecall` instruction in machine mode)

|

| 257 |

|

|

* Machine timer interrupt `mti` (via processor's MTIME unit / external signal)

|

| 258 |

15 |

zero_gravi |

* Machine software interrupt `msi` (via external signal)

|

| 259 |

|

|

* Machine external interrupt `mei` (via external signal)

|

| 260 |

47 |

zero_gravi |

* Eight fast interrupt requests (custom extension)

|

| 261 |

2 |

zero_gravi |

|

| 262 |

15 |

zero_gravi |

|

| 263 |

47 |

zero_gravi |

#### Privileged architecture - Instruction stream synchronization (`Zifencei` extension)

|

| 264 |

|

|

|

| 265 |

41 |

zero_gravi |

* System instructions: `FENCE.I` (among others, used to clear and reload instruction cache)

|

| 266 |

8 |

zero_gravi |

|

| 267 |

47 |

zero_gravi |

|

| 268 |

|

|

#### Privileged architecture - Physical memory protection (`PMP`)

|

| 269 |

|

|

|

| 270 |

|

|

* Requires `Zicsr` extension

|

| 271 |

44 |

zero_gravi |

* Configurable number of regions (0..63)

|

| 272 |

42 |

zero_gravi |

* Additional machine CSRs: `pmpcfg*`(0..15) `pmpaddr*`(0..63)

|

| 273 |

2 |

zero_gravi |

|

| 274 |

47 |

zero_gravi |

|

| 275 |

|

|

#### Privileged architecture - Hardware performance monitors (`HPM` extension)

|

| 276 |

|

|

|

| 277 |

|

|

* Requires `Zicsr` extension

|

| 278 |

44 |

zero_gravi |

* Configurable number of counters (0..29)

|

| 279 |

|

|

* Additional machine CSRs: `mhpmevent*`(3..31) `[m]hpmcounter*[h]`(3..31)

|

| 280 |

15 |

zero_gravi |

|

| 281 |

23 |

zero_gravi |

|

| 282 |

44 |

zero_gravi |

### :warning: Non-RISC-V-Compliant Issues and Limitations

|

| 283 |

|

|

|

| 284 |

40 |

zero_gravi |

* CPU and Processor are BIG-ENDIAN, but this should be no problem as the external memory bus interface provides big- and little-endian configurations

|

| 285 |

30 |

zero_gravi |

* `misa` CSR is read-only - no dynamic enabling/disabling of synthesized CPU extensions during runtime; for compatibility: write accesses (in m-mode) are ignored and do not cause an exception

|

| 286 |

42 |

zero_gravi |

* The physical memory protection (**PMP**) only supports `NAPOT` mode yet and a minimal granularity of 8 bytes

|

| 287 |

39 |

zero_gravi |

* The `A` extension only implements `lr.w` and `sc.w` instructions yet. However, these instructions are sufficient to emulate all further AMO operations

|

| 288 |

44 |

zero_gravi |

* The `mcause` trap code `0x80000000` (originally reserved in the RISC-V specs) is used to indicate a hardware reset (as "non-maskable interrupt")

|

| 289 |

|

|

* The bit manipulation extension is not yet officially ratified, but is expected to stay unchanged. There is no software support in the upstream GCC RISC-V port yet. However, an intrinsic library is provided to utilize the provided bit manipulation extension from C-language code (see [`sw/example/bit_manipulation`](https://github.com/stnolting/neorv32/tree/master/sw/example/bit_manipulation)). NEORV32's `B`/`Zbb` extension is compliant to spec. version "0.94-draft".

|

| 290 |

23 |

zero_gravi |

|

| 291 |

|

|

|

| 292 |

|

|

|

| 293 |

2 |

zero_gravi |

## FPGA Implementation Results

|

| 294 |

|

|

|

| 295 |

23 |

zero_gravi |

### NEORV32 CPU

|

| 296 |

|

|

|

| 297 |

|

|

This chapter shows exemplary implementation results of the NEORV32 CPU for an **Intel Cyclone IV EP4CE22F17C6N FPGA** on

|

| 298 |

37 |

zero_gravi |

a DE0-nano board. The design was synthesized using **Intel Quartus Prime Lite 20.1** ("balanced implementation"). The timing

|

| 299 |

4 |

zero_gravi |

information is derived from the Timing Analyzer / Slow 1200mV 0C Model. If not otherwise specified, the default configuration

|

| 300 |

42 |

zero_gravi |

of the CPU's generics is assumed (e.g. no physical memory protection, no hardware performance monitors).

|

| 301 |

49 |

zero_gravi |

No constraints were used at all.

|

| 302 |

2 |

zero_gravi |

|

| 303 |

49 |

zero_gravi |

Results generated for hardware version [`1.5.1.4`](https://github.com/stnolting/neorv32/blob/master/CHANGELOG.md).

|

| 304 |

2 |

zero_gravi |

|

| 305 |

44 |

zero_gravi |

| CPU Configuration | LEs | FFs | Memory bits | DSPs | f_max |

|

| 306 |

|

|

|:-----------------------------------------|:----------:|:--------:|:-----------:|:----:|:-------:|

|

| 307 |

49 |

zero_gravi |

| `rv32i` | 979 | 409 | 1024 | 0 | 123 MHz |

|

| 308 |

|

|

| `rv32i` + `Zicsr` | 1789 | 847 | 1024 | 0 | 122 MHz |

|

| 309 |

|

|

| `rv32im` + `Zicsr` | 2381 | 1125 | 1024 | 0 | 122 MHz |

|

| 310 |

|

|

| `rv32imc` + `Zicsr` | 2608 | 1140 | 1024 | 0 | 122 MHz |

|

| 311 |

|

|

| `rv32imac` + `Zicsr` | 2621 | 1144 | 1024 | 0 | 122 MHz |

|

| 312 |

|

|

| `rv32imacb` + `Zicsr` | 3013 | 1310 | 1024 | 0 | 122 MHz |

|

| 313 |

|

|

| `rv32imacb` + `Zicsr` + `u` | 3031 | 1313 | 1024 | 0 | 122 MHz |

|

| 314 |

|

|

| `rv32imacb` + `Zicsr` + `u` + `Zifencei` | 3050 | 1313 | 1024 | 0 | 116 MHz |

|

| 315 |

2 |

zero_gravi |

|

| 316 |

49 |

zero_gravi |

Setups with enabled "embedded CPU extension" `E` show the same LUT and FF utilization and identical f_max as the according `I` configuration.

|

| 317 |

|

|

However, the size of the register file is cut in half.

|

| 318 |

2 |

zero_gravi |

|

| 319 |

39 |

zero_gravi |

|

| 320 |

23 |

zero_gravi |

### NEORV32 Processor-Internal Peripherals and Memories

|

| 321 |

|

|

|

| 322 |

49 |

zero_gravi |

Results generated for hardware version [`1.5.1.4`](https://github.com/stnolting/neorv32/blob/master/CHANGELOG.md).

|

| 323 |

11 |

zero_gravi |

|

| 324 |

25 |

zero_gravi |

| Module | Description | LEs | FFs | Memory bits | DSPs |

|

| 325 |

31 |

zero_gravi |

|:----------|:-----------------------------------------------------|----:|----:|------------:|-----:|

|

| 326 |

37 |

zero_gravi |

| BOOT ROM | Bootloader ROM (default 4kB) | 3 | 1 | 32 768 | 0 |

|

| 327 |

49 |

zero_gravi |

| BUSSWITCH | Bus mux for CPU instr. & data interfaces | 65 | 8 | 0 | 0 |

|

| 328 |

45 |

zero_gravi |

| i-CACHE | Proc.-int. nstruction cache (default 1x4x64 bytes) | 234 | 156 | 8 192 | 0 |

|

| 329 |

47 |

zero_gravi |

| CFS | Custom functions subsystem | - | - | - | - |

|

| 330 |

39 |

zero_gravi |

| DMEM | Processor-internal data memory (default 8kB) | 6 | 2 | 65 536 | 0 |

|

| 331 |

40 |

zero_gravi |

| GPIO | General purpose input/output ports | 67 | 65 | 0 | 0 |

|

| 332 |

39 |

zero_gravi |

| IMEM | Processor-internal instruction memory (default 16kb) | 6 | 2 | 131 072 | 0 |

|

| 333 |

40 |

zero_gravi |

| MTIME | Machine system timer | 274 | 166 | 0 | 0 |

|

| 334 |

49 |

zero_gravi |

| NCO | Numerically-controlled oscillator | 254 | 226 | 0 | 0 |

|

| 335 |

39 |

zero_gravi |

| PWM | Pulse-width modulation controller | 71 | 69 | 0 | 0 |

|

| 336 |

40 |

zero_gravi |

| SPI | Serial peripheral interface | 138 | 124 | 0 | 0 |

|

| 337 |

|

|

| SYSINFO | System configuration information memory | 11 | 10 | 0 | 0 |

|

| 338 |

31 |

zero_gravi |

| TRNG | True random number generator | 132 | 105 | 0 | 0 |

|

| 339 |

40 |

zero_gravi |

| TWI | Two-wire interface | 77 | 46 | 0 | 0 |

|

| 340 |

|

|

| UART | Universal asynchronous receiver/transmitter | 176 | 132 | 0 | 0 |

|

| 341 |

|

|

| WDT | Watchdog timer | 60 | 45 | 0 | 0 |

|

| 342 |

39 |

zero_gravi |

| WISHBONE | External memory interface | 129 | 104 | 0 | 0 |

|

| 343 |

2 |

zero_gravi |

|

| 344 |

|

|

|

| 345 |

23 |

zero_gravi |

### NEORV32 Processor - Exemplary FPGA Setups

|

| 346 |

6 |

zero_gravi |

|

| 347 |

47 |

zero_gravi |

Exemplary processor implementation results for different FPGA platforms. The processor setup uses *the default peripheral configuration* (like no _CFS_ and no _TRNG_),

|

| 348 |

23 |

zero_gravi |

no external memory interface and only internal instruction and data memories. IMEM uses 16kB and DMEM uses 8kB memory space. The setup's top entity connects most of the

|

| 349 |

11 |

zero_gravi |

processor's [top entity](https://github.com/stnolting/neorv32/blob/master/rtl/core/neorv32_top.vhd) signals

|

| 350 |

40 |

zero_gravi |

to FPGA pins - except for the Wishbone bus and the interrupt signals. The "default" strategy of each toolchain is used.

|

| 351 |

6 |

zero_gravi |

|

| 352 |

40 |

zero_gravi |

Results generated for hardware version [`1.4.9.0`](https://github.com/stnolting/neorv32/blob/master/CHANGELOG.md).

|

| 353 |

6 |

zero_gravi |

|

| 354 |

40 |

zero_gravi |

| Vendor | FPGA | Board | Toolchain | CPU Configuration | LUT / LE | FF / REG | DSP | Memory Bits | BRAM / EBR | SPRAM | Frequency |

|

| 355 |

|

|

|:--------|:----------------------------------|:-----------------|:---------------------------|:-----------------------------------------------|:-----------|:-----------|:-------|:-------------|:-----------|:---------|--------------:|

|

| 356 |

|

|

| Intel | Cyclone IV `EP4CE22F17C6N` | Terasic DE0-Nano | Quartus Prime Lite 20.1 | `rv32imc` + `u` + `Zicsr` + `Zifencei` | 3813 (17%) | 1904 (8%) | 0 (0%) | 231424 (38%) | - | - | 119 MHz |

|

| 357 |

|

|

| Lattice | iCE40 UltraPlus `iCE40UP5K-SG48I` | Upduino v2.0 | Radiant 2.1 (Synplify Pro) | `rv32ic` + `u` + `Zicsr` + `Zifencei` | 4397 (83%) | 1679 (31%) | 0 (0%) | - | 12 (40%) | 4 (100%) | *c* 22.15 MHz |

|

| 358 |

|

|

| Xilinx | Artix-7 `XC7A35TICSG324-1L` | Arty A7-35T | Vivado 2019.2 | `rv32imc` + `u` + `Zicsr` + `Zifencei` + `PMP` | 2465 (12%) | 1912 (5%) | 0 (0%) | - | 8 (16%) | - | *c* 100 MHz |

|

| 359 |

2 |

zero_gravi |

|

| 360 |

23 |

zero_gravi |

**_Notes_**

|

| 361 |

20 |

zero_gravi |

* The Lattice iCE40 UltraPlus setup uses the FPGA's SPRAM memory primitives for the internal IMEM and DMEM (each 64kb).

|

| 362 |

12 |

zero_gravi |

The FPGA-specific memory components can be found in [`rtl/fpga_specific`](https://github.com/stnolting/neorv32/blob/master/rtl/fpga_specific/lattice_ice40up).

|

| 363 |

|

|

* The clock frequencies marked with a "c" are constrained clocks. The remaining ones are _f_max_ results from the place and route timing reports.

|

| 364 |

11 |

zero_gravi |

* The Upduino and the Arty board have on-board SPI flash memories for storing the FPGA configuration. These device can also be used by the default NEORV32

|

| 365 |

|

|

bootloader to store and automatically boot an application program after reset (both tested successfully).

|

| 366 |

40 |

zero_gravi |

* The setups with `PMP` implement 2 regions with a minimal granularity of 64kB.

|

| 367 |

42 |

zero_gravi |

* No HPM counters are implemented.

|

| 368 |

2 |

zero_gravi |

|

| 369 |

22 |

zero_gravi |

|

| 370 |

|

|

|

| 371 |

2 |

zero_gravi |

## Performance

|

| 372 |

|

|

|

| 373 |

|

|

### CoreMark Benchmark

|

| 374 |

|

|

|

| 375 |

|

|

The [CoreMark CPU benchmark](https://www.eembc.org/coremark) was executed on the NEORV32 and is available in the

|

| 376 |

|

|

[sw/example/coremark](https://github.com/stnolting/neorv32/blob/master/sw/example/coremark) project folder. This benchmark

|

| 377 |

|

|

tests the capabilities of a CPU itself rather than the functions provided by the whole system / SoC.

|

| 378 |

|

|

|

| 379 |

|

|

~~~

|

| 380 |

|

|

**Configuration**

|

| 381 |

45 |

zero_gravi |

Hardware: 32kB IMEM, 16kB DMEM, no caches, 100MHz clock

|

| 382 |

38 |

zero_gravi |

CoreMark: 2000 iterations, MEM_METHOD is MEM_STACK

|

| 383 |

|

|

Compiler: RISCV32-GCC 10.1.0 (rv32i toolchain)

|

| 384 |

|

|

Compiler flags: default, see makefile

|

| 385 |

|

|

Peripherals: UART for printing the results

|

| 386 |

2 |

zero_gravi |

~~~

|

| 387 |

|

|

|

| 388 |

42 |

zero_gravi |

Results generated for hardware version [`1.4.9.8`](https://github.com/stnolting/neorv32/blob/master/CHANGELOG.md).

|

| 389 |

|

|

|

| 390 |

|

|

| CPU (including `Zicsr`) | Executable Size | Optimization | CoreMark Score | CoreMarks/MHz |

|

| 391 |

34 |

zero_gravi |

|:--------------------------------------------|:---------------:|:------------:|:--------------:|:-------------:|

|

| 392 |

42 |

zero_gravi |

| `rv32i` | 28 756 bytes | `-O3` | 36.36 | **0.3636** |

|

| 393 |

|

|

| `rv32im` | 27 516 bytes | `-O3` | 68.97 | **0.6897** |

|

| 394 |

|

|

| `rv32imc` | 22 008 bytes | `-O3` | 68.97 | **0.6897** |

|

| 395 |

|

|

| `rv32imc` + `FAST_MUL_EN` | 22 008 bytes | `-O3` | 86.96 | **0.8696** |

|

| 396 |

|

|

| `rv32imc` + `FAST_MUL_EN` + `FAST_SHIFT_EN` | 22 008 bytes | `-O3` | 90.91 | **0.9091** |

|

| 397 |

2 |

zero_gravi |

|

| 398 |

34 |

zero_gravi |

The `FAST_MUL_EN` configuration uses DSPs for the multiplier of the `M` extension (enabled via the `FAST_MUL_EN` generic). The `FAST_SHIFT_EN` configuration

|

| 399 |

|

|

uses a barrel shifter for CPU shift operations (enabled via the `FAST_SHIFT_EN` generic).

|

| 400 |

2 |

zero_gravi |

|

| 401 |

31 |

zero_gravi |

When the `C` extension is enabled, branches to an unaligned uncompressed instruction require additional instruction fetch cycles.

|

| 402 |

22 |

zero_gravi |

|

| 403 |

34 |

zero_gravi |

|

| 404 |

2 |

zero_gravi |

### Instruction Cycles

|

| 405 |

|

|

|

| 406 |

11 |

zero_gravi |

The NEORV32 CPU is based on a two-stages pipelined architecutre. Each stage uses a multi-cycle processing scheme. Hence,

|

| 407 |

9 |

zero_gravi |

each instruction requires several clock cycles to execute (2 cycles for ALU operations, ..., 40 cycles for divisions).

|

| 408 |

|

|

The average CPI (cycles per instruction) depends on the instruction mix of a specific applications and also on the available

|

| 409 |

42 |

zero_gravi |

CPU extensions. *By default* the CPU-internal shifter (e.g. for the `SLL` instruction) as well as the multiplier and divider of the

|

| 410 |

2 |

zero_gravi |

`M` extension use a bit-serial approach and require several cycles for completion.

|

| 411 |

|

|

|

| 412 |

6 |

zero_gravi |

The following table shows the performance results for successfully running 2000 CoreMark

|

| 413 |

9 |

zero_gravi |

iterations, which reflects a pretty good "real-life" work load. The average CPI is computed by

|

| 414 |

12 |

zero_gravi |

dividing the total number of required clock cycles (only the timed core to avoid distortion due to IO wait cycles; sampled via the `cycle[h]` CSRs)

|

| 415 |

19 |

zero_gravi |

by the number of executed instructions (`instret[h]` CSRs). The executables were generated using optimization `-O3`.

|

| 416 |

2 |

zero_gravi |

|

| 417 |

42 |

zero_gravi |

Results generated for hardware version [`1.4.9.8`](https://github.com/stnolting/neorv32/blob/master/CHANGELOG.md).

|

| 418 |

2 |

zero_gravi |

|

| 419 |

42 |

zero_gravi |

| CPU (including `Zicsr`) | Required Clock Cycles | Executed Instructions | Average CPI |

|

| 420 |

34 |

zero_gravi |

|:--------------------------------------------|----------------------:|----------------------:|:-----------:|

|

| 421 |

42 |

zero_gravi |

| `rv32i` | 5 595 750 503 | 1 466 028 607 | **3.82** |

|

| 422 |

|

|

| `rv32im` | 2 966 086 503 | 598 651 143 | **4.95** |

|

| 423 |

|

|

| `rv32imc` | 2 981 786 734 | 611 814 918 | **4.87** |

|

| 424 |

|

|

| `rv32imc` + `FAST_MUL_EN` | 2 399 234 734 | 611 814 918 | **3.92** |

|

| 425 |

|

|

| `rv32imc` + `FAST_MUL_EN` + `FAST_SHIFT_EN` | 2 265 135 174 | 611 814 948 | **3.70** |

|

| 426 |

2 |

zero_gravi |

|

| 427 |

34 |

zero_gravi |

The `FAST_MUL_EN` configuration uses DSPs for the multiplier of the `M` extension (enabled via the `FAST_MUL_EN` generic). The `FAST_SHIFT_EN` configuration

|

| 428 |

|

|

uses a barrel shifter for CPU shift operations (enabled via the `FAST_SHIFT_EN` generic).

|

| 429 |

|

|

|

| 430 |

36 |

zero_gravi |

When the `C` extension is enabled branches to an unaligned uncompressed instruction require additional instruction fetch cycles.

|

| 431 |

12 |

zero_gravi |

|

| 432 |

22 |

zero_gravi |

|

| 433 |

31 |

zero_gravi |

|

| 434 |

14 |

zero_gravi |

## Top Entities

|

| 435 |

2 |

zero_gravi |

|

| 436 |

36 |

zero_gravi |

The top entity of the **NEORV32 Processor** (SoC) is [`rtl/core/neorv32_top.vhd`](https://github.com/stnolting/neorv32/blob/master/rtl/core/neorv32_top.vhd).

|

| 437 |

2 |

zero_gravi |

|

| 438 |

36 |

zero_gravi |

All signals of the top entity are of type *std_ulogic* or *std_ulogic_vector*, respectively

|

| 439 |

34 |

zero_gravi |

(except for the processor's TWI signals, which are of type *std_logic*). Leave all unused output ports unconnected (`open`) and tie all unused

|

| 440 |

|

|

input ports to zero (`'0'` or `(others => '0')`, respectively).

|

| 441 |

14 |

zero_gravi |

|

| 442 |

36 |

zero_gravi |

Use the top's generics to configure the system according to your needs. Each generic is initilized with the default configuration.

|

| 443 |

34 |

zero_gravi |

Detailed information regarding the interface signals and configuration generics can be found in

|

| 444 |

40 |

zero_gravi |

the [:page_facing_up: NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf) (pdf).

|

| 445 |

22 |

zero_gravi |

|

| 446 |

23 |

zero_gravi |

|

| 447 |

36 |

zero_gravi |

### Using the CPU in Stand-Alone Mode

|

| 448 |

23 |

zero_gravi |

|

| 449 |

47 |

zero_gravi |

If you *do not* want to use the NEORV32 processor setup, you can also use the CPU in stand-alone mode and build your own system around it.

|

| 450 |

36 |

zero_gravi |

The top entity of the stand-alone **NEORV32 CPU** is [`rtl/core/neorv32_cpu.vhd`](https://github.com/stnolting/neorv32/blob/master/rtl/core/neorv32_cpu.vhd).

|

| 451 |

|

|

Note that the CPU uses a proprietary interface for accessing data and instruction memory. More information can be found in the

|

| 452 |

40 |

zero_gravi |

[:page_facing_up: NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf).

|

| 453 |

14 |

zero_gravi |

|

| 454 |

47 |

zero_gravi |

:information_source: It is recommended to use the processor setup even if you only want to use the CPU. Simply disable all the processor-internal modules via the generics

|

| 455 |

|

|

and you will get a "CPU wrapper" that already provides a minimal CPU environment and an external memory interface (like AXI4). This setup also allows to further use the default

|

| 456 |

|

|

bootloader and software framework. From this base you can start building your own processor system.

|

| 457 |

2 |

zero_gravi |

|

| 458 |

36 |

zero_gravi |

|

| 459 |

|

|

### Alternative Top Entities

|

| 460 |

|

|

|

| 461 |

|

|

*Alternative top entities*, like the simplified ["hello world" test setup](#Create-a-new-Hardware-Project) or CPU/Processor

|

| 462 |

|

|

wrappers with resolved port signal types (i.e. *std_logic*), can be found in [`rtl/top_templates`](https://github.com/stnolting/neorv32/blob/master/rtl/top_templates).

|

| 463 |

|

|

|

| 464 |

|

|

|

| 465 |

35 |

zero_gravi |

### AXI4 Connectivity

|

| 466 |

22 |

zero_gravi |

|

| 467 |

35 |

zero_gravi |

Via the [`rtl/top_templates/neorv32_top_axi4lite.vhd`](https://github.com/stnolting/neorv32/blob/master/rtl/top_templates/neorv32_top_axi4lite.vhd)

|

| 468 |

|

|

wrapper the NEORV32 provides an **AXI4-Lite** compatible master interface. This wrapper instantiates the default

|

| 469 |

|

|

[NEORV32 processor top entitiy](https://github.com/stnolting/neorv32/blob/master/rtl/core/neorv32_top.vhd) and implements a Wishbone to AXI4-Lite bridge.

|

| 470 |

2 |

zero_gravi |

|

| 471 |

35 |

zero_gravi |

The AXI4-Lite interface has been tested using Xilinx Vivado 19.2 block designer:

|

| 472 |

|

|

|

| 473 |

|

|

|

| 474 |

|

|

|

| 475 |

|

|

The processor was packed as custom IP using `neorv32_top_axi4lite.vhd` as top entity. The AXI interface is automatically detected by the packager.

|

| 476 |

|

|

All remaining IO interfaces are available as custom signals. The configuration generics are available via the "customize IP" dialog.

|

| 477 |

|

|

In the figure above the resulting IP block is named "neorv32_top_axi4lite_v1_0".

|

| 478 |

|

|

*(Note: Use Syntheiss option "global" when generating the block design to maintain the internal TWI tri-state drivers.)*

|

| 479 |

|

|

|

| 480 |

|

|

The setup uses an AXI interconnect to attach two block RAMs to the processor. Since the processor in this example is configured *without* IMEM and DMEM,

|

| 481 |

|

|

the attached block RAMs are used for storing instructions and data: the first RAM is used as instruction memory

|

| 482 |

|

|

and is mapped to address `0x00000000 - 0x00003fff` (16kB), the second RAM is used as data memory and is mapped to address `0x80000000 - 0x80001fff` (8kB).

|

| 483 |

|

|

|

| 484 |

|

|

|

| 485 |

|

|

|

| 486 |

2 |

zero_gravi |

## Getting Started

|

| 487 |

|

|

|

| 488 |

|

|

This overview is just a short excerpt from the *Let's Get It Started* section of the NEORV32 documentary:

|

| 489 |

|

|

|

| 490 |

40 |

zero_gravi |

[:page_facing_up: NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf)

|

| 491 |

2 |

zero_gravi |

|

| 492 |

|

|

|

| 493 |

14 |

zero_gravi |

### Toolchain

|

| 494 |

2 |

zero_gravi |

|

| 495 |

|

|

At first you need the **RISC-V GCC toolchain**. You can either [download the sources](https://github.com/riscv/riscv-gnu-toolchain)

|

| 496 |

|

|

and build the toolchain by yourself, or you can download a prebuilt one and install it.

|

| 497 |

|

|

|

| 498 |

23 |

zero_gravi |

To build the toolchain by yourself, follow the official [build instructions](https://github.com/riscv/riscv-gnu-toolchain).

|

| 499 |

14 |

zero_gravi |

Make sure to use the `ilp32` or `ilp32e` ABI.

|

| 500 |

2 |

zero_gravi |

|

| 501 |

15 |

zero_gravi |

**Alternatively**, you can download a prebuilt toolchain. I have uploaded the toolchains I am using to GitHub. These toolchains

|

| 502 |

40 |

zero_gravi |

were compiled on a 64-bit x86 Ubuntu 20.04 LTS (Ubuntu on Windows, actually). Download the toolchain of choice:

|

| 503 |

46 |

zero_gravi |

[:octocat: github.com/stnolting/riscv-gcc-prebuilt](https://github.com/stnolting/riscv-gcc-prebuilt)

|

| 504 |

2 |

zero_gravi |

|

| 505 |

45 |

zero_gravi |

You can also use the toolchains provided by [SiFive](https://github.com/sifive/freedom-tools/releases). These are 64-bit toolchains that can also emit 32-bit

|

| 506 |

|

|

RISC-V code. They were compiled for more sophisticated machines (`imac`) so the according hardware extensions are *mandatory*

|

| 507 |

2 |

zero_gravi |

|

| 508 |

45 |

zero_gravi |

:warning: Keep in mind that – for instance – a `rv32imc` toolchain only provides library code compiled with compressed and

|

| 509 |

|

|

`mul`/`div` instructions! Hence, this code cannot be executed (without emulation) on an architecture without these extensions!

|

| 510 |

|

|

|

| 511 |

|

|

|

| 512 |

22 |

zero_gravi |

### Dowload the NEORV32 Project

|

| 513 |

2 |

zero_gravi |

|

| 514 |

23 |

zero_gravi |

Get the sources of the NEORV32 Processor project. The simplest way is using `git clone` (suggested for easy project updates via `git pull`):

|

| 515 |

12 |

zero_gravi |

|

| 516 |

2 |

zero_gravi |

$ git clone https://github.com/stnolting/neorv32.git

|

| 517 |

|

|

|

| 518 |

23 |

zero_gravi |

Alternatively, you can either download a specific [release](https://github.com/stnolting/neorv32/releases) or get the most recent version

|

| 519 |

|

|

of this project as [`*.zip` file](https://github.com/stnolting/neorv32/archive/master.zip).

|

| 520 |

2 |

zero_gravi |

|

| 521 |

22 |

zero_gravi |

|

| 522 |

|

|

### Create a new Hardware Project

|

| 523 |

|

|

|

| 524 |

23 |

zero_gravi |

Create a new project with your FPGA design tool of choice. Add all the `*.vhd` files from the [`rtl/core`](https://github.com/stnolting/neorv32/blob/master/rtl)

|

| 525 |

|

|

folder to this project. Make sure to add these files to a **new design library** called `neorv32`.

|

| 526 |

|

|

|

| 527 |

40 |

zero_gravi |

You can either instantiate the [processor's top entity](https://github.com/stnolting/neorv32/blob/master/rtl/core/neorv32_top.vhd) or one of its

|

| 528 |

36 |

zero_gravi |

[wrappers](https://github.com/stnolting/neorv32/blob/master/rtl/top_templates) in your own project. If you just want to try out the processor,

|

| 529 |

|

|

you can use the simple [test setup](https://github.com/stnolting/neorv32/blob/master/rtl/top_templates/neorv32_test_setup.vhd) as top entity.

|

| 530 |

2 |

zero_gravi |

|

| 531 |

40 |

zero_gravi |

|

| 532 |

|

|

|

| 533 |

|

|

|

| 534 |

33 |

zero_gravi |

This test setup instantiates the processor and implements most of the peripherals and some ISA extensions. Only the UART lines, clock, reset and some GPIO output signals are

|

| 535 |

25 |

zero_gravi |

propagated as actual entity signals. Basically, it is a FPGA "hello world" example:

|

| 536 |

23 |

zero_gravi |

|

| 537 |

2 |

zero_gravi |

```vhdl

|

| 538 |

9 |

zero_gravi |

entity neorv32_test_setup is

|

| 539 |

|

|

port (

|

| 540 |

|

|

-- Global control --

|

| 541 |

|

|

clk_i : in std_ulogic := '0'; -- global clock, rising edge

|

| 542 |

|

|

rstn_i : in std_ulogic := '0'; -- global reset, low-active, async

|

| 543 |

|

|

-- GPIO --

|

| 544 |

|

|

gpio_o : out std_ulogic_vector(7 downto 0); -- parallel output

|

| 545 |

|

|

-- UART --

|

| 546 |

|

|

uart_txd_o : out std_ulogic; -- UART send data

|

| 547 |

|

|

uart_rxd_i : in std_ulogic := '0' -- UART receive data

|

| 548 |

|

|

);

|

| 549 |

|

|

end neorv32_test_setup;

|

| 550 |

2 |

zero_gravi |

```

|

| 551 |

|

|

|

| 552 |

|

|

|

| 553 |

23 |

zero_gravi |

### Check the Toolchain

|

| 554 |

2 |

zero_gravi |

|

| 555 |

11 |

zero_gravi |

Make sure `GNU Make` and a native `GCC` compiler are installed. To test the installation of the RISC-V toolchain navigate to an example project like

|

| 556 |

2 |

zero_gravi |

`sw/example/blink_led` and run:

|

| 557 |

|

|

|

| 558 |

|

|

neorv32/sw/example/blink_led$ make check

|

| 559 |

|

|

|

| 560 |

23 |

zero_gravi |

|

| 561 |

|

|

### Compiling an Example Program

|

| 562 |

|

|

|

| 563 |

9 |

zero_gravi |

The NEORV32 project includes some [example programs](https://github.com/stnolting/neorv32/tree/master/sw/example) from

|

| 564 |

|

|

which you can start your own application. Simply compile one of these projects. This will create a NEORV32

|

| 565 |

23 |

zero_gravi |

*executable* `neorv32_exe.bin` in the same folder:

|

| 566 |

2 |

zero_gravi |

|

| 567 |

23 |

zero_gravi |

neorv32/sw/example/blink_led$ make clean_all exe

|

| 568 |

2 |

zero_gravi |

|

| 569 |

23 |

zero_gravi |

|

| 570 |

|

|

### Upload the Executable via the Bootloader

|

| 571 |

|

|

|

| 572 |

34 |

zero_gravi |

You can upload a generated executable directly from the command line using the makefile's `upload` target. Replace `/dev/ttyUSB0` with

|

| 573 |

|

|

the according serial port.

|

| 574 |

|

|

|

| 575 |

|

|

sw/exeample/blink_example$ make COM_PORT=/dev/ttyUSB0` upload

|

| 576 |

|

|

|

| 577 |

|

|

A more "secure" way is to use a dedicated terminal program. This allows to directly interact with the bootloader console.

|

| 578 |

23 |

zero_gravi |

Connect your FPGA board via UART to your computer and open the according port to interface with the NEORV32 bootloader. The bootloader

|

| 579 |

2 |

zero_gravi |

uses the following default UART configuration:

|

| 580 |

|

|

|

| 581 |

32 |

zero_gravi |

* 19200 Baud

|

| 582 |

|

|

* 8 data bits

|

| 583 |

|

|

* 1 stop bit

|

| 584 |

|

|

* No parity bits

|

| 585 |

|

|

* No transmission / flow control protocol (raw bytes only)

|

| 586 |

|

|

* Newline on `\r\n` (carriage return & newline) - also for sent data

|

| 587 |

2 |

zero_gravi |

|

| 588 |

23 |

zero_gravi |

Use the bootloader console to upload the `neorv32_exe.bin` executable and run your application image.

|

| 589 |

2 |

zero_gravi |

|

| 590 |

9 |

zero_gravi |

```

|

| 591 |

43 |

zero_gravi |

<< NEORV32 Bootloader >>

|

| 592 |

|

|

|

| 593 |

|

|

BLDV: Nov 7 2020

|

| 594 |

|

|

HWV: 0x01040606

|

| 595 |

|

|

CLK: 0x0134FD90 Hz

|

| 596 |

|

|

USER: 0x0001CE40

|

| 597 |

|

|

MISA: 0x42801104

|

| 598 |

|

|

PROC: 0x03FF0035

|

| 599 |

|

|

IMEM: 0x00010000 bytes @ 0x00000000

|

| 600 |

|

|

DMEM: 0x00010000 bytes @ 0x80000000

|

| 601 |

|

|

|

| 602 |

|

|

Autoboot in 8s. Press key to abort.

|

| 603 |

|

|

Aborted.

|

| 604 |

|

|

|

| 605 |

|

|

Available CMDs:

|

| 606 |

|

|

h: Help

|

| 607 |

|

|

r: Restart

|

| 608 |

|

|

u: Upload

|

| 609 |

|

|

s: Store to flash

|

| 610 |

|

|

l: Load from flash

|

| 611 |

|

|

e: Execute

|

| 612 |

|

|

CMD:> u

|

| 613 |

|

|

Awaiting neorv32_exe.bin... OK

|

| 614 |

|

|

CMD:> e

|

| 615 |

|

|

Booting...

|

| 616 |

|

|

|

| 617 |

|

|

Blinking LED demo program

|

| 618 |

9 |

zero_gravi |

```

|

| 619 |

2 |

zero_gravi |

|

| 620 |

40 |

zero_gravi |

Going further: Take a look at the _Let's Get It Started!_ chapter of the [:page_facing_up: NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf).

|

| 621 |

2 |

zero_gravi |

|

| 622 |

|

|

|

| 623 |

|

|

|

| 624 |

40 |

zero_gravi |

## Contribute/Feedback/Questions

|

| 625 |

2 |

zero_gravi |

|

| 626 |

9 |

zero_gravi |

I'm always thankful for help! So if you have any questions, bug reports, ideas or if you want to give some kind of feedback, feel free

|

| 627 |

40 |

zero_gravi |

to [:bulb: open a new issue](https://github.com/stnolting/neorv32/issues), start a new [:sparkles: discussion on GitHub](https://github.com/stnolting/neorv32/discussions)

|

| 628 |

|

|

or directly [:e-mail: drop me a line](mailto:stnolting@gmail.com).

|

| 629 |

2 |

zero_gravi |

|

| 630 |

40 |

zero_gravi |

If you'd like to directly contribute to this repository:

|

| 631 |

22 |

zero_gravi |

|

| 632 |

40 |

zero_gravi |

0. :star: this repository ;)

|

| 633 |

|

|

1. Check out the project's [code of conduct](https://github.com/stnolting/neorv32/tree/master/CODE_OF_CONDUCT.md)

|

| 634 |

|

|

2. [Fork](https://github.com/stnolting/neorv32/fork) this repository and clone the fork

|

| 635 |

|

|

3. Create a feature branch in your fork: `git checkout -b awesome_new_feature_branch`

|

| 636 |

|

|

4. Create a new remote for the upstream repo: `git remote add upstream https://github.com/stnolting/neorv32`

|

| 637 |

|

|

5. Commit your modifications: `git commit -m "Awesome new feature!"`

|

| 638 |

|

|

6. Push to the branch: `git push origin awesome_new_feature_branch`

|

| 639 |

|

|

7. Create a new [pull request](https://github.com/stnolting/neorv32/pulls)

|

| 640 |

2 |

zero_gravi |

|

| 641 |

40 |

zero_gravi |

|

| 642 |

11 |

zero_gravi |

## Legal

|

| 643 |

2 |

zero_gravi |

|

| 644 |

12 |

zero_gravi |

This project is released under the BSD 3-Clause license. No copyright infringement intended.

|

| 645 |

11 |

zero_gravi |

Other implied or used projects might have different licensing - see their documentation to get more information.

|

| 646 |

|

|

|

| 647 |

37 |

zero_gravi |

#### Citing

|

| 648 |

11 |

zero_gravi |

|

| 649 |

34 |

zero_gravi |

If you are using the NEORV32 or some parts of the project in some kind of publication, please cite it as follows:

|

| 650 |

2 |

zero_gravi |

|

| 651 |

34 |

zero_gravi |

> S. Nolting, "The NEORV32 Processor", github.com/stnolting/neorv32

|

| 652 |

2 |

zero_gravi |

|

| 653 |

9 |

zero_gravi |

#### BSD 3-Clause License

|

| 654 |

2 |

zero_gravi |

|

| 655 |

42 |

zero_gravi |

Copyright (c) 2021, Stephan Nolting. All rights reserved.

|

| 656 |

2 |

zero_gravi |

|

| 657 |

|

|

Redistribution and use in source and binary forms, with or without modification, are

|

| 658 |

|

|

permitted provided that the following conditions are met:

|

| 659 |

|

|

|

| 660 |

|

|

1. Redistributions of source code must retain the above copyright notice, this list of

|

| 661 |

|

|

conditions and the following disclaimer.

|

| 662 |

|

|

2. Redistributions in binary form must reproduce the above copyright notice, this list of

|

| 663 |

|

|

conditions and the following disclaimer in the documentation and/or other materials

|

| 664 |

|

|

provided with the distribution.

|

| 665 |

|

|

3. Neither the name of the copyright holder nor the names of its contributors may be used to

|

| 666 |

|

|

endorse or promote products derived from this software without specific prior written

|

| 667 |

|

|

permission.

|

| 668 |

|

|

|

| 669 |

|

|

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS

|

| 670 |

|

|

OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF

|

| 671 |

|

|

MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE

|

| 672 |

|

|

COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL,

|

| 673 |

|

|

EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE

|

| 674 |

|

|

GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED

|

| 675 |

|

|

AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING

|

| 676 |

|

|

NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED

|

| 677 |

|

|

OF THE POSSIBILITY OF SUCH DAMAGE.

|

| 678 |

|

|

|

| 679 |

|

|

|

| 680 |

9 |

zero_gravi |

#### Limitation of Liability for External Links

|

| 681 |

|

|

|

| 682 |

36 |

zero_gravi |

Our website contains links to the websites of third parties ("external links"). As the

|

| 683 |

9 |

zero_gravi |

content of these websites is not under our control, we cannot assume any liability for

|

| 684 |

|

|

such external content. In all cases, the provider of information of the linked websites

|

| 685 |

|

|

is liable for the content and accuracy of the information provided. At the point in time

|

| 686 |

|

|

when the links were placed, no infringements of the law were recognisable to us. As soon

|

| 687 |

|

|

as an infringement of the law becomes known to us, we will immediately remove the

|

| 688 |

|

|

link in question.

|

| 689 |

|

|

|

| 690 |

|

|

|

| 691 |

11 |

zero_gravi |

#### Proprietary Notice

|

| 692 |

9 |

zero_gravi |

|

| 693 |

2 |

zero_gravi |

"Artix" and "Vivado" are trademarks of Xilinx Inc.

|

| 694 |

|

|

|

| 695 |

45 |

zero_gravi |

"Cyclone" and "Quartus Prime Lite" are trademarks of Intel Corporation.

|

| 696 |

2 |

zero_gravi |

|

| 697 |

35 |

zero_gravi |

"iCE40", "UltraPlus" and "Radiant" are trademarks of Lattice Semiconductor Corporation.

|

| 698 |

11 |

zero_gravi |

|

| 699 |

35 |

zero_gravi |

"AXI", "AXI4" and "AXI4-Lite" are trademarks of Arm Holdings plc.

|

| 700 |

2 |

zero_gravi |

|

| 701 |

|

|

|

| 702 |

|

|

|

| 703 |

18 |

zero_gravi |

## Acknowledgements

|

| 704 |

9 |

zero_gravi |

|

| 705 |

18 |

zero_gravi |

[](https://riscv.org/)

|

| 706 |

|

|

|

| 707 |

23 |

zero_gravi |

[RISC-V](https://riscv.org/) - Instruction Sets Want To Be Free!

|

| 708 |

11 |

zero_gravi |

|

| 709 |

43 |

zero_gravi |

Continous integration provided by [:octocat: GitHub Actions](https://github.com/features/actions) and powered by [GHDL](https://github.com/ghdl/ghdl).

|

| 710 |

2 |

zero_gravi |

|

| 711 |

|

|

|

| 712 |

|

|

|

| 713 |

|

|

This project is not affiliated with or endorsed by the Open Source Initiative (https://www.oshwa.org / https://opensource.org).

|

| 714 |

|

|

|

| 715 |

32 |

zero_gravi |

--------

|

| 716 |

2 |

zero_gravi |

|

| 717 |

36 |

zero_gravi |

Made with :coffee: in Hannover, Germany :eu:

|