URL

https://opencores.org/ocsvn/openmsp430/openmsp430/trunk

Subversion Repositories openmsp430

Compare Revisions

- This comparison shows the changes necessary to convert path

/openmsp430/trunk/doc

- from Rev 151 to Rev 166

- ↔ Reverse comparison

Rev 151 → Rev 166

/openMSP430.pdf

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

/html/software_development_tools.html

1,9 → 1,5

<!DOCTYPE HTML PUBLIC "-//W3C//DTD HTML 4.01//EN" "http://www.w3.org/TR/html4/strict.dtd"> |

<html><head> |

<title>openMSP430 Software Development Tools</title> |

|

|

</head><body> |

<html><head><title>openMSP430 Software Development Tools</title></head><body> |

<h3>Table of content</h3> |

|

<ul> |

49,20 → 45,47

<br> |

|

In order to connect the host PC to the openMSP430 serial debug |

interface, a serial cable is required.<br> |

interface, a UART or I2C serial cable/adapter is required.<br> |

|

Typically, the following solutions will suit any kind of development |

board:<br> |

board:<br><br> |

<table style="text-align: left; width: 50%; margin-left: auto; margin-right: auto;" border="1" cellpadding="2" cellspacing="2"> |

<tbody> |

|

<tr> |

<td style="vertical-align: top; text-align: center;"><strong>UART</strong><br> |

</td> |

<td style="vertical-align: top; text-align: center;"><strong>I<sup>2</sup>C</strong><br> |

</td> |

</tr> |

<tr> |

<td style="vertical-align: top; text-align: left;"> |

<span style="font-weight: bold;"><br><a href="http://www.ftdichip.com/Products/Cables/USBRS232.htm"> |

USB to RS232 converter:</a></span><br> |

<br> |

<div style="text-align: center;"><img src="http://opencores.org/usercontent,img,1353274537" alt="USB to RS232" title="USB to RS232" width="25%"> |

<br> |

</div> |

|

<ul> |

<a href="http://www.ftdichip.com/Products/Cables/USBTTLSerial.htm"><span style="font-weight: bold;"> |

USB to Serial TTL converter:</span></a><br><br> |

<div style="text-align: center;"><img src="http://opencores.org/usercontent,img,1353274560" alt="USB to Serial TTL" title="USB to Serial TTL" width="25%"> |

<br> |

|

<li><a href="http://www.ftdichip.com/Products/Cables/USBRS232.htm">USB |

to RS232 converter</a></li> |

<li><a href="http://www.ftdichip.com/Products/Cables/USBTTLSerial.htm">USB |

to Serial TTL converter</a><br> |

</li> |

</ul> |

</div> |

</td> |

<td style="vertical-align: top; text-align: left;"><br> |

<a href="http://www.robot-electronics.co.uk/htm/usb_iss_tech.htm"><span style="font-weight: bold;">Devantech USB-ISS adapter:</span></a><br><br> |

<div style="text-align: center;"><img src="http://opencores.org/usercontent,img,1353274507" alt="USB to I2C adapter" title="USB to I2C adapter" width="75%"> |

<br> |

|

</div> |

</td> |

</tr> |

</tbody> |

</table> |

<ul></ul> |

|

<a name="2. openmsp430-loader"></a> |

<h1>2. openmsp430-loader</h1> |

|

89,15 → 112,30

</td> |

<td width="15"><br> |

</td> |

<td> <code>openmsp430-loader.tcl [-device <communication |

device>] [-baudrate <communication speed>] |

<elf/ihex-file> |

<td> <code><br> |

USAGE : openmsp430-loader.tcl [-device <communication port>]<br> |

|

[-adaptor <adaptor type>]<br> |

|

[-speed <communication speed>]<br> |

|

[-i2c_addr <cpu |

address>] |

<elf/ihex-file><br> |

<br> |

DEFAULT : <communication port> = /dev/ttyUSB0<br> |

<adaptor |

type> = uart_generic<br> |

<communication speed> = 115200 (for UART) / I2C_S_100KHZ (for I2C)<br> |

<core address> = 42<br> |

<br> |

Examples: openmsp430-loader.tcl -device /dev/ttyUSB0 -baudrate 9600 |

leds.elf<br> |

openmsp430-loader.tcl |

-device COM2: -baudrate 38400 ta_uart.ihex </code> |

EXAMPLES: openmsp430-loader.tcl -device /dev/ttyUSB0 -adaptor uart_generic -speed 9600 leds.elf<br> |

|

openmsp430-loader.tcl -device |

COM2: -adaptor |

i2c_usb-iss -speed I2C_S_100KHZ -i2c_addr 75 ta_uart.ihex<br> |

<br> |

</code> |

</td> |

</tr> |

</tbody> |

109,13 → 147,12

<br> |

|

<br> |

|

<img src="usercontent,img,1306525377" alt="openmsp430-loader Linux" title="openmsp430-loader Linux" width="75%"> |

<img src="http://opencores.org/usercontent,img,1353618648" alt="openmsp430-loader Linux" title="openmsp430-loader Linux" width="100%"> |

<br> |

|

<br> |

|

<img src="usercontent,img,1249244501" alt="openmsp430-loader Windows" title="openmsp430-loader Windows" width="75%"> |

<img src="http://opencores.org/usercontent,img,1249244501" alt="openmsp430-loader Windows" title="openmsp430-loader Windows" width="75%"> |

<br> |

|

<a name="3. openmsp430-minidebug"></a> |

126,8 → 163,7

<br> |

|

<br> |

|

<img src="usercontent,img,1306665243" alt="openmsp430-minidebug" title="openmsp430-minidebug" width="75%"> |

<img src="http://opencores.org/usercontent,img,1353618607" alt="openmsp430-minidebug" title="openmsp430-minidebug" width="75%"> |

<br> |

|

<br> |

170,7 → 206,7

|

<br> |

|

<img src="usercontent,img,1248897690" alt="GDB Proxy flow" title="GDB Proxy flow" width="40%"> |

<img src="http://opencores.org/usercontent,img,1248897690" alt="GDB Proxy flow" title="GDB Proxy flow" width="40%"> |

<br> |

|

<br> |

181,8 → 217,7

<br> |

|

<br> |

|

<img src="usercontent,img,1306525816" alt="gdbproxy" title="gdbproxy" width="60%"> |

<img src="http://opencores.org/usercontent,img,1353618690" alt="gdbproxy" title="gdbproxy" width="60%"> |

<br> |

|

<br> |

192,12 → 227,12

|

<br> |

|

<img src="usercontent,img,1320787180" alt="gdbproxy-Eclipse" title="gdbproxy-Eclipse" width="100%"> |

<img src="http://opencores.org/usercontent,img,1320787180" alt="gdbproxy-Eclipse" title="gdbproxy-Eclipse" width="100%"> |

<br> |

|

<br> |

|

<img src="usercontent,img,1306526049" alt="gdbproxy-DDD" title="gdbproxy-DDD" width="100%"> |

<img src="http://opencores.org/usercontent,img,1306526049" alt="gdbproxy-DDD" title="gdbproxy-DDD" width="100%"> |

<br> |

|

<br> |

1232,7 → 1267,7

<tr> |

<td style="vertical-align: top; text-align: center;">msp430x1491<br> |

</td> |

<td style="vertical-align: top; text-align: center;">59 kB<br> |

<td style="vertical-align: top; text-align: center;">60 kB<br> |

</td> |

<td style="vertical-align: top; text-align: center;">2048 B<br> |

</td> |

1241,7 → 1276,7

<tr> |

<td style="vertical-align: top; text-align: center;">msp430x149<br> |

</td> |

<td style="vertical-align: top; text-align: center;">59 kB<br> |

<td style="vertical-align: top; text-align: center;">60 kB<br> |

</td> |

<td style="vertical-align: top; text-align: center;">2048 B<br> |

</td> |

/html/images/dbg_i2c_cmd_write_burst.png

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

html/images/dbg_i2c_cmd_write_burst.png

Property changes :

Added: svn:mime-type

## -0,0 +1 ##

+application/octet-stream

\ No newline at end of property

Index: html/images/openmsp430-minidebug.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/USB-ISS.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/USB-ISS.png

===================================================================

--- html/images/USB-ISS.png (nonexistent)

+++ html/images/USB-ISS.png (revision 166)

html/images/USB-ISS.png

Property changes :

Added: svn:mime-type

## -0,0 +1 ##

+application/octet-stream

\ No newline at end of property

Index: html/images/dbg_i2c_cmd_frame.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/dbg_i2c_cmd_frame.png

===================================================================

--- html/images/dbg_i2c_cmd_frame.png (nonexistent)

+++ html/images/dbg_i2c_cmd_frame.png (revision 166)

html/images/dbg_i2c_cmd_frame.png

Property changes :

Added: svn:mime-type

## -0,0 +1 ##

+application/octet-stream

\ No newline at end of property

Index: html/images/dbg_i2c_cmd_write.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/dbg_i2c_cmd_write.png

===================================================================

--- html/images/dbg_i2c_cmd_write.png (nonexistent)

+++ html/images/dbg_i2c_cmd_write.png (revision 166)

html/images/dbg_i2c_cmd_write.png

Property changes :

Added: svn:mime-type

## -0,0 +1 ##

+application/octet-stream

\ No newline at end of property

Index: html/images/dbg_uart_cmd_write_burst.odg

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/dbg_i2c_cmd_read.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/dbg_i2c_cmd_read.png

===================================================================

--- html/images/dbg_i2c_cmd_read.png (nonexistent)

+++ html/images/dbg_i2c_cmd_read.png (revision 166)

html/images/dbg_i2c_cmd_read.png

Property changes :

Added: svn:mime-type

## -0,0 +1 ##

+application/octet-stream

\ No newline at end of property

Index: html/images/dbg_uart_cmd_write.odg

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/dbg_uart_cmd_read_burst.odg

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/dbg_uart_cmd_frame.odg

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/usb2uart_ttl.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/usb2uart_ttl.png

===================================================================

--- html/images/usb2uart_ttl.png (nonexistent)

+++ html/images/usb2uart_ttl.png (revision 166)

html/images/usb2uart_ttl.png

Property changes :

Added: svn:mime-type

## -0,0 +1 ##

+application/octet-stream

\ No newline at end of property

Index: html/images/cpu_structure.odg

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/wave_sdi_i2c.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/wave_sdi_i2c.png

===================================================================

--- html/images/wave_sdi_i2c.png (nonexistent)

+++ html/images/wave_sdi_i2c.png (revision 166)

html/images/wave_sdi_i2c.png

Property changes :

Added: svn:mime-type

## -0,0 +1 ##

+application/octet-stream

\ No newline at end of property

Index: html/images/dbg_i2c_sda_io.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/dbg_i2c_sda_io.png

===================================================================

--- html/images/dbg_i2c_sda_io.png (nonexistent)

+++ html/images/dbg_i2c_sda_io.png (revision 166)

html/images/dbg_i2c_sda_io.png

Property changes :

Added: svn:mime-type

## -0,0 +1 ##

+application/octet-stream

\ No newline at end of property

Index: html/images/cpu_structure.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/core_integration.odg

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/dbg_i2c_cmd_read_burst.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/dbg_i2c_cmd_read_burst.png

===================================================================

--- html/images/dbg_i2c_cmd_read_burst.png (nonexistent)

+++ html/images/dbg_i2c_cmd_read_burst.png (revision 166)

html/images/dbg_i2c_cmd_read_burst.png

Property changes :

Added: svn:mime-type

## -0,0 +1 ##

+application/octet-stream

\ No newline at end of property

Index: html/images/dbg_i2c.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/dbg_i2c.png

===================================================================

--- html/images/dbg_i2c.png (nonexistent)

+++ html/images/dbg_i2c.png (revision 166)

html/images/dbg_i2c.png

Property changes :

Added: svn:mime-type

## -0,0 +1 ##

+application/octet-stream

\ No newline at end of property

Index: html/images/core_integration.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/dbg_uart_8N1.odg

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/openmsp430-gdbproxy.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/usb2uart.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/usb2uart.png

===================================================================

--- html/images/usb2uart.png (nonexistent)

+++ html/images/usb2uart.png (revision 166)

html/images/usb2uart.png

Property changes :

Added: svn:mime-type

## -0,0 +1 ##

+application/octet-stream

\ No newline at end of property

Index: html/images/openmsp430-loader_lin.png

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/images/dbg_uart_cmd_read.odg

===================================================================

Cannot display: file marked as a binary type.

svn:mime-type = application/octet-stream

Index: html/integration.html

===================================================================

--- html/integration.html (revision 151)

+++ html/integration.html (revision 166)

@@ -1,8 +1,5 @@

-openMSP430 Integration and Connectivity

-

-

-

+openMSP430 Integration and Connectivity

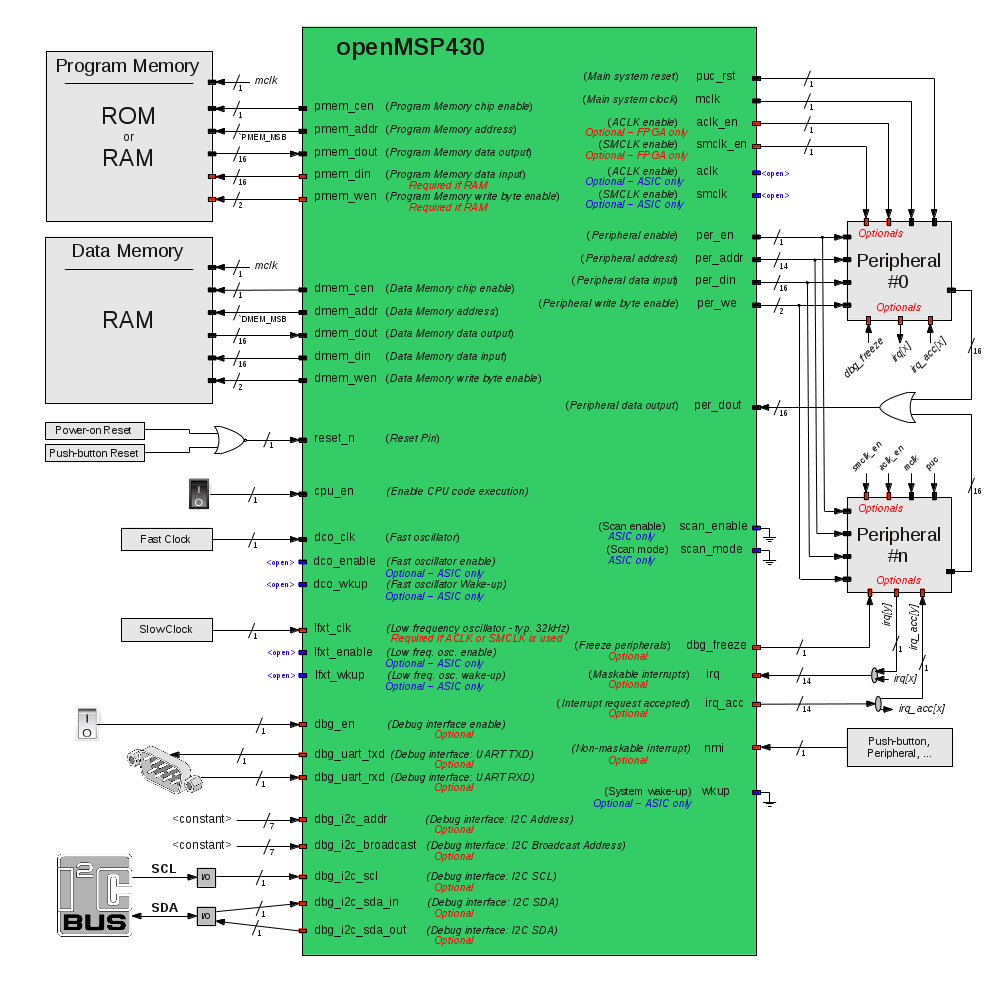

The following diagram shows an overview of the openMSP430 core connectivity in an FPGA system (i.e. all ASIC specific pins are left unused):

- +

+

The full pinout of the core is summarized in the following table.

@@ -323,7 +324,7 @@ Freeze peripherals

- dbg_uart_txd

+ dbg_uart_txd

Output

1

mclk

@@ -330,13 +331,51 @@

Debug interface: UART TXD

- dbg_uart_rxd

+ dbg_uart_rxd

Input

1

<async>

Debug interface: UART RXD (asynchronous)

-

+

+ dbg_i2c_addr

+ Input

+ 1

+ mclk

+

+ Debug interface: I2C Address

+

+

+ dbg_i2c_broadcast

+ Input

+ 1

+ mclk

+

+ Debug interface: I2C Broadcast Address (for multicore only)

+

+

+ dbg_i2c_scl

+ Input

+ 1

+ <async>

+ Debug interface: I2C SCL

+

+

+ dbg_i2c_sda_in

+ Input

+ 1

+ <async>

+ Debug interface: I2C SDA input

+

+

+ dbg_i2c_sda_out

+ Output

+ 1

+ mclk

+

+ Debug interface: I2C SDA output

+

+

Scan

@@ -377,12 +416,12 @@

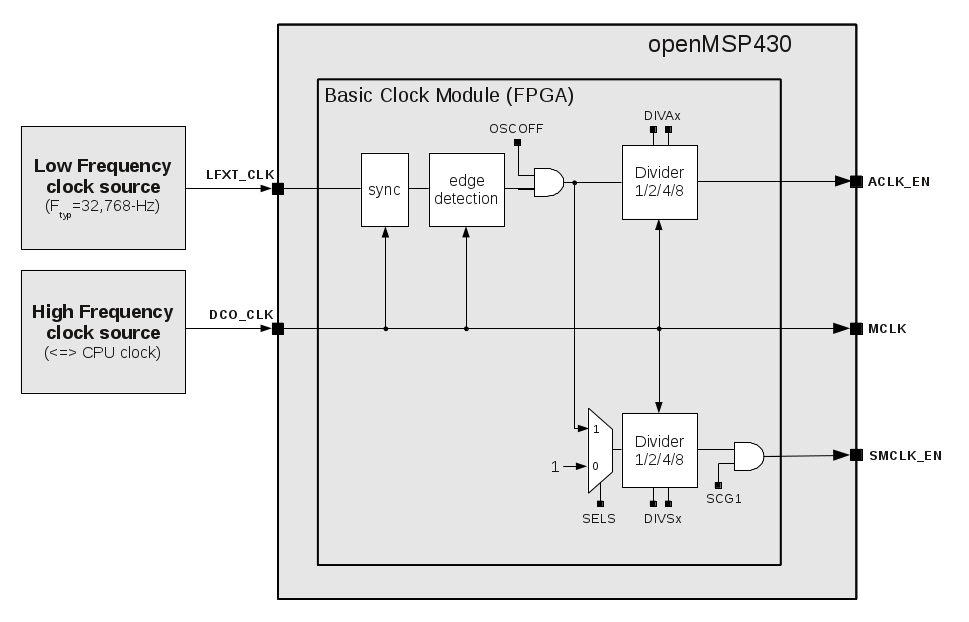

The different clocks in the design are managed by the Basic Clock Module as following in the FPGA configuration:

- +

+

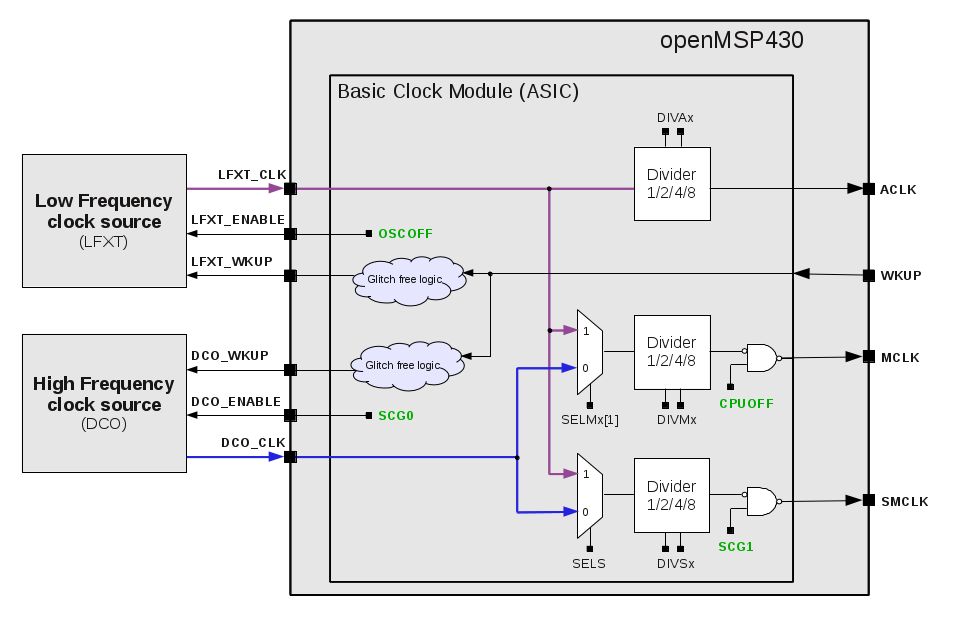

or as following in the ASIC configuration:

- +

+

- +

+

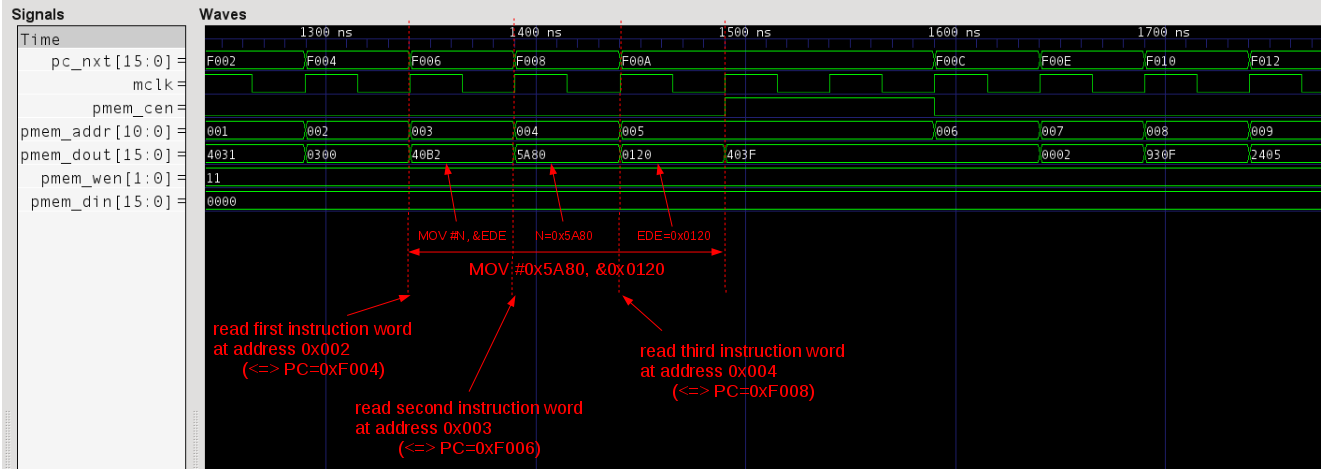

@@ -509,7 +544,7 @@ The following waveform illustrates some read accesses of the program memory (write access are illustrated in the data memory section):

- +

+

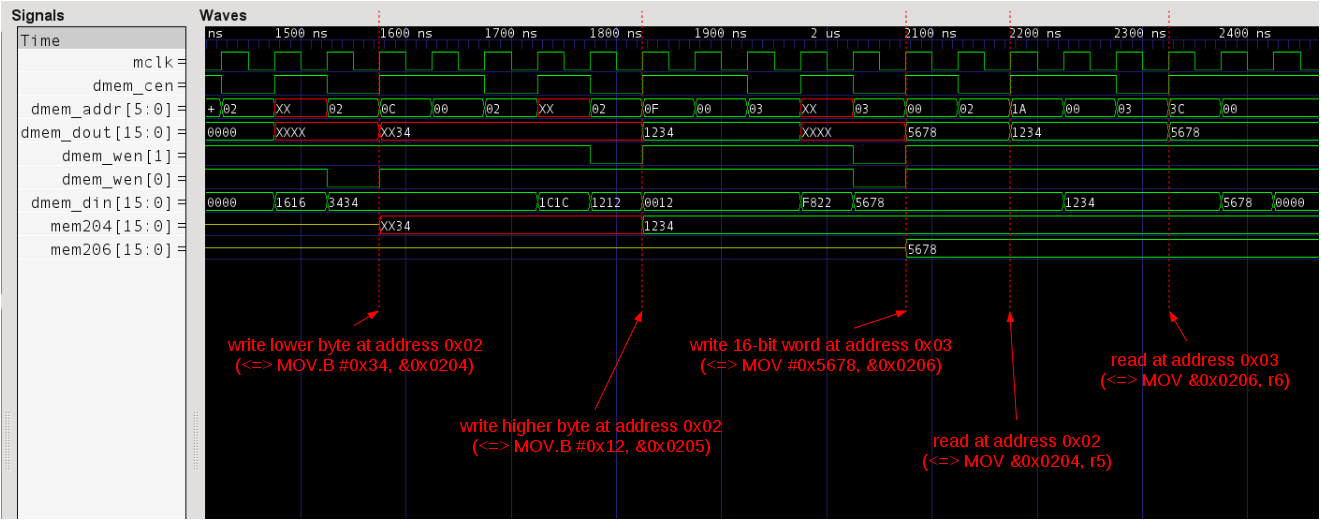

@@ -545,7 +580,7 @@ The following waveform illustrates some read/write access to the data memory:

- +

+

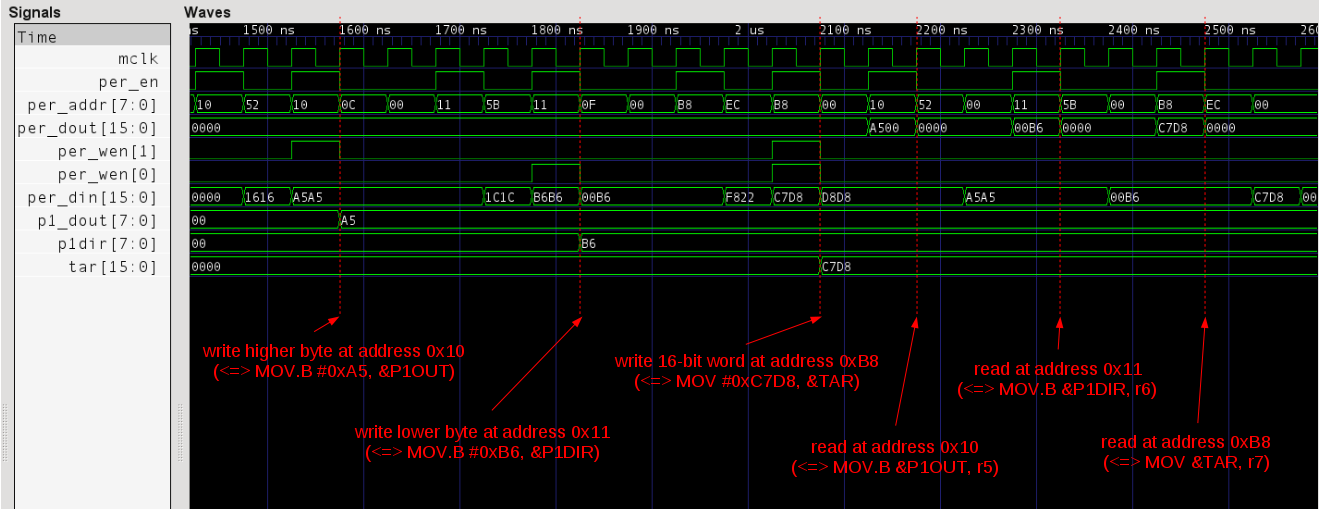

@@ -594,7 +629,7 @@ The following waveform illustrates some read/write access to the peripheral registers:

- +

+

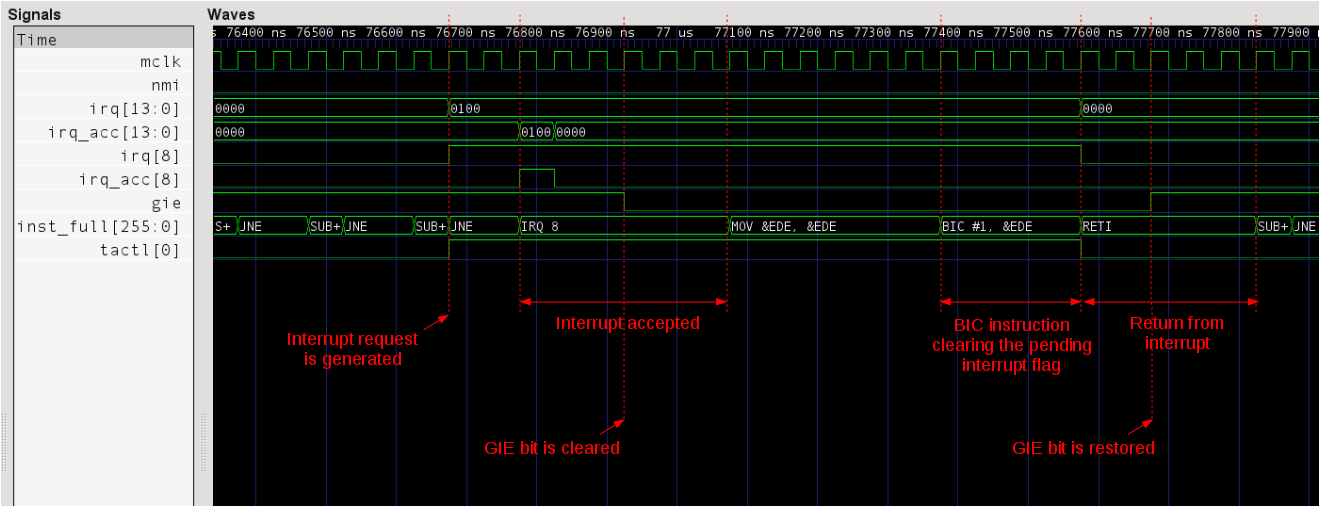

@@ -717,7 +752,7 @@ The following waveform illustrates a TAIV interrupt issued by the Timer-A, which is connected to IRQ[8] :

- +

+

@@ -726,7 +761,7 @@

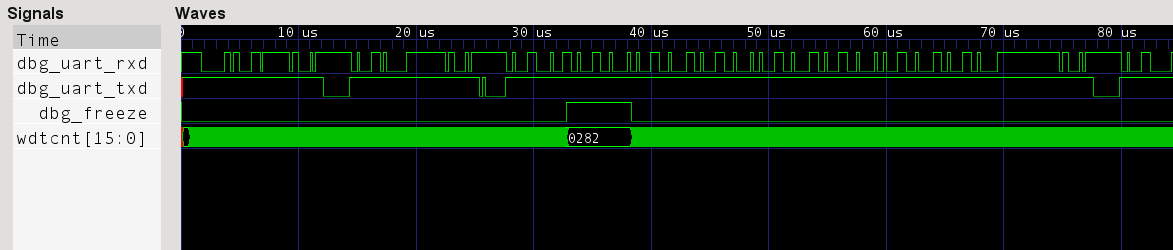

- +The following waveform shows some communication traffic on the UART serial bus :

+The following waveform shows some communication traffic on the UART serial bus :

+

+ +

+ +

+

+ + \ No newline at end of file

+

Table of content

-

@@ -9,11 +6,15 @@

- 1. Overview

- 2. Clocks

- 3. Resets -

- 4. Program Memory -

- 5. Data Memory +

- 4. Program Memory +

- 5. Data Memory

- 6. Peripherals

- 7. Interrupts

- 8. Serial Debug Interface +

The following diagram shows an overview of the openMSP430 core connectivity in an FPGA system (i.e. all ASIC specific pins are left unused):

-

The full pinout of the core is summarized in the following table.

@@ -323,7 +324,7 @@

+

+

+

-

or as following in the ASIC configuration:

-

-

@@ -400,11 +439,7 @@

through the Watchdog or TimerA peripherals), then this port needs to be

connected to a clock running at least two time slower as DCO_CLK

(typically 32kHz). It can be connected to 0 or 1 otherwise.

-+ In an ASIC, if ACLK or SMCLK are used and if the clock muxes are included, then this port can be connected to any kind of clock source (it doesn't need to be low-frequency. The name was just @@ -422,7 +457,7 @@ original ACLK and SMCLK from the MSP430 specification when the core is targeting an FPGA.

An example of this can be found in the Watchdog and TimerA modules, where it is implemented as following:

-

+

-

@@ -443,7 +478,7 @@

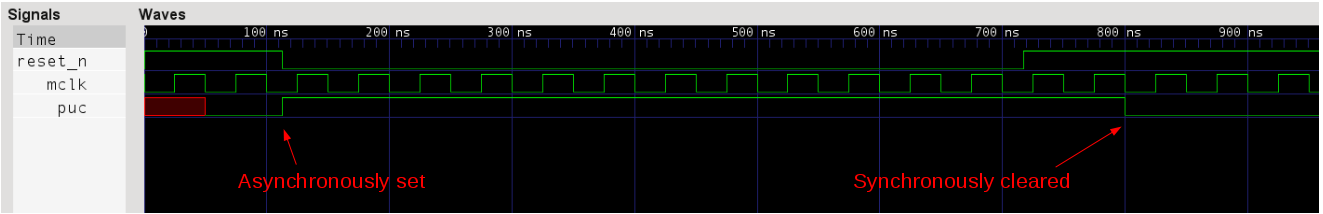

As an FPGA system illustration, the following waveform shows the different

clocks where the software running on the openMSP430 configures the

BCSCTL1 and BCSCTL2 registers so that ACLK_EN and SMCLK_EN are respectively running at LFXT_CLK/2 and DCO_CLK/4.

-

@@ -463,7 +498,7 @@

-

@@ -509,7 +544,7 @@ The following waveform illustrates some read accesses of the program memory (write access are illustrated in the data memory section):

-

@@ -545,7 +580,7 @@ The following waveform illustrates some read/write access to the data memory:

-

@@ -594,7 +629,7 @@ The following waveform illustrates some read/write access to the peripheral registers:

-

@@ -717,7 +752,7 @@ The following waveform illustrates a TAIV interrupt issued by the Timer-A, which is connected to IRQ[8] :

-

@@ -726,7 +761,7 @@

8. Serial Debug Interface

The serial debug interface module provides a two-wires communication -bus for remote debugging and an additional freeze signal which might be +bus (UART or I2C) for remote debugging and an additional freeze signal which might be useful for some peripherals (typically timers).-

@@ -743,12 +778,46 @@

watchdog every times the user stops the CPU during a debugging session.

+

8.1 UART Configuration

+-

DBG_UART_TXD / DBG_UART_RXD: these signals are typically connected to an RS-232 transceiver and will allow a PC to communicate with the openMSP430 core.

-

+

+ +

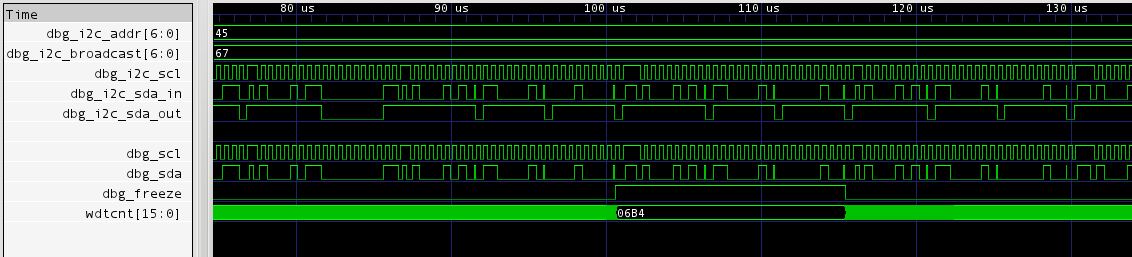

8.2 I2C Configuration

+-

+

-

+ DBG_I2C_ADDR: I2C Device address of the oMSP core (between 8 and 119). In a multi-core configuration each core has its own address.

+

+

+ -

+ DBG_I2C_BROADCAST:

+I2C Device broadcast address of the oMSP core (between 8 and 119). In a

+multi-core configuration all cores have the same broadcast address.

+

+ -

+ DBG_I2C_SCL: I2C bus clock input (SCL).

+

+

+ -

+ DBG_I2C_SDA_OUT / DBG_I2C_SDA_IN: these signals are connected to the SDA I/O cell as following:

+++

+

+

+

+

+ + \ No newline at end of file

/html/serial_debug_interface.html

1,10 → 1,13

<!DOCTYPE HTML PUBLIC "-//W3C//DTD HTML 4.01//EN" "http://www.w3.org/TR/html4/strict.dtd"> |

<html><head><title>openMSP430 Serial Debug Interface</title></head><body> |

<html><head><title>openMSP430 Serial Debug Interface</title> |

|

|

<meta http-equiv="content-type" content="text/html; charset=utf-8"></head><body> |

<a name="TOC"></a> |

<h3>Table of content</h3> |

<ul> |

<li><a href="#1.%20Introduction"> 1. Introduction</a></li> |

<li><a href="#2.%20Debug%20Unit"> 2. Debug Unit</a> |

<li><strong><a href="#1.%20Introduction"> 1. Introduction</a></strong></li> |

<li><strong><a href="#2.%20Debug%20Unit"> 2. Debug Unit</a></strong> |

<ul> |

<li><a href="#2.1%20Register%20Mapping"> 2.1 Register Mapping</a></li> |

<li><a href="#2.2%20CPU%20Control/Status%20Registers"> 2.2 CPU Control/Status Registers</a></li> |

12,6 → 15,7

<li><a href="#2.2.1%20CPU_ID"> 2.2.1 CPU_ID</a></li> |

<li><a href="#2.2.2%20CPU_CTL"> 2.2.2 CPU_CTL</a></li> |

<li><a href="#2.2.3%20CPU_STAT"> 2.2.3 CPU_STAT</a></li> |

<li><a href="#2.2.4%20CPU_NR"> 2.2.4 CPU_NR</a></li> |

</ul> |

<li><a href="#2.3%20Memory%20Access%20Registers"> 2.3 Memory Access Registers</a></li> |

<ul> |

29,7 → 33,7

</ul> |

</ul> |

</li> |

<li><a href="#3.%20Debug%20Communication%20Interface:%20UART"> 3. Debug Communication Interface: UART</a> |

<li><strong><a href="#3.%20Debug%20Communication%20Interface:%20UART"> 3. Debug Communication Interface: UART</a></strong> |

<ul> |

<li><a href="#3.1%20Serial%20communication%20protocol:%208N1"> 3.1 Serial communication protocol: 8N1</a></li> |

<li><a href="#3.2%20Synchronization%20frame"> 3.2 Synchronization frame</a></li> |

45,7 → 49,25

<li><a href="#3.4.2%20Read%20Burst%20access"> 3.4.2 Read Burst access</a></li> |

</ul> |

</ul> |

</li></ul> |

</li> |

<li><strong><a href="#4.%20Debug%20Communication%20Interface:%20I2C"> 4. Debug Communication Interface: I2C</a></strong> |

<ul> |

<li><a href="#4.1%20I2C%20communication%20protocol"> 4.1 I2C communication protocol</a></li> |

<li><a href="#4.2%20Synchronization%20frame"> 4.2 Synchronization frame</a></li> |

<li><a href="#4.3%20Read/Write%20access%20to%20the%20debug%20registers"> 4.3 Read/Write access to the debug registers</a></li> |

<ul> |

<li><a href="#4.3.1%20Command%20Frame"> 4.3.1 Command Frame</a></li> |

<li><a href="#4.3.2%20Write%20access"> 4.3.2 Write access</a></li> |

<li><a href="#4.3.3%20Read%20access"> 4.3.3 Read access</a></li> |

</ul> |

<li><a href="#4.4%20Read/Write%20burst%20implementation%20for%20the%20CPU%20Memory%20access">4.4 Read/Write burst implementation for the CPU Memory access</a></li> |

<ul> |

<li><a href="#4.4.1%20Write%20Burst%20access"> 4.4.1 Write Burst access</a></li> |

<li><a href="#4.4.2%20Read%20Burst%20access"> 4.4.2 Read Burst access</a></li> |

</ul> |

</ul> |

</li> |

</ul> |

|

<a name="1. Introduction"></a> |

<h1>1. Introduction</h1> |

54,21 → 76,91

with the host computer is typically built on a JTAG or Spy-Bi-Wire |

serial protocol. However, the global debug architecture from the MSP430 |

is unfortunately poorly documented on the web (and is also probably |

tightly linked with the internal core architecture). |

tightly linked with the internal core micro-architecture). |

<br><br>A custom module has therefore been implemented for the |

openMSP430. The communication with the host is done with a simple two-wire RS232 |

cable (8N1 serial protocol) and the debug unit provides all the |

required features for Nexus Class 3 debugging (beside trace), namely: <ul> |

<li>CPU control (run, stop, step, reset).</li> |

<li>Software & hardware breakpoint support.</li> |

<li>Hardware watchpoint support.<br> |

</li> |

openMSP430. The communication with the host is done with a simple two-wire cable following either the UART or I<sup>2</sup>C serial protocol (interface is selectable in the <a href="http://opencores.org/project,openmsp430,core#2.1.3.3%20Expert%20System%20Configuration">Expert System Configuraiton</a> section). |

<br><br>The debug unit provides all required features for Nexus Class 3 debugging (beside trace), namely: <br> |

<br> |

<table style="text-align: left; width: 50%; margin-left: auto; margin-right: auto;" border="1" cellpadding="2" cellspacing="2"> |

<tbody> |

<tr align="center"> |

<td style="vertical-align: top;"><span style="font-weight: bold;"><strong>Debug unit features</strong></span><br> |

</td> |

</tr> |

<tr> |

<td style="vertical-align: top;"> |

<ul> |

<li>CPU control (run, stop, step, reset).</li><li>Software & hardware breakpoint.</li><li>Hardware watchpoint.<br> |

</li><li>Memory read/write on-the-fly (no need to halt execution).</li><li>CPU registers read/write on-the-fly (no need to halt execution).</li> |

</ul> |

</td> |

</tr> |

</tbody> |

</table> |

<br> |

<ul></ul> |

|

<li>Memory read/write on-the-fly (no need to halt execution).</li> |

<li>CPU registers read/write on-the-fly (no need to halt execution).</li> |

</ul> |

Depending on the selected serial interface, the following features are available:<br> |

<br> |

<table style="text-align: left; width: 50%; margin-left: auto; margin-right: auto;" border="1" cellpadding="2" cellspacing="2"> |

<tbody> |

<tr align="center"> |

<td colspan="2" rowspan="1" style="vertical-align: top;"><span style="font-weight: bold;"><strong>Debug interface features</strong></span><br> |

</td> |

</tr> |

<tr> |

<td style="vertical-align: top; text-align: center;"><strong>UART</strong><br> |

</td> |

<td style="vertical-align: top; text-align: center;"><strong>I<sup>2</sup>C</strong><br> |

</td> |

</tr> |

<tr> |

<td style="vertical-align: top; text-align: left;"> |

<span style="font-weight: bold;"><br> |

Strengths:</span><br> |

<ul> |

|

<li>No extra hardware required for most FPGA boards (almost all come with a UART interface, either <a href="http://www.ftdichip.com/Products/Cables/USBRS232.htm">RS232 or USB</a> based).</li> |

|

<a name="2. Debug Unit"></a> |

|

<li>Possibility to use <a href="http://www.ftdichip.com/Products/Cables/USBTTLSerial.htm">USB to serial TTL</a> cables.</li> |

|

</ul><span style="font-weight: bold;">Weaknesses:</span><br> |

<ul> |

<li>Need to reset the debug interface after cable insertion.</li> |

<li>For ASICs, no possibility to change the MCLK frequency during a debug session.<br> |

</li> |

</ul> |

|

</td> |

<td style="vertical-align: top; text-align: left;"><br> |

<span style="font-weight: bold;">Strengths:</span><br> |

<ul> |

|

<li>Very stable interface (synchronous protocol, no synchronization frame required).</li> |

|

|

<li>Multi-core chip support with a single I2C |

interface (i.e. TWO pins)... in such a system, each openMSP430 instance has its own I2C device address.</li> |

<li>Possibility to combine the openMSP430 debug interface with |

an already existing "functional" I2C interface... effectively creating |

a ZERO |

wire serial debug interface.</li> |

<li>Affordable <a href="http://www.robot-electronics.co.uk/htm/usb_iss_tech.htm">USB-ISS adapter</a> (~23€).</li> |

</ul><span style="font-weight: bold;">Weaknesses:</span><br> |

<ul> |

<li>Extra I2C adapter required (<a href="http://www.robot-electronics.co.uk/htm/usb_iss_tech.htm">USB-ISS</a> currently supported)<br> |

</li> |

</ul> |

<br> |

|

</td> |

</tr> |

</tbody> |

</table> |

|

<a name="2. Debug Unit"></a><br> |

|

<div style="text-align: right;"><a href="#TOC">Top</a></div> |

<h1>2. Debug Unit</h1> |

|

277,6 → 369,13

<td><small>0x17</small></td> |

<td colspan="16"><font size="-5">BRK_ADDR1[15:0]</font></td> |

</tr> |

<tr align="center"> |

<td><small><a href="#2.2.4%20CPU_NR">CPU_NR</a></small></td> |

<td><small>0x18</small></td> |

<td colspan="8"><small>CPU_TOTAL_NR</small></td> |

<td colspan="8"><small>CPU_INST_NR</small></td> |

</tr> |

|

</tbody></table> |

|

<a name="2.2 CPU Control/Status Registers"></a> |

449,19 → 548,19

<table border="0"> |

<tbody><tr> |

<td> </td><td valign="top"><li><b>HWBRK3_PND</b></li></td> |

<td>: This bit reflects if one of the Hardware Breakpoint Unit 3 status bit is set (i.e. BRK3_STAT≠0).</td> |

<td>: This bit reflects if one of the Hardware Breakpoint Unit 3 status bit is set (i.e. BRK3_STAT≠0).</td> |

</tr> |

<tr> |

<td> </td><td valign="top"><li><b>HWBRK2_PND</b></li></td> |

<td>: This bit reflects if one of the Hardware Breakpoint Unit 2 status bit is set (i.e. BRK2_STAT≠0).</td> |

<td>: This bit reflects if one of the Hardware Breakpoint Unit 2 status bit is set (i.e. BRK2_STAT≠0).</td> |

</tr> |

<tr> |

<td> </td><td valign="top"><li><b>HWBRK1_PND</b></li></td> |

<td>: This bit reflects if one of the Hardware Breakpoint Unit 1 status bit is set (i.e. BRK1_STAT≠0).</td> |

<td>: This bit reflects if one of the Hardware Breakpoint Unit 1 status bit is set (i.e. BRK1_STAT≠0).</td> |

</tr> |

<tr> |

<td> </td><td valign="top"><li><b>HWBRK0_PND</b></li></td> |

<td>: This bit reflects if one of the Hardware Breakpoint Unit 0 status bit is set (i.e. BRK0_STAT≠0).</td> |

<td>: This bit reflects if one of the Hardware Breakpoint Unit 0 status bit is set (i.e. BRK0_STAT≠0).</td> |

</tr> |

<tr> |

<td> </td><td valign="top"><li><b>SWBRK_PND</b></li></td> |

483,7 → 582,61

</td> |

</tr> |

</tbody></table> |

<a name="2.2.4 CPU_NR"></a> |

<h3>2.2.4 CPU_NR</h3> |

|

This 16 bit read only register gives useful information for multi-core systems. |

<br> |

<br> |

|

<table border="1"> |

|

<tbody><tr align="center"> |

<td rowspan="2"><b><small>Register Name</small></b></td> |

<td rowspan="2"><b><small>Address</small></b></td> |

<td colspan="16"><b><small>Bit Field</small></b></td> |

</tr> |

<tr align="center"> |

<td><small>15</small></td><td><small>14</small></td> |

<td><small>13</small></td><td><small>12</small></td> |

<td><small>11</small></td><td><small>10</small></td> |

<td><small> 9</small></td><td><small> 8</small></td> |

<td><small> 7</small></td><td><small> 6</small></td> |

<td><small> 5</small></td><td><small> 4</small></td> |

<td><small> 3</small></td><td><small> 2</small></td> |

<td><small> 1</small></td><td><small> 0</small></td> |

</tr> |

<tr> |

<td style="vertical-align: top; text-align: center;"><small>CPU_NR</small></td> |

<td style="vertical-align: top; text-align: center;"><small>0x18</small></td> |

<td colspan="8" rowspan="1" style="vertical-align: top; text-align: center;"><font size="-5">CPU_TOTAL_NR</font></td> |

<td colspan="8" rowspan="1" style="vertical-align: top; text-align: center;"><font size="-5">CPU_INST_NR</font></td> |

</tr> |

|

|

</tbody> |

</table> |

|

<br> |

|

<table border="0"> |

|

<tbody><tr> |

<td> </td><td valign="top"><li><b>CPU_TOTAL_NR</b></li></td> |

<td>: <span style="color: rgb(0, 0, 0); font-family: 'Times New Roman'; font-style: normal; font-variant: normal; font-weight: normal; letter-spacing: normal; line-height: normal; orphans: 2; text-indent: 0px; text-transform: none; white-space: normal; widows: 2; word-spacing: 0px; font-size: medium; display: inline ! important; float: none;">Total number of oMSP instances -1 (for multicore systems)</span>.</td> |

</tr> |

<tr> |

<td> </td><td valign="top"><li><b>CPU_INST_NR</b></li></td> |

<td>: <span style="color: rgb(0, 0, 0); font-family: 'Times New Roman'; font-style: normal; font-variant: normal; font-weight: normal; letter-spacing: normal; line-height: normal; orphans: 2; text-indent: 0px; text-transform: none; white-space: normal; widows: 2; word-spacing: 0px; font-size: medium; display: inline ! important; float: none;">Current oMSP instance number (for multicore systems)</span>.</td> |

</tr> |

|

|

|

|

|

|

</tbody> |

</table> |

<a name="2.3 Memory Access Registers"></a> |

<div style="text-align: right;"><a href="#TOC">Top</a></div> |

<h2>2.3 Memory Access Registers</h2> |

503,7 → 656,7

<li>set MEM_DATA with the data to be written</li> |

<li>set MEM_CTL (in particular RD/WR=1 and START=1)</li> |

</ol> |

<li>burst read/write access (MEM_CNT≠0):</li> |

<li>burst read/write access (MEM_CNT≠0):</li> |

<ul> |

<li>burst access are optimized for the communication interface used (i.e. for the UART). |

The burst sequence are therefore described in the corresponding section (<a href="#3.4%20Read/Write%20burst%20implementation%20for%20the%20CPU%20Memory%20access">3.4 Read/Write burst implementation for the CPU Memory access</a>)</li> |

577,7 → 730,7

Memory or CPU-Register address to be used for the next read/write |

transfer. After a POR, this register is set to 0x0000. |

<br> |

<strong>Note:</strong> in case of burst (i.e. MEM_CNT≠0), this register |

<strong>Note:</strong> in case of burst (i.e. MEM_CNT≠0), this register |

specifies the first address of the burst transfer and will be |

incremented automatically as the burst goes (by 1 for 8-bit access and |

by 2 for 16-bit access). |

688,7 → 841,7

</tr> |

<tr> |

<td> </td><td> </td> |

<td> ≠0 - |

<td> ≠0 - |

specifies the burst size for the next transfer (i.e number of data |

access). This field will be automatically decremented as the burst goes.</td> |

</tr> |

736,7 → 889,7

</tr> |

<tr> |

<td> </td><td> </td> |

<td> 1 - Address match on BRK_ADDR0→BRK_ADDR1 range (range mode) |

<td> 1 - Address match on BRK_ADDR0→BRK_ADDR1 range (range mode) |

<br><font color="red"><b>Note</b>: range mode is not supported by the core unless the `DBG_HWBRK_RANGE define is set to 1'b1 in the <i>openMSP430_define.v</i> file.</font></td> |

|

</tr> |

806,7 → 959,7

<td> </td><td valign="top"><li><b>RANGE_WR</b></li></td> |

<td>: |

This bit is set whenever the CPU performs a write access within the |

BRKx_ADDR0→BRKx_ADDR1 range (valid if RANGE_MODE=1 and |

BRKx_ADDR0→BRKx_ADDR1 range (valid if RANGE_MODE=1 and |

ACCESS_MODE[1]=1).</td> |

</tr> |

<tr> |

813,7 → 966,7

<td> </td><td valign="top"><li><b>RANGE_RD</b></li></td> |

<td>: |

This bit is set whenever the CPU performs a read access within the |

BRKx_ADDR0→BRKx_ADDR1 range (valid if RANGE_MODE=1 and |

BRKx_ADDR0→BRKx_ADDR1 range (valid if RANGE_MODE=1 and |

ACCESS_MODE[0]=1). <br><font color="red"><b>Note</b>: range mode is not supported by the core unless the `DBG_HWBRK_RANGE define is set to 1'b1 in the <i>openMSP430_define.v</i> file.</font></td> |

</tr> |

<tr> |

919,7 → 1072,7

<h1>3. Debug Communication Interface: UART</h1>With its UART interface, |

the openMSP430 debug unit can communicate with the host computer using |

a simple RS232 cable (connected to the <a href="http://opencores.org/project,openmsp430,core#2.1.5%20Pinout">dbg_uart_txd</a> and <a href="http://opencores.org/project,openmsp430,core#2.1.5%20Pinout">dbg_uart_rxd</a> ports of the IP).<br>Typically, a <a href="http://www.google.com/search?q=usb+to+rs232+converter">USB to RS232</a> or <a href="http://www.ftdichip.com/Products/Cables/USBTTLSerial.htm">USB to serial TTL</a> |

cable will provide a reliable communication link between your host PC |

cable will provides a reliable communication link between your host PC |

and the openMSP430 (speed being typically limited by the cable length). |

<a name="3.1 Serial communication protocol: 8N1"></a> |

<h2>3.1 Serial communication protocol: 8N1</h2> |

1005,5 → 1158,83

<br> |

<img src="usercontent,img,1247430449" alt="Debug Read Burst Transaction" title="Debug Read Burst Transaction"> |

|

<a name="4. Debug Communication Interface: I2C"></a> |

<div style="text-align: right;"><a href="#TOC">Top</a></div> |

<h1>4. Debug Communication Interface: I2C</h1> |

With its I2C interface, the openMSP430 debug unit can communicate with the host computer using |

an I2C adapter (connected to the <a href="http://opencores.org/project,openmsp430,core#2.1.5%20Pinout">dbg_i2c_scl</a> and <a href="http://opencores.org/project,openmsp430,core#2.1.5%20Pinout">dbg_i2c_sda_in / dbg_i2c_sda_out</a> ports of the IP).<br>Currently, the <a href="http://www.robot-electronics.co.uk/acatalog/USB_I2C.html">USB-ISS</a> |

adapter from Devantech (Robot Electronics) is supported by the software |

development tools and provides a reliable communication link between |

your host PC |

and the openMSP430. |

<a name="4.1 I2C communication protocol"></a> |

<h2>4.1 I2C communication protocol</h2> |

There are plenty tutorials on Internet regarding the I2C protocol (see the official <a href="http://www.nxp.com/documents/user_manual/UM10204.pdf">I2C specification</a> for more info).<br> |

A simple byte read or write frame looks as following:<br> |

<br> |

<img src="usercontent,img,1352582784" alt="I2C Protocol" title="I2C Protocol" width="80%"> |

<br><a name="4.2 Synchronization frame"></a> |

<h2>4.2 Synchronization frame</h2> |

Unlike the UART interface, the I2C is a synchronous communication protocol.<br> |

A synchronization frame is therefore not required.<br><br> |

|

<a name="4.3 Read/Write access to the debug registers"></a> |

<h2>4.3 Read/Write access to the debug registers</h2> |

In order to perform a read / write access to a debug register, the host needs to send a command frame to the openMSP430.<br>In |

case of write access, this command frame will be followed by 1 or 2 |

data frames and in case of read access, the openMSP430 will send 1 or 2 |

data frames after receiving the command. |

<a name="4.3.1 Command Frame"></a> |

<h3>4.3.1 Command Frame</h3> |

The command frame looks as following: |

<br> |

<img src="usercontent,img,1352584261" alt="Debug command frame" title="Debug command frame" width="100%"> |

<br> |

<table border="0"> |

<tbody><tr> |

<td> </td><td valign="top"><li><b>WR</b></li></td> |

<td>: Perform a Write access when set. Read otherwise.</td> |

</tr> |

<tr> |

<td> </td><td valign="top"><li><b>B/W</b></li></td> |

<td>: Perform a 8-bit data access when set (one data frame). 16-bit otherwise (two data frame).</td></tr><tr> |

</tr> |

<tr> |

<td> </td><td valign="top"><li><b>Address</b></li></td> |

<td>: Debug register address.</td></tr><tr> |

</tr> |

</tbody></table> |

|

<a name="4.3.2 Write access"></a> |

<h3>4.3.2 Write access</h3> |

A write access transaction looks like this: |

<br> |

<img src="usercontent,img,1352586896" alt="I2C Debug Write Transaction" title="I2C Debug Write Transaction" width="100%"> |

|

<a name="4.3.3 Read access"></a> |

<h3>4.3.3 Read access</h3> |

A read access transaction looks like this: |

<br> |

<img src="usercontent,img,1352586064" alt="I2C Debug Read Transaction" title="I2C Debug Read Transaction" width="100%"> |

|

<a name="4.4 Read/Write burst implementation for the CPU Memory access"></a> |

<h2>4.4 Read/Write burst implementation for the CPU Memory access</h2>In |

order to optimize the data burst transactions for the I2C, read/write |

access are not done by reading or writing the MEM_DATA register.<br> |

Instead, the data transfer starts immediately after the MEM_CTL.START bit has been set. |

|

<a name="4.4.1 Write Burst access"></a> |

<h3>4.4.1 Write Burst access</h3> |

A write burst transaction looks like this: |

<br> |

<img src="usercontent,img,1352673100" alt="I2C Debug Write Burst Transaction" title="I2C Debug Write Burst Transaction" width="100%"> |

|

<a name="4.4.2 Read Burst access"></a> |

<h3>4.4.2 Read Burst access</h3> |

A read burst transaction looks like this: |

<br> |

<img src="usercontent,img,1352672466" alt="I2C Debug Read Burst Transaction" title="I2C Debug Read Burst Transaction" width="100%"> |

|

<div style="text-align: right;"><a href="#TOC">Top</a></div> |

|

</body></html> |

/html/overview.html

1,29 → 1,48

<!DOCTYPE HTML PUBLIC "-//W3C//DTD HTML 4.01//EN" "http://www.w3.org/TR/html4/strict.dtd"> |

<html><head><title>openMSP430 Overview</title></head><body> |

<html><head><title>openMSP430 Overview</title></head> |

<body> |

<table style="text-align: left; width: 100%;" border="0" cellpadding="0" cellspacing="0"> |

<tbody> |

<tr> |

<td style="vertical-align: top;"> |

<h1>Introduction</h1> |

The openMSP430 is a synthesizable 16bit microcontroller core written in Verilog. It is |

compatible with Texas Instruments' <b><a href="http://www.ti.com/litv/pdf/slau049f">MSP430 microcontroller |

family</a></b> and can execute the code generated by any MSP430 toolchain in a near cycle accurate way.<br> |

<br> |

The core comes with some peripherals (<b>16x16 Hardware Multiplier, </b>Watchdog, |

GPIO, TimerA, generic templates) and most notably with a two-wire <b>Serial |

Debug Interface</b> supporting the<b> <a href="http://sourceforge.net/apps/mediawiki/mspgcc/index.php?title=MSPGCC_Wiki" target="_blank">MSPGCC</a> GNU Debugger</b> (GDB) for in-system |

software debugging. <br> |

<br> |

While being fully FPGA friendly, this design is also particularly |

suited for ASIC implementations (typically mixed signal ICs with strong area and low-power requirements).<br> |

In a nutshell, the openMSP430 brings with it:<br> |

<ul> |

<li>Low area (8k-Gates), without hidden extra infrastructure overhead (memory backbone, IRQ controller and watchdog timer are already included).</li> |

<li>Excellent code density.</li> |

<li>Good performances.</li> |

<li>Build-in power and clock managment options.</li> |

<li>Multiple time <span style="font-weight: bold;">Silicon Proven</span>.</li> |

</ul> |

</td> |

<td style="vertical-align: top;"> |

<table border="0" cellpadding="0" cellspacing="0"> |

<tbody> |

<tr><td style="vertical-align: top;"><a href="https://www.paypal.com/cgi-bin/webscr?cmd=_s-xclick&hosted_button_id=QVSEARCQD88FQ"><img alt="donate 8euro" src="http://opencores.org/websvn,filedetails?repname=openmsp430&path=%2Fopenmsp430%2Ftrunk%2Fdoc%2Fhtml%2Fimages%2Fdonate_buttons%2F008_amount_button.png" > </a> </td></tr> |

<tr><td style="vertical-align: top;"><a href="https://www.paypal.com/cgi-bin/webscr?cmd=_s-xclick&hosted_button_id=SD9F58JAMB8XA"><img alt="donate 16euro" src="http://opencores.org/websvn,filedetails?repname=openmsp430&path=%2Fopenmsp430%2Ftrunk%2Fdoc%2Fhtml%2Fimages%2Fdonate_buttons%2F016_amount_button.png" > </a> </td></tr> |

<tr><td style="vertical-align: top;"><a href="https://www.paypal.com/cgi-bin/webscr?cmd=_s-xclick&hosted_button_id=K2VBGQU7C4ZQY"><img alt="donate 32euro" src="http://opencores.org/websvn,filedetails?repname=openmsp430&path=%2Fopenmsp430%2Ftrunk%2Fdoc%2Fhtml%2Fimages%2Fdonate_buttons%2F032_chip_button_paypal.png" > </a> </td></tr> |

<tr><td style="vertical-align: top;"><a href="https://www.paypal.com/cgi-bin/webscr?cmd=_s-xclick&hosted_button_id=6CQD25UJLD2CY"><img alt="donate 64euro" src="http://opencores.org/websvn,filedetails?repname=openmsp430&path=%2Fopenmsp430%2Ftrunk%2Fdoc%2Fhtml%2Fimages%2Fdonate_buttons%2F064_amount_button.png" > </a> </td></tr> |

<tr><td style="vertical-align: top;"><a href="https://www.paypal.com/cgi-bin/webscr?cmd=_s-xclick&hosted_button_id=EQFEFFJZFCXBW"><img alt="donate 128euro" src="http://opencores.org/websvn,filedetails?repname=openmsp430&path=%2Fopenmsp430%2Ftrunk%2Fdoc%2Fhtml%2Fimages%2Fdonate_buttons%2F128_amount_button.png" > </a> </td></tr> |

<tr><td style="vertical-align: top;"><a href="https://www.paypal.com/cgi-bin/webscr?cmd=_s-xclick&hosted_button_id=MG8M87BXDL3K8"><img alt="donate XXXeuro" src="http://opencores.org/websvn,filedetails?repname=openmsp430&path=%2Fopenmsp430%2Ftrunk%2Fdoc%2Fhtml%2Fimages%2Fdonate_buttons%2F000_amount_button.png" > </a> </td></tr> |

</tbody> |

</table> |

</td> |

</tr> |

</tbody> |

</table> |

<br> |

<h1>Introduction</h1> |

|

The openMSP430 is a synthesizable 16bit microcontroller core written in Verilog. It is compatible with Texas Instruments' <b><a href="http://www.ti.com/litv/pdf/slau049f">MSP430 microcontroller family</a></b> and can execute the code generated by any MSP430 toolchain in a near cycle accurate way.<br><br> |

The core comes with some peripherals (<b>16x16 Hardware Multiplier, </b>Watchdog, GPIO, TimerA, generic templates) and most notably with a two-wire <b>Serial Debug Interface</b> supporting the<b> <a href="http://sourceforge.net/apps/mediawiki/mspgcc/index.php?title=MSPGCC_Wiki" target="_blank">MSPGCC</a> GNU Debugger</b> (GDB) for in-system software debugging. |

<br><br> |

While being fully FPGA friendly, this design is also particularly |

suited for ASIC implementations (typically mixed signal ICs with strong area |

and low-power requirements).<br> |

In a nutshell, the openMSP430 brings with it:<br> |

<ul> |

|

<li>Low area (8k-Gates), without hidden extra infrastructure |

overhead (memory backbone, IRQ controller and watchdog timer are already |

included).</li> |

|

<li>Excellent code density.</li> |

<li>Good performances.</li> |

|

<li>Build-in power and clock managment options.</li> |

<li>Multiple time <span style="font-weight: bold;">Silicon Proven</span>.<br> |

</li> |

</ul> |

|

<h1>Download</h1> |

<h3>Design</h3> |

The complete tar archive of the project can be downloaded <a href="http://www.opencores.org/download,openmsp430">here</a> (OpenCores account required).<br> |

65,7 → 84,7

<li>Power saving modes.</li> |

<li>Configurable memory size for both program and data.</li> |

<li>Scalable peripheral address space.</li> |

<li>Two-wire Serial Debug Interface (Nexus class 3, w/o trace) with GDB support.</li> |

<li>Two-wire Serial Debug Interface (Nexus class 3, w/o trace) with GDB support (I<sup>2</sup>C or UART based).</li> |

<li>FPGA friendly (option for single clock domain, no clock gate).</li> |

<li>ASIC friendly (options for full power & clock management support).<br> |

</li> |

/html/core.html

1,5 → 1,6

<!DOCTYPE HTML PUBLIC "-//W3C//DTD HTML 4.01//EN" "http://www.w3.org/TR/html4/strict.dtd"> |

<html><head><title>openMSP430 Core</title></head><body> |

<html><head><title>openMSP430 Core</title></head> |

<body> |

<h3>Table of content</h3> |

<ul> |

<li><a href="#1.%20Introduction">1. Introduction</a></li> |

11,14 → 12,20

<li><a href="#2.1.2%20Limitations"> 2.1.2 Limitations</a></li> |

<li><a href="#2.1.3%20Configuration"> 2.1.3 Configuration</a></li> |

<ul> |

<li><a href="#2.1.3.1%20Basic%20System%20Configuration"> 2.1.3.1 Basic System Configuration</a></li> |

<li><a href="#2.1.3.2%20Advanced%20System%20Configuration"> 2.1.3.2 Advanced System Configuration</a></li> |

<li><a href="#2.1.3.3%20Expert%20System%20Configuration"> 2.1.3.3 Expert System Configuration</a></li> |

<li><a href="#2.1.3.1%20Basic%20System%20Configuration"> 2.1.3.1 Basic System Configuration</a></li> |

<li><a href="#2.1.3.2%20Advanced%20System%20Configuration"> 2.1.3.2 Advanced System Configuration</a></li> |

<li><a href="#2.1.3.3%20Expert%20System%20Configuration"> 2.1.3.3 Expert System Configuration</a></li> |

<li><a href="#2.1.3.4%20Parameters%20For%20Multi-Core%20Systems"> 2.1.3.4 Parameters For Multi-Core Systems</a></li> |

</ul> |

<li><a href="#2.1.4%20Memory%20mapping"> 2.1.4 Memory mapping</a></li> |

<li><a href="#2.1.5%20Pinout"> 2.1.5 Pinout</a></li> |

<li><a href="#2.1.6%20Instruction%20Cycles%20and%20Lengths">2.1.6 Instruction Cycles and Lengths</a></li> |

<li><a href="#2.1.7%20Serial%20Debug%20Interface"> 2.1.7 Serial Debug Interface</a></li> |

<li><a href="#2.1.8%20Benchmark%20results"> 2.1.8 Benchmark results</a></li> |

<ul> |

<li><a href="#2.1.8.1%20Dhrystone">2.1.8.1 Dhrystone</a></li> |

<li><a href="#2.1.8.2%20CoreMark">2.1.8.2 CoreMark</a></li> |

</ul> |

</ul> |

</li> |

<li><a href="#2.2_System_Peripherals"> 2.2 System Peripherals</a> |

88,7 → 95,7

|

The following diagram shows the openMSP430 design structure: |

<br><br> |

<img src="usercontent,img,1267738921" alt="CPU Structure" title="CPU Structure" width="80%"> |

<img src="http://opencores.org/usercontent,img,1354053264" alt="CPU Structure" title="CPU Structure" width="80%"> |

<br> |

<ul> |

<li><b>Frontend</b>: This module performs the instruction Fetch and Decode tasks. It also contains the execution state machine.</li> |

97,8 → 104,8

current decoded instruction according to the execution state.</li> |

<li><b>Serial Debug Interface</b>: |

Contains all the required logic for a Nexus class 3 debugging unit |

(without trace). Communication with the host is done with a standard |

two-wire 8N1 serial interface.</li> |

(without trace). Communication with the host is performed with a standard |

two-wire interface following either the UART 8N1 or I<sup>2</sup>C serial protocol.</li> |

<li><b>Memory backbone</b>: This block |

performs a simple arbitration between the frontend and execution-unit |

for program, data and peripheral memory access.</li> |

159,6 → 166,7

// |

Uncomment the required memory size<br> |

//-------------------------------------------------------<br> |

//`define PMEM_SIZE_CUSTOM<br> |

//`define PMEM_SIZE_59_KB<br> |

//`define PMEM_SIZE_55_KB<br> |

//`define PMEM_SIZE_54_KB<br> |

179,6 → 187,7

// |

Uncomment the required memory size<br> |

//-------------------------------------------------------<br> |

//`define DMEM_SIZE_CUSTOM<br> |

//`define DMEM_SIZE_32_KB<br> |

//`define DMEM_SIZE_24_KB<br> |

//`define DMEM_SIZE_16_KB<br> |

207,6 → 216,9

<li>The sum of program, data and peripheral memory space <b>MUST NOT</b> exceed 64 kB</li> |

</ul> |

<br> |

<b><u>Note:</u></b> when selected, custom memory sizes can be specified in the "Expert System Configuration" section. |

<br> |

<br> |

|

<a name="2.1.3.2 Advanced System Configuration"></a> |

<h4>2.1.3.2 Advanced System Configuration</h4> |

288,6 → 300,7

// shifted up and a custom linker script will therefore<br> |

// be required by the GCC compiler.<br> |

//-------------------------------------------------------<br> |

//`define PER_SIZE_CUSTOM<br> |

//`define PER_SIZE_32_KB<br> |

//`define PER_SIZE_16_KB<br> |

//`define PER_SIZE_8_KB<br> |

317,6 → 330,9

<li>The sum of program, data and peripheral memory space <b>MUST NOT</b> exceed 64 kB</li> |

</ul> |

<br> |

<b><u>Note:</u></b> when selected, custom peripheral memory space can be specified in the "Expert System Configuration" section. |

<br> |

<br> |

<a name="2.1.3.3 Expert System Configuration"></a> |

<h4>2.1.3.3 Expert System Configuration</h4> |

In this section, you will find configuration options which are |

345,6 → 361,29

//<br> |

//============================================================================<br> |

<br> |

//-------------------------------------------------------<br> |

// Select serial debug interface protocol<br> |

//-------------------------------------------------------<br> |

// DBG_UART -> Enable UART (8N1) debug interface<br> |

// DBG_I2C -> Enable I2C debug interface<br> |

//-------------------------------------------------------<br> |

`define DBG_UART<br> |

//`define DBG_I2C<br> |

<br> |

<br> |

//-------------------------------------------------------<br> |

// Enable the I2C broadcast address<br> |

//-------------------------------------------------------<br> |

// For multicore systems, a common I2C broadcast address<br> |

// can be given to all oMSP cores in order to<br> |

// synchronously RESET, START, STOP, or STEP all CPUs<br> |

// at once with a single I2C command.<br> |

// If you have a single openMSP430 in your system,<br> |

// this option can stay commented-out.<br> |

//-------------------------------------------------------<br> |

//`define DBG_I2C_BROADCAST<br> |

<br> |

<br> |

//-------------------------------------------------------<br>// Number of hardware breakpoint/watchpoint units<br> |

// (each unit contains two hardware addresses available<br> |

// for breakpoints or watchpoints):<br> |

376,6 → 415,31

<br> |

<br> |

//-------------------------------------------------------<br> |

// Custom Program/Data and Peripheral Memory Spaces<br> |

//-------------------------------------------------------<br> |

// The following values are valid only if the<br> |

// corresponding *_SIZE_CUSTOM defines are uncommented:<br> |

//<br> |

// - *_SIZE : size of the section in bytes.<br> |

// - *_AWIDTH : address port width, this value must allow<br> |

// to address all WORDS of the section<br> |

// (i.e. the *_SIZE divided by 2)<br> |

//-------------------------------------------------------<br> |

<br> |

// Custom Program memory (enabled with PMEM_SIZE_CUSTOM)<br> |

`define PMEM_CUSTOM_AWIDTH 10<br> |

`define PMEM_CUSTOM_SIZE 2048<br> |

<br> |

// Custom Data memory (enabled with DMEM_SIZE_CUSTOM)<br> |

`define DMEM_CUSTOM_AWIDTH 6<br> |

`define DMEM_CUSTOM_SIZE 128<br> |

<br> |

// Custom Peripheral memory (enabled with PER_SIZE_CUSTOM)<br> |

`define PER_CUSTOM_AWIDTH 8<br> |

`define PER_CUSTOM_SIZE 512<br> |

<br> |

<br> |

//-------------------------------------------------------<br> |

// ASIC version<br> |

//-------------------------------------------------------<br> |

// When uncommented, this define will enable the<br> |

392,7 → 456,61

</ul> |

<br> |

All remaining defines located after the ASIC section in the <b><i>openMSP430_defines.v</i></b> file are system constants and <b>MUST NOT</b> be edited. |

<br> |

<br> |

<a name="2.1.3.4 Parameters For Multi-Core Systems"></a> |

<h4>2.1.3.4 Parameters For Multi-Core Systems</h4> |

|

In addition to the define file, two Verilog parameters are available to facilitate software development on multi-core systems.<br> |

For example, in a dual-core openMSP430 system, the cores can be instantiated as following: |

<br> |

<br> |

<table border="0" cellpadding="0" cellspacing="4"> |

<tbody><tr> |

<td width="35"><br></td> |

<td bgcolor="#d0d0d0" width="3"><br></td> |

<td width="15"><br></td> |

<td> |

<code> |

openMSP430 #(.INST_NR (<strong>0</strong>), .TOTAL_NR(<strong>1</strong>)) openMSP430_core_0 ( |

<br>... |

<br>); |

<br> |

<br>openMSP430 #(.INST_NR (<strong>1</strong>), .TOTAL_NR(<strong>1</strong>)) openMSP430_core_1 ( |

<br>... |

<br>); |

</code> |

</td> |

</tr> |

</tbody> |

</table> |

<br> |

The values of these parameters are then directly accessible through the CPU_NR register of the SFR peripheral.<br> |

For example, if both cores share the same program memory, the software can take advantage of this information as following: |

<br><br> |

<table border="0" cellpadding="0" cellspacing="4"> |

<tbody><tr> |

<td width="35"><br></td> |

<td bgcolor="#d0d0d0" width="3"><br></td> |

<td width="15"><br></td> |

<td> |

<code> |

"... |

<br>int main(void) { |

<br> if (CPU_NR==<strong>0x0100</strong>) { |

<br> main_core_0(); // Main routine call for core 0 |

<br> } |

<br> if (CPU_NR==<strong>0x0101</strong>) { |

<br> main_core_1(); // Main routine call for core 1 |

<br> } |

<br>} |

<br>..." |

</code> |

</td> |

</tr> |

</tbody> |

</table> |

<br><br> |

|

<a name="2.1.4 Memory mapping"></a> |

<h3>2.1.4 Memory mapping</h3> |

780,7 → 898,50

<td style="vertical-align: top; text-align: center;"><async><br> |

</td> |

<td> Debug interface: UART RXD (asynchronous) </td> |

</tr><tr align="center"> |

</tr><tr> |

<td style="vertical-align: top;">dbg_i2c_addr<br> |

</td> |

<td style="vertical-align: top;"> Input</td> |

<td style="vertical-align: top;"> 7</td> |

<td style="vertical-align: top; text-align: center;">mclk</td> |

<td style="vertical-align: top;">Debug interface: I2C Address<br> |

</td> |

</tr> |

<tr> |

<td style="vertical-align: top;">dbg_i2c_broadcast<br> |

</td> |

<td style="vertical-align: top;"> Input</td> |

<td style="vertical-align: top;"> 7</td> |

<td style="vertical-align: top; text-align: center;">mclk</td> |

<td style="vertical-align: top;">Debug interface: I2C Broadcast Address (for multicore systems)<br> |

</td> |

</tr> |

<tr> |

<td style="vertical-align: top;">dbg_i2c_scl<br> |

</td> |

<td style="vertical-align: top;"> Input</td> |

<td style="vertical-align: top;"> 1</td> |

<td style="vertical-align: top; text-align: center;"><async></td> |

<td style="vertical-align: top;">Debug interface: I2C SCL (asynchronous)</td> |

</tr> |

<tr> |

<td style="vertical-align: top;">dbg_i2c_sda_in<br> |

</td> |

<td style="vertical-align: top;"> Input</td> |

<td style="vertical-align: top;"> 1</td> |

<td style="vertical-align: top; text-align: center;"><async></td> |

<td style="vertical-align: top;">Debug interface: I2C SDA IN (asynchronous)</td> |

</tr> |

<tr> |

<td style="vertical-align: top;">dbg_i2c_sda_out<br> |

</td> |

<td style="vertical-align: top;"> Output</td> |

<td style="vertical-align: top;"> 1</td> |

<td style="vertical-align: top; text-align: center;">mclk</td> |

<td style="vertical-align: top;">Debug interface: I2C SDA OUT<br> |

</td> |

</tr> |

<tr align="center"> |

<td colspan="5" rowspan="1" style="vertical-align: top;"><b><i>Scan</i></b></td> |

</tr> |

<tr> |

910,6 → 1071,101

|

All the details about the Serial Debug Interface are located <a href="http://opencores.org/project,openmsp430,serial%20debug%20interface">here</a>.<br> |

<br> |

|

<a name="2.1.8 Benchmark results"></a> |

<h3>2.1.8 Benchmark results</h3> |

|

<a name="2.1.8.1 Dhrystone"></a> |

<h4>2.1.8.1 Dhrystone (DMIPS/MHz)</h4> |

Dhrystone is known for being susceptible to compiler optimizations (among other issues).<br>However, |

as it is still quite a popular metric, some results are provided here |

(ranging from 0.30 to 0.45 DMIPS/MHz depending on the compiler version |

and options).<br> |

Note that the used C-code is available in the repository <a href="http://opencores.org/websvn,listing?repname=openmsp430&path=%2Fopenmsp430%2Ftrunk%2Fcore%2Fsim%2Frtl_sim%2Fsrc-c%2Fdhrystone_v2.1%2F#path_openmsp430_trunk_core_sim_rtl_sim_src-c_dhrystone_v2.1_">here</a> and <a href="http://opencores.org/websvn,listing?repname=openmsp430&path=%2Fopenmsp430%2Ftrunk%2Fcore%2Fsim%2Frtl_sim%2Fsrc-c%2Fdhrystone_4mcu%2F#path_openmsp430_trunk_core_sim_rtl_sim_src-c_dhrystone_4mcu_">here</a>.<br> |

<br> |

|

<table style="text-align: left; width: 40%;" border="1" cellpadding="2" cellspacing="2"> |

<tbody> |

<tr> |

<td style="text-align: center;" colspan="1" rowspan="2"><span style="font-weight: bold;">Dhrystone flavor</span></td> |

<td style="font-weight: bold; text-align: right;">Compiler options</td> |

<td colspan="1" rowspan="2" style="vertical-align: top; text-align: center; font-weight: bold;">-Os</td> |

<td colspan="1" rowspan="2" style="vertical-align: top; text-align: center; font-weight: bold;">-O2</td> |

<td colspan="1" rowspan="2" style="vertical-align: top; text-align: center; font-weight: bold;">-O3</td> |

</tr> |

<tr align="left"> |

<td style="font-weight: bold;">Compiler version |

</td> |

</tr> |

<tr> |

<td style="text-align: center;" colspan="1" rowspan="2">Dhrystone v2.1<br> |

(<a href="http://ftp.unicamp.br/pub/unix-c/benchmark/system/">common version</a>)</td> |

<td style="text-align: left;">mspgcc v4.4.5</td> |

<td style="text-align: center;">0.30</td> |

<td style="text-align: center;">0.32</td> |

<td style="text-align: center;">0.33</td> |

</tr> |

<tr> |

<td style="text-align: left;">mspgcc v4.6.3</td> |

<td style="text-align: center;">0.37</td> |

<td style="text-align: center;">0.39</td> |

<td style="text-align: center;">0.40</td> |

</tr> |

<tr> |

<td style="text-align: center;" colspan="1" rowspan="2">Dhrystone v2.1<br> |

(<a href="http://www.ecrostech.com/Other/Resources/Dhrystone.htm">MCU adapted</a>)</td> |

<td style="text-align: left;">mspgcc v4.4.5</td> |

<td style="text-align: center;">0.30</td> |

<td style="text-align: center;">0.30</td> |

<td style="text-align: center;">0.31</td> |

</tr> |

<tr> |

<td style="text-align: left;">mspgcc v4.6.3</td> |

<td style="text-align: center;">0.37</td> |

<td style="text-align: center;">0.44</td> |

<td style="text-align: center;">0.45</td> |

</tr> |

</tbody> |

</table> |

|

<a name="2.1.8.2 CoreMark"></a> |

<h4>2.1.8.2 CoreMark (CoreMark/MHz)</h4> |

CoreMark tries to address most of Dhrystone's pitfall by preventing the |

compiler to optimize some code away and using "real-life" algorithm.<br> |

Note that the used C-code is available in the repository <a href="http://opencores.org/websvn,listing?repname=openmsp430&path=%2Fopenmsp430%2Ftrunk%2Fcore%2Fsim%2Frtl_sim%2Fsrc-c%2Fcoremark_v1.0%2F#path_openmsp430_trunk_core_sim_rtl_sim_src-c_coremark_v1.0_">here</a>.<br> |

<br> |

|

<table style="text-align: left; width: 40%;" border="1" cellpadding="2" cellspacing="2"> |

<tbody> |

<tr> |

<td style="text-align: center;" colspan="1" rowspan="2"><br> |

</td> |

<td style="font-weight: bold; text-align: right;">Compiler options</td> |

<td colspan="1" rowspan="2" style="vertical-align: top; text-align: center; font-weight: bold;">-Os</td> |

<td colspan="1" rowspan="2" style="vertical-align: top; text-align: center; font-weight: bold;">-O2</td> |

<td colspan="1" rowspan="2" style="vertical-align: top; text-align: center; font-weight: bold;">-O3</td> |

</tr> |

<tr align="left"> |

<td style="font-weight: bold;">Compiler version</td> |

</tr> |

<tr> |

<td style="text-align: center;" colspan="1" rowspan="2">CoreMark v1.0<br> |

(<a href="http://www.coremark.org/">official version</a>)</td> |

<td style="text-align: left;">mspgcc v4.4.5</td> |

<td style="text-align: center;">0.78</td> |

<td style="text-align: center;">0.85</td> |

<td style="text-align: center;">0.83</td> |

</tr> |

<tr> |

<td style="text-align: left;">mspgcc v4.6.3</td> |

<td style="text-align: center;">0.74</td> |

<td style="text-align: center;">0.91</td> |

<td style="text-align: center;">0.87</td> |

</tr> |

</tbody> |

</table> |

<br> |

|

<a name="2.2_System_Peripherals"></a> |

<h2>2.2 System Peripherals</h2> |

In addition to the CPU core itself, several peripherals are also |

1066,7 → 1322,7

<b><sup><font color="#ff0000">1</font></sup></b>: These fields are not available if the NMI is excluded (see <i>openMSP430_defines.v</i> )<br> |

<b><sup><font color="#ff0000">2</font></sup></b>: These fields are not available if the Watchdog is excluded (see <i>openMSP430_defines.v</i> )<br> |

<br> |

In addition, two 16-bit read-only registers have been added in order |

In addition, three 16-bit read-only registers have been added in order |

to let the software know with which version of the openMSP430 it is |

running:<br> |

<br> |

1101,7 → 1357,13

<td colspan="6"><font size="-5">PMEM_SIZE</font></td> |

<td colspan="9"><font size="-5">DMEM_SIZE</font></td> |

<td colspan="1"><font size="-5">MPY</font></td> |

</tr> |

</tr><tr> |

<td style="vertical-align: top; text-align: center;"><small>CPU_NR</small></td> |

<td style="vertical-align: top; text-align: center;"><small>0x0008</small></td> |

<td colspan="8" rowspan="1" style="vertical-align: top; text-align: center;"><font size="-5">CPU_TOTAL_NR</font></td> |

<td colspan="8" rowspan="1" style="vertical-align: top; text-align: center;"><font size="-5">CPU_INST_NR</font></td> |

</tr> |

|

</tbody> |

</table> |

<br> |

1136,10 → 1398,18

<td> </td><td valign="top"><li><b>PMEM_SIZE</b></li></td> |

<td>: Progam memory size for the current implementation (byte size = PMEM_SIZE*1024)</td> |

</tr> |

<tr> |

<td> </td><td valign="top"><li><b>CPU_INST_NR</b></li></td> |

<td>: Current oMSP instance number (for multicore systems)</td> |

</tr> |

<tr> |

<td> </td><td valign="top"><li><b>CPU_TOTAL_NR</b></li></td> |

<td>: Total number of oMSP instances-1 (for multicore systems)</td> |

</tr> |

</tbody> |

</table> |

<br> |

<span style="font-weight: bold; text-decoration: underline;">Note:</span> attentive readers will have noted that <span style="font-style: italic;">CPU_ID_LO</span> and <span style="font-style: italic;">CPU_ID_HI</span> are identical to the Serial Debug Interface register counterparts.<br> |

<span style="font-weight: bold; text-decoration: underline;">Note:</span> attentive readers will have noted that <span style="font-style: italic;">CPU_ID_LO</span>, <span style="font-style: italic;">CPU_ID_HI</span> and <span style="font-style: italic;">CPU_NR</span> are identical to the Serial Debug Interface register counterparts.<br> |

<a name="2.2.2 Watchdog Timer"></a> |

<h3>2.2.4 Watchdog Timer</h3> |

|

/html/files_directory_description.html

26,14 → 26,26

|

<table border="1"> |

<tbody><tr><td colspan="5"><b>core</b></td> <td><i><b>openMSP430 Core top level directory</b></i></td></tr> |

<tr><td rowspan="107" valign="bottom"><font color="white">abcd</font></td> <td colspan="4"><b>bench</b></td> <td><i><b>Top level testbench directory</b></i></td></tr> |

<tr><td rowspan="7" valign="bottom"><font color="white">abcd</font></td> <td colspan="3"><b>verilog</b></td> <td><i></i><br> |

<tr><td rowspan="120" valign="bottom"><font color="white">abcd</font></td> <td colspan="4"><b>bench</b></td> <td><i><b>Top level testbench directory</b></i></td></tr> |

<tr><td rowspan="9" valign="bottom"><font color="white">abcd</font></td> <td colspan="3"><b>verilog</b></td> <td><i></i><br> |

</td></tr> |

<tr><td rowspan="6" valign="bottom"><font color="white">abcd</font></td> <td colspan="2">tb_openMSP430.v</td> <td><i>Testbench top level module</i></td></tr> |

<tr><td rowspan="8" valign="bottom"><font color="white">abcd</font></td> <td colspan="2">tb_openMSP430.v</td> <td><i>Testbench top level module</i></td></tr> |

<tr><td colspan="2">ram.v</td> <td><i>RAM verilog model</i></td></tr> |

<tr><td colspan="2">registers.v</td> <td><i>Connections to Core internals for easy debugging</i></td></tr> |

<tr><td colspan="2">dbg_uart_tasks.v</td> <td><i>UART tasks for the serial debug interface</i></td></tr> |

<tr> |

<td colspan="2" rowspan="1" style="vertical-align: top;">dbg_i2c_tasks.v<br> |

</td> |

<td style="vertical-align: top;"><span style="font-style: italic;">I2C tasks for the serial debug interface</span><br> |

</td> |

</tr> |

<tr> |

<td colspan="2" rowspan="1" style="vertical-align: top;">io_cell.v<br> |

</td> |

<td style="vertical-align: top;"><span style="font-style: italic;">Generic I/O cell model for building the serial debug interface I2C bus</span><br> |

</td> |

</tr> |

<tr> |

<td colspan="2" rowspan="1" style="vertical-align: top;">msp_debug.v</td> |

<td style="vertical-align: top;"><i>Testbench instruction decoder and ASCII chain generator for easy debugging</i></td> |

</tr> |

41,9 → 53,9

<tr><td colspan="4"><b>doc</b></td> <td><i><b>Diverse documentation</b></i></td></tr> |

<tr><td><font color="white">abcd</font></td> <td colspan="3">slau049f.pdf</td> <td><i>MSP430x1xx Family User's Guide</i></td></tr> |

<tr><td colspan="4"><b>rtl</b></td> <td><i><b>RTL sources</b></i></td></tr> |

<tr><td rowspan="30" valign="bottom"><font color="white">abcd</font></td><td colspan="3"><b>verilog</b></td> <td><i></i><br> |

<tr><td rowspan="31" valign="bottom"><font color="white">abcd</font></td><td colspan="3"><b>verilog</b></td> <td><i></i><br> |

</td></tr> |

<tr><td rowspan="29" valign="bottom"><font color="white">abcd</font></td> <td colspan="2">openMSP430_defines.v</td> <td><i>openMSP430 core configuration file (Program and Data memory size definition, Debug Interface configuration, ...)</i></td></tr> |

<tr><td rowspan="30" valign="bottom"><font color="white">abcd</font></td> <td colspan="2">openMSP430_defines.v</td> <td><i>openMSP430 core configuration file (Program and Data memory size definition, Debug Interface configuration, ...)</i></td></tr> |

<tr><td colspan="2">openMSP430_undefines.v</td> <td><i>openMSP430 Verilog `undef file</i></td></tr> |

<tr><td colspan="2">openMSP430.v</td> <td><i>openMSP430 top level</i></td></tr> |

<tr><td colspan="2">omsp_frontend.v</td> <td><i>Instruction fetch and decode</i></td></tr> |

59,6 → 71,12

<tr><td colspan="2">omsp_dbg_hwbrk.v</td> <td><i>Serial Debug Interface hardware breakpoint unit</i></td></tr> |

<tr><td colspan="2">omsp_dbg_uart.v</td> <td><i>Serial Debug Interface UART communication block</i></td></tr> |

<tr> |

<td colspan="2" rowspan="1" style="vertical-align: top;">omsp_dbg_i2c.v<br> |

</td> |

<td style="vertical-align: top;"><span style="font-style: italic;">Serial Debug Interface I2C communication block</span><br> |

</td> |

</tr> |

<tr> |

<td colspan="2" rowspan="1" style="vertical-align: top;">omsp_sync_cell.v</td> |

<td style="vertical-align: top;"><i>Simple synchronization module (double flip-flop).</i></td> |

</tr> |

107,9 → 125,11

<tr><td colspan="1">template_periph_16b.v</td> <td><i>Verilog template for 16 bit peripherals</i></td></tr> |

<tr><td colspan="1">template_periph_8b.v</td> <td><i>Verilog template for 8 bit peripherals</i></td></tr> |

<tr><td colspan="4"><b>sim</b></td> <td><i><b>Top level simulations directory</b></i></td></tr> |

<tr><td rowspan="54" valign="bottom"><font color="white">abcd</font></td> <td colspan="3"><b>rtl_sim</b></td> <td><i><b>RTL simulations</b></i></td></tr> |

<tr><td rowspan="53" valign="bottom"><font color="white">abcd</font></td> <td colspan="2"><b>bin</b></td> <td><i><b>RTL simulation scripts</b></i></td></tr> |

<tr><td rowspan="6" valign="bottom"><font color="white">abcd</font></td> <td colspan="1">msp430sim</td> <td><i>Main simulation script for assembler vector sources (located in the <span style="font-weight: bold;">src</span> directory)<br> |

<tr><td colspan="1" rowspan="62" valign="bottom"><font color="white">abcd</font></td> <td colspan="3"><b>rtl_sim</b></td> <td><i><b>RTL simulations</b></i></td></tr> |

<tr><td colspan="1" rowspan="61" valign="bottom"><font color="white">abcd</font></td> <td colspan="2"><b>bin</b></td> <td><i><b>RTL simulation scripts</b></i></td></tr> |

<tr><td colspan="1" rowspan="10" valign="bottom"><font color="white">abcd</font><br> |

|

</td> <td colspan="1">msp430sim</td> <td><i>Main simulation script for assembler vector sources (located in the <span style="font-weight: bold;">src</span> directory)<br> |

</i></td></tr> |

<tr> |

<td style="vertical-align: top;">msp430sim_c<br> |

121,8 → 141,25

<tr><td colspan="1">rtlsim.sh</td> <td><i>Verilog Icarus simulation script</i></td></tr> |

<tr><td colspan="1">template.x</td> <td><i>ASM linker definition file template</i></td></tr> |

<tr> |

<td style="vertical-align: top;"><br> |

<td style="vertical-align: top;">template_defs.asm<br> |

</td> |

<td style="vertical-align: top;"><span style="font-style: italic;">Common ASM definition file included in all ".s43" files</span><br> |

</td> |

</tr> |

<tr> |

<td style="vertical-align: top;">omsp_config.sh<br> |

</td> |

<td style="vertical-align: top;"><span style="font-style: italic;">oMSP configuration file.</span><br> |

</td> |

</tr> |

<tr> |

<td style="vertical-align: top;">parse_results<br> |

</td> |

<td style="vertical-align: top;"><span style="font-style: italic;">Script parsing regression log files and generating summary report.</span><br> |

</td> |

</tr> |

<tr> |

|

<td style="vertical-align: top;">cov_*<br> |

</td> |

<td style="vertical-align: top;"><span style="font-style: italic;">Code coverage scripts for NC-Verilog and ICM</span><br> |

150,7 → 187,8

</td> |

</tr> |

<tr><td colspan="1">load_waveform.sav</td> <td><i>SAV file for gtkWave</i></td></tr> |