| Line 5... |

Line 5... |

[](https://github.com/stnolting/neorv32/releases)

|

[](https://github.com/stnolting/neorv32/releases)

|

|

|

|

|

## Table of Content

|

## Table of Content

|

|

|

* [Introduction](#Introduction)

|

* [Overview](#Overview)

|

|

* [Project Status](#Status)

|

* [Features](#Features)

|

* [Features](#Features)

|

* [FPGA Implementation Results](#FPGA-Implementation-Results)

|

* [FPGA Implementation Results](#FPGA-Implementation-Results)

|

* [Performance](#Performance)

|

* [Performance](#Performance)

|

* [Top Entities](#Top-Entities)

|

* [Top Entities](#Top-Entities)

|

* [**Getting Started**](#Getting-Started)

|

* [**Getting Started**](#Getting-Started)

|

* [Contribute](#Contribute)

|

* [Contribute](#Contribute)

|

* [Legal](#Legal)

|

* [Legal](#Legal)

|

|

|

|

|

|

|

## Introduction

|

## Overview

|

|

|

The NEORV32 Processor is a customizable microcontroller-like system on chip (SoC) that is based

|

The NEORV32 Processor is a customizable microcontroller-like system on chip (SoC) that is based

|

on the RISC-V-compliant NEORV32 CPU. The project consists of two main parts:

|

on the RISC-V-compliant NEORV32 CPU. The project consists of two main parts:

|

|

|

|

|

| Line 35... |

Line 36... |

stand-alone mode and build your own SoC around it.

|

stand-alone mode and build your own SoC around it.

|

|

|

|

|

### [NEORV32 Processor](#Processor-Features)

|

### [NEORV32 Processor](#Processor-Features)

|

|

|

Based on the NEORV32 CPU, the NEORV32 Processor is a full-scale RISC-V microcontroller system

|

Based on the NEORV32 CPU, the NEORV32 Processor is a full-scale RISC-V microcontroller system (**SoC**)

|

that already provides common peripherals like GPIO, serial interfaces, timers, embedded

|

that already provides common peripherals like GPIO, serial interfaces, timers, embedded

|

memories and an external bus interface for connectivity and custom extension.

|

memories and an external bus interface for connectivity and custom extension.

|

All optional features and modules beyond the base CPU can be enabled and configured via

|

All optional features and modules beyond the base CPU can be enabled and configured via

|

[VHDL generics](#Top-Entities).

|

[VHDL generics](#Top-Entities).

|

|

|

| Line 64... |

Line 65... |

For more information take a look at the [ NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf).

|

For more information take a look at the [ NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf).

|

|

|

|

|

### Key Features

|

### Key Features

|

|

|

- RISC-V-compliant `rv32i` CPU with optional `C`, `E`, `M`, `U`, `Zicsr`, `Zifencei` and `PMP` (physical memory protection) extensions

|

* RISC-V-compliant `rv32i` CPU with optional `C`, `E`, `M`, `U`, `Zicsr`, `Zifencei` and `PMP` (physical memory protection) extensions

|

- GCC-based toolchain ([pre-compiled rv32i and rv32e toolchains available](https://github.com/stnolting/riscv_gcc_prebuilt))

|

* GCC-based toolchain ([pre-compiled rv32i and rv32e toolchains available](https://github.com/stnolting/riscv_gcc_prebuilt))

|

- Application compilation based on [GNU makefiles](https://github.com/stnolting/neorv32/blob/master/sw/example/blink_led/makefile)

|

* Application compilation based on [GNU makefiles](https://github.com/stnolting/neorv32/blob/master/sw/example/blink_led/makefile)

|

- [Doxygen-based](https://github.com/stnolting/neorv32/blob/master/docs/doxygen_makefile_sw) documentation of the software framework: available on [GitHub pages](https://stnolting.github.io/neorv32/files.html)

|

* [Doxygen-based](https://github.com/stnolting/neorv32/blob/master/docs/doxygen_makefile_sw) documentation of the software framework: available on [GitHub pages](https://stnolting.github.io/neorv32/files.html)

|

- [**Detailed data sheet**](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf) (pdf)

|

* [**Detailed data sheet**](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf) (pdf)

|

- Completely described in behavioral, platform-independent VHDL – no primitives, macros, etc.

|

* Completely described in behavioral, platform-independent VHDL - no primitives, macros, etc.

|

- Fully synchronous design, no latches, no gated clocks

|

* Fully synchronous design, no latches, no gated clocks

|

- Small hardware footprint and high operating frequency

|

* Small hardware footprint and high operating frequency

|

- Highly configurable CPU and processor setup

|

* Highly configurable CPU and processor setup

|

- [FreeRTOS port](https://github.com/stnolting/neorv32/blob/master/sw/example/demo_freeRTOS) available

|

* [FreeRTOS port](https://github.com/stnolting/neorv32/blob/master/sw/example/demo_freeRTOS) available

|

|

|

|

|

### Design Principles

|

### Design Principles

|

|

|

* From zero to main(): Completely open source and documented.

|

* From zero to `main()`: Completely open source and documented.

|

* Plain VHDL without technology-specific parts like attributes, macros or primitives.

|

* Plain VHDL without technology-specific parts like attributes, macros or primitives.

|

* Easy to use – working out of the box.

|

* Easy to use – working out of the box.

|

* Clean synchronous design, no wacky combinatorial interfaces.

|

* Clean synchronous design, no wacky combinatorial interfaces.

|

* Be as small as possible – but with a reasonable size-performance tradeoff.

|

* Be as small as possible – but with a reasonable size-performance tradeoff.

|

* The processor has to fit in a Lattice iCE40 UltraPlus 5k FPGA running at 20+ MHz.

|

* The processor has to fit in a Lattice iCE40 UltraPlus 5k FPGA running at 20+ MHz.

|

|

|

|

|

### Status

|

## Status

|

|

|

The processor is [synthesizable](#FPGA-Implementation-Results) (tested on *real hardware* using Intel Quartus Prime, Xilinx Vivado and Lattice Radiant/Synplify Pro) and can successfully execute

|

The processor is [synthesizable](#FPGA-Implementation-Results) (tested on *real hardware* using Intel Quartus Prime, Xilinx Vivado and Lattice Radiant/Synplify Pro) and can successfully execute

|

all the [provided example programs](https://github.com/stnolting/neorv32/tree/master/sw/example) including the [CoreMark benchmark](#CoreMark-Benchmark).

|

all the [provided example programs](https://github.com/stnolting/neorv32/tree/master/sw/example) including the [CoreMark benchmark](#CoreMark-Benchmark).

|

|

|

The processor passes the official `rv32i`, `rv32im`, `rv32imc`, `rv32Zicsr` and `rv32Zifencei` [RISC-V compliance tests](https://github.com/riscv/riscv-compliance).

|

The processor passes the official `rv32i`, `rv32im`, `rv32imc`, `rv32Zicsr` and `rv32Zifencei` [RISC-V compliance tests](https://github.com/riscv/riscv-compliance).

|

| Line 104... |

Line 105... |

| [RISC-V compliance test](https://github.com/stnolting/neorv32_riscv_compliance) | [](https://travis-ci.com/stnolting/neorv32_riscv_compliance) | |

|

| [RISC-V compliance test](https://github.com/stnolting/neorv32_riscv_compliance) | [](https://travis-ci.com/stnolting/neorv32_riscv_compliance) | |

|

|

|

|

|

### To-Do / Wish List

|

### To-Do / Wish List

|

|

|

- Add AXI(-Lite) bridges

|

* Add AXI(-Lite) bridges

|

- Synthesis results (+ wrappers?) for more platforms

|

* Synthesis results (+ wrappers?) for more platforms

|

- Maybe port additional RTOSs (like [Zephyr](https://github.com/zephyrproject-rtos/zephyr) or [RIOT](https://www.riot-os.org))

|

* Maybe port additional RTOSs (like [Zephyr](https://github.com/zephyrproject-rtos/zephyr) or [RIOT](https://www.riot-os.org))

|

- Implement further CPU extensions:

|

* Implement further CPU extensions:

|

- Atomic operations (`A`)

|

* Atomic operations (`A`)

|

- Bitmanipulation operations (`B`), when they are "official"

|

* Bitmanipulation operations (`B`), when they are "official"

|

- Floating-point instructions (`F`)

|

* Floating-point instructions (`F`)

|

- ...

|

* ...

|

|

|

|

|

## Features

|

## Features

|

|

|

The full-blown data sheet of the NEORV32 Processor/CPU is available as pdf file:

|

The full-blown data sheet of the NEORV32 Processor/CPU is available as pdf file:

|

| Line 126... |

Line 127... |

|

|

|

|

The NEORV32 Processor provides a full-scale microcontroller-like SoC based on the NEORV32 CPU. The setup

|

The NEORV32 Processor provides a full-scale microcontroller-like SoC based on the NEORV32 CPU. The setup

|

is highly customizable via the processor's top generics.

|

is highly customizable via the processor's top generics.

|

|

|

- Optional processor-internal data and instruction memories (**DMEM** / **IMEM**)

|

* Optional processor-internal data and instruction memories (**DMEM** / **IMEM**)

|

- Optional internal **Bootloader** with UART console and automatic SPI flash boot option

|

* Optional internal **Bootloader** with UART console and automatic SPI flash boot option

|

- Optional machine system timer (**MTIME**), RISC-V-compliant

|

* Optional machine system timer (**MTIME**), RISC-V-compliant

|

- Optional universal asynchronous receiver and transmitter (**UART**) with simulation output option via text.io

|

* Optional universal asynchronous receiver and transmitter (**UART**) with simulation output option via text.io

|

- Optional 8/16/24/32-bit serial peripheral interface controller (**SPI**) with 8 dedicated chip select lines

|

* Optional 8/16/24/32-bit serial peripheral interface controller (**SPI**) with 8 dedicated chip select lines

|

- Optional two wire serial interface controller (**TWI**), compatible to the I²C standard

|

* Optional two wire serial interface controller (**TWI**), compatible to the I²C standard

|

- Optional general purpose parallel IO port (**GPIO**), 32xOut & 32xIn, with pin-change interrupt

|

* Optional general purpose parallel IO port (**GPIO**), 32xOut & 32xIn, with pin-change interrupt

|

- Optional 32-bit external bus interface, Wishbone b4 compliant (**WISHBONE**), *standard* or *pipelined* handshake/transactions mode

|

* Optional 32-bit external bus interface, Wishbone b4 compliant (**WISHBONE**), *standard* or *pipelined* handshake/transactions mode

|

- Optional watchdog timer (**WDT**)

|

* Optional watchdog timer (**WDT**)

|

- Optional PWM controller with 4 channels and 8-bit duty cycle resolution (**PWM**)

|

* Optional PWM controller with 4 channels and 8-bit duty cycle resolution (**PWM**)

|

- Optional GARO-based true random number generator (**TRNG**)

|

* Optional GARO-based true random number generator (**TRNG**)

|

- Optional custom functions unit (**CFU**) for tightly-coupled custom co-processors

|

* Optional custom functions unit (**CFU**) for tightly-coupled custom co-processors

|

- System configuration information memory to check hardware configuration by software (**SYSINFO**)

|

* System configuration information memory to check hardware configuration by software (**SYSINFO**)

|

|

|

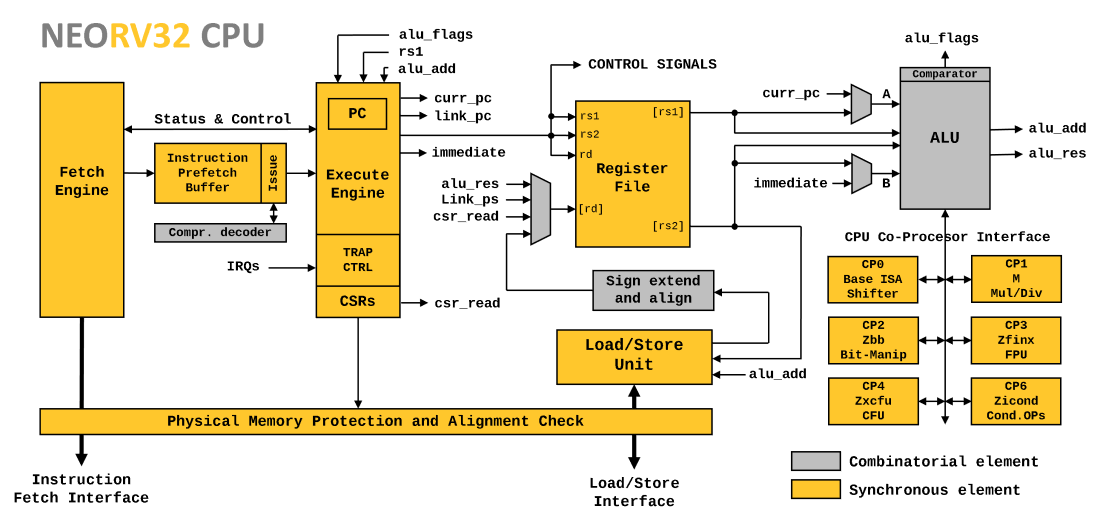

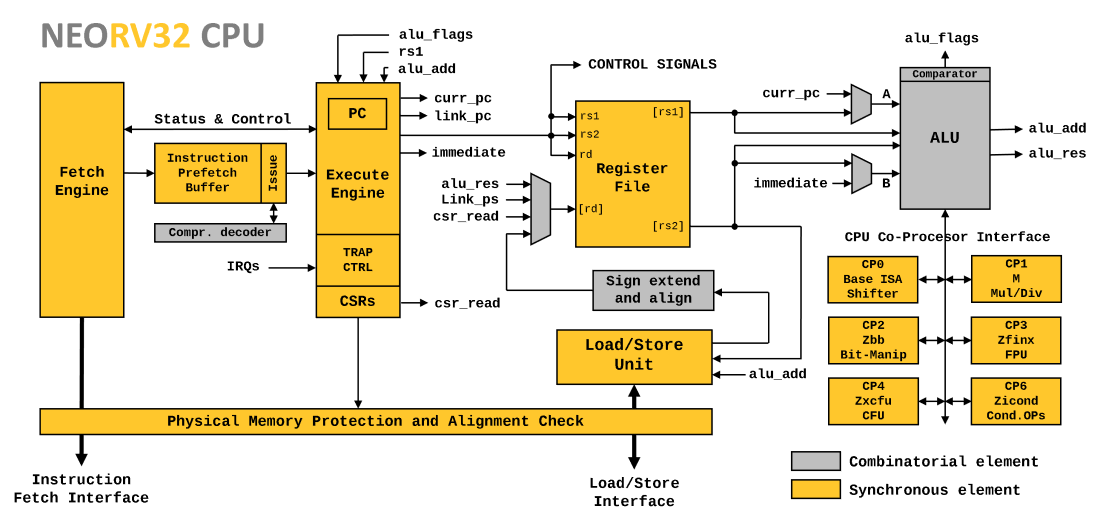

### CPU Features

|

### CPU Features

|

|

|

|

|

|

|

| Line 310... |

Line 311... |

|

|

~~~

|

~~~

|

**Configuration**

|

**Configuration**

|

Hardware: 32kB IMEM, 16kB DMEM, 100MHz clock

|

Hardware: 32kB IMEM, 16kB DMEM, 100MHz clock

|

CoreMark: 2000 iterations, MEM_METHOD is MEM_STACK

|

CoreMark: 2000 iterations, MEM_METHOD is MEM_STACK

|

Compiler: RISCV32-GCC 10.1.0 (rv32i)

|

Compiler: RISCV32-GCC 10.1.0 (rv32i toolchain)

|

|

Flags: default, see makefile

|

Peripherals: UART for printing the results

|

Peripherals: UART for printing the results

|

~~~

|

~~~

|

|

|

| CPU | Executable Size | Optimization | CoreMark Score | CoreMarks/MHz |

|

| CPU | Executable Size | Optimization | CoreMark Score | CoreMarks/MHz |

|

|:--------------------------|:---------------:|:------------:|:--------------:|:-------------:|

|

|:--------------------------|:---------------:|:------------:|:--------------:|:-------------:|

|

| `rv32i` | 26 940 bytes | `-O3` | 33.89 | 0.3389 |

|

| `rv32i` | 26 940 bytes | `-O3` | 33.89 | **0.3389** |

|

| `rv32im` | 25 772 bytes | `-O3` | 64.51 | 0.6451 |

|

| `rv32im` | 25 772 bytes | `-O3` | 64.51 | **0.6451** |

|

| `rv32im` + `FAST_MUL_EN` | 25 772 bytes | `-O3` | 80.00 | 0.8000 |

|

| `rv32imc` | 20 524 bytes | `-O3` | 64.51 | **0.6451** |

|

| `rv32imc` | 19 812 bytes | `-O3` | 62.50 | 0.6250 |

|

| `rv32imc` + `FAST_MUL_EN` | 20 524 bytes | `-O3` | 80.00 | **0.8000** |

|

| `rv32imc` + `FAST_MUL_EN` | 19 812 bytes | `-O3` | 76.92 | 0.7692 |

|

|

|

|

The `FAST_MUL_EN` configuration uses DSPs for the multiplier of the `M` extension (enabled via the `FAST_MUL_EN` generic).

|

The `FAST_MUL_EN` configuration uses DSPs for the multiplier of the `M` extension (enabled via the `FAST_MUL_EN` generic).

|

|

|

When the `C` extension is enabled, branches to an unaligned uncompressed instruction require additional instruction fetch cycles.

|

When the `C` extension is enabled, branches to an unaligned uncompressed instruction require additional instruction fetch cycles.

|

|

|

| Line 345... |

Line 346... |

|

|

Results generated for hardware version: `1.4.4.8`

|

Results generated for hardware version: `1.4.4.8`

|

|

|

| CPU | Required Clock Cycles | Executed Instructions | Average CPI |

|

| CPU | Required Clock Cycles | Executed Instructions | Average CPI |

|

|:------------------------|----------------------:|----------------------:|:-----------:|

|

|:------------------------|----------------------:|----------------------:|:-----------:|

|

| `rv32i` | 5 945 938 586 | 1 469 587 406 | 4.05 |

|

| `rv32i` | 5 945 938 586 | 1 469 587 406 | **4.05** |

|

| `rv32im` | 3 110 282 586 | 602 225 760 | 5.16 |

|

| `rv32im` | 3 110 282 586 | 602 225 760 | **5.16** |

|

| `rv32im` `FAST_MUL_EN` | 2 527 730 586 | 602 225 728 | 4.19 |

|

| `rv32imc` | 3 172 969 968 | 615 388 924 | **5.16** |

|

| `rv32imc` | 3 217 064 278 | 602 225 530 | 5.34 |

|

| `rv32imc` `FAST_MUL_EN` | 2 590 417 968 | 615 388 890 | **4.21** |

|

| `rv32imc` `FAST_MUL_EN` | 2 634 512 278 | 602 225 574 | 4.37 |

|

|

|

|

The `FAST_MUL_EN` configuration uses DSPs for the multiplier of the `M` extension (enabled via the `FAST_MUL_EN` generic).

|

The `FAST_MUL_EN` configuration uses DSPs for the multiplier of the `M` extension (enabled via the `FAST_MUL_EN` generic).

|

|

|

When the `C` extension is enabled, branches to an unaligned uncompressed instruction require additional instruction fetch cycles.

|

When the `C` extension is enabled, branches to an unaligned uncompressed instruction require additional instruction fetch cycles.

|

|

|

| Line 604... |

Line 604... |

### Upload the Executable via the Bootloader

|

### Upload the Executable via the Bootloader

|

|

|

Connect your FPGA board via UART to your computer and open the according port to interface with the NEORV32 bootloader. The bootloader

|

Connect your FPGA board via UART to your computer and open the according port to interface with the NEORV32 bootloader. The bootloader

|

uses the following default UART configuration:

|

uses the following default UART configuration:

|

|

|

- 19200 Baud

|

* 19200 Baud

|

- 8 data bits

|

* 8 data bits

|

- 1 stop bit

|

* 1 stop bit

|

- No parity bits

|

* No parity bits

|

- No transmission / flow control protocol (raw bytes only)

|

* No transmission / flow control protocol (raw bytes only)

|

- Newline on `\r\n` (carriage return & newline) - also for sent data

|

* Newline on `\r\n` (carriage return & newline) - also for sent data

|

|

|

Use the bootloader console to upload the `neorv32_exe.bin` executable and run your application image.

|

Use the bootloader console to upload the `neorv32_exe.bin` executable and run your application image.

|

|

|

```

|

```

|

<< NEORV32 Bootloader >>

|

<< NEORV32 Bootloader >>

|

| Line 743... |

Line 743... |

|

|

|

|

|

|

This project is not affiliated with or endorsed by the Open Source Initiative (https://www.oshwa.org / https://opensource.org).

|

This project is not affiliated with or endorsed by the Open Source Initiative (https://www.oshwa.org / https://opensource.org).

|

|

|

|

--------

|

|

|

|

This repository was created on June 23th, 2020.

|

|

|

Made with :coffee: in Hannover, Germany.

|

Made with :coffee: in Hannover, Germany.

|