| Line 2... |

Line 2... |

|

|

[](https://travis-ci.com/stnolting/neorv32)

|

[](https://travis-ci.com/stnolting/neorv32)

|

[](https://github.com/stnolting/neorv32/blob/master/LICENSE)

|

[](https://github.com/stnolting/neorv32/blob/master/LICENSE)

|

[](https://github.com/stnolting/neorv32/releases)

|

[](https://github.com/stnolting/neorv32/releases)

|

|

|

|

|

## Table of Content

|

|

|

|

* [Overview](#Overview)

|

* [Overview](#Overview)

|

* [Project Status](#Status)

|

* [Project Status](#Status)

|

* [Features](#Features)

|

* [Features](#Features)

|

* [FPGA Implementation Results](#FPGA-Implementation-Results)

|

* [FPGA Implementation Results](#FPGA-Implementation-Results)

|

* [Performance](#Performance)

|

* [Performance](#Performance)

|

| Line 73... |

Line 70... |

* [**Full-blown data sheet**](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf) (pdf)

|

* [**Full-blown data sheet**](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf) (pdf)

|

* Completely described in behavioral, platform-independent VHDL - no primitives, macros, etc.

|

* Completely described in behavioral, platform-independent VHDL - no primitives, macros, etc.

|

* Fully synchronous design, no latches, no gated clocks

|

* Fully synchronous design, no latches, no gated clocks

|

* Small hardware footprint and high operating frequency

|

* Small hardware footprint and high operating frequency

|

* Highly configurable CPU and processor setup

|

* Highly configurable CPU and processor setup

|

|

* [AXI4-Lite connectivity](#AXI4-Connectivity) - compatible with Xilinx Vivado IP Packer

|

* [FreeRTOS port](https://github.com/stnolting/neorv32/blob/master/sw/example/demo_freeRTOS) available

|

* [FreeRTOS port](https://github.com/stnolting/neorv32/blob/master/sw/example/demo_freeRTOS) available

|

|

|

|

|

### Design Principles

|

### Design Principles

|

|

|

| Line 100... |

Line 98... |

| [NEORV32 processor](https://github.com/stnolting/neorv32) | [](https://travis-ci.com/stnolting/neorv32) | [](https://stnolting.github.io/neorv32/files.html) |

|

| [NEORV32 processor](https://github.com/stnolting/neorv32) | [](https://travis-ci.com/stnolting/neorv32) | [](https://stnolting.github.io/neorv32/files.html) |

|

| [Pre-built toolchain](https://github.com/stnolting/riscv_gcc_prebuilt) | [](https://travis-ci.com/stnolting/riscv_gcc_prebuilt) | |

|

| [Pre-built toolchain](https://github.com/stnolting/riscv_gcc_prebuilt) | [](https://travis-ci.com/stnolting/riscv_gcc_prebuilt) | |

|

| [RISC-V compliance test](https://github.com/stnolting/neorv32_riscv_compliance) | [](https://travis-ci.com/stnolting/neorv32_riscv_compliance) | |

|

| [RISC-V compliance test](https://github.com/stnolting/neorv32_riscv_compliance) | [](https://travis-ci.com/stnolting/neorv32_riscv_compliance) | |

|

|

|

|

|

### To-Do / Wish List

|

### To-Do / Wish List / [Help Wanted](#Contribute)

|

|

|

|

* Add a cache for the external memory interface

|

|

* Use LaTeX for data sheet

|

* Further size and performance optimization

|

* Further size and performance optimization

|

* Add AXI(-Lite) bridges

|

|

* Synthesis results (+ wrappers?) for more platforms

|

* Synthesis results (+ wrappers?) for more platforms

|

* Maybe port additional RTOSs (like [Zephyr](https://github.com/zephyrproject-rtos/zephyr) or [RIOT](https://www.riot-os.org))

|

* Maybe port additional RTOSs (like [Zephyr](https://github.com/zephyrproject-rtos/zephyr) or [RIOT](https://www.riot-os.org))

|

* Use LaTeX for data sheet

|

|

* Implement further CPU extensions:

|

* Implement further CPU extensions:

|

* Atomic operations (`A`)

|

* Atomic operations (`A`)

|

* Bitmanipulation operations (`B`), when they are "official"

|

* Bitmanipulation operations (`B`), when they are "official"

|

* Floating-point instructions (`F`)

|

* Floating-point instructions (`F`)

|

* ...

|

* ...

|

| Line 119... |

Line 117... |

## Features

|

## Features

|

|

|

The full-blown data sheet of the NEORV32 Processor and CPU is available as pdf file:

|

The full-blown data sheet of the NEORV32 Processor and CPU is available as pdf file:

|

[ NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf).

|

[ NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf).

|

|

|

### Processor Features

|

### NEORV32 Processor (SoC)

|

|

|

|

|

|

|

The NEORV32 Processor provides a full-scale microcontroller-like SoC based on the NEORV32 CPU. The setup

|

The NEORV32 Processor provides a full-scale microcontroller-like SoC based on the NEORV32 CPU. The setup

|

is highly customizable via the processor's top generics.

|

is highly customizable via the processor's top generics.

|

| Line 131... |

Line 129... |

* Optional processor-internal data and instruction memories (**DMEM** / **IMEM**)

|

* Optional processor-internal data and instruction memories (**DMEM** / **IMEM**)

|

* Optional internal **Bootloader** with UART console and automatic SPI flash boot option

|

* Optional internal **Bootloader** with UART console and automatic SPI flash boot option

|

* Optional machine system timer (**MTIME**), RISC-V-compliant

|

* Optional machine system timer (**MTIME**), RISC-V-compliant

|

* Optional universal asynchronous receiver and transmitter (**UART**) with simulation output option via text.io

|

* Optional universal asynchronous receiver and transmitter (**UART**) with simulation output option via text.io

|

* Optional 8/16/24/32-bit serial peripheral interface controller (**SPI**) with 8 dedicated chip select lines

|

* Optional 8/16/24/32-bit serial peripheral interface controller (**SPI**) with 8 dedicated chip select lines

|

* Optional two wire serial interface controller (**TWI**), compatible to the I²C standard

|

* Optional two wire serial interface controller (**TWI**), with optional clock-stretching, compatible to the I²C standard

|

* Optional general purpose parallel IO port (**GPIO**), 32xOut & 32xIn, with pin-change interrupt

|

* Optional general purpose parallel IO port (**GPIO**), 32xOut & 32xIn, with pin-change interrupt

|

* Optional 32-bit external bus interface, Wishbone b4 compliant (**WISHBONE**), *standard* or *pipelined* handshake/transactions mode

|

* Optional 32-bit external bus interface, Wishbone b4 compliant (**WISHBONE**), *standard* or *pipelined* handshake/transactions mode

|

|

* Optional wrapper for **AXI4-Lite Master Interface** (see [AXI Connectivity](#AXI4-Connectivity)), compatibility verified with Xilinx Vivado Block Desginer

|

* Optional watchdog timer (**WDT**)

|

* Optional watchdog timer (**WDT**)

|

* Optional PWM controller with 4 channels and 8-bit duty cycle resolution (**PWM**)

|

* Optional PWM controller with 4 channels and 8-bit duty cycle resolution (**PWM**)

|

* Optional GARO-based true random number generator (**TRNG**)

|

* Optional GARO-based true random number generator (**TRNG**)

|

* Optional custom functions units (**CFU0** and **CFU1**) for tightly-coupled custom co-processors

|

* Optional custom functions units (**CFU0** and **CFU1**) for tightly-coupled custom co-processors

|

* System configuration information memory to check hardware configuration by software (**SYSINFO**)

|

* System configuration information memory to check hardware configuration by software (**SYSINFO**)

|

|

|

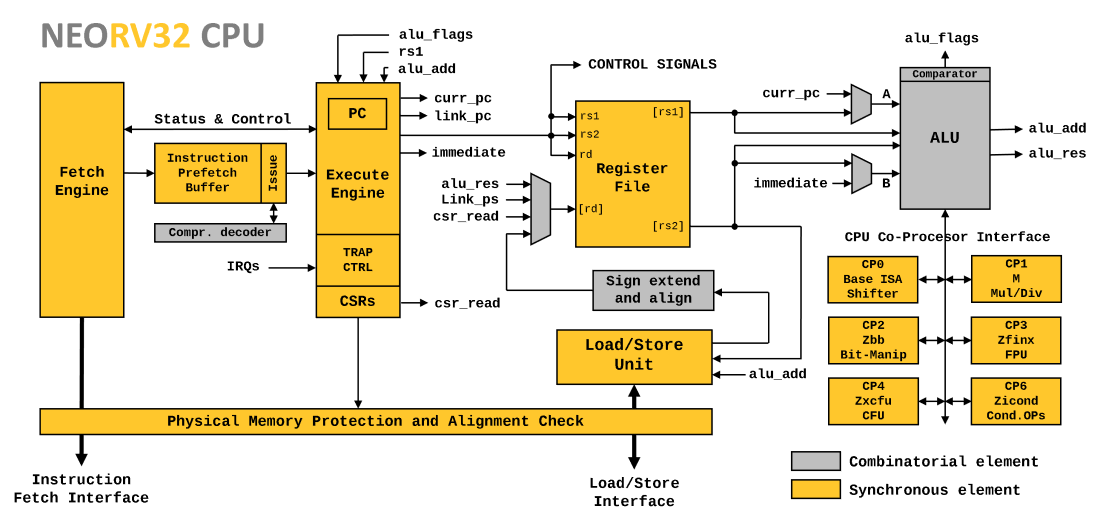

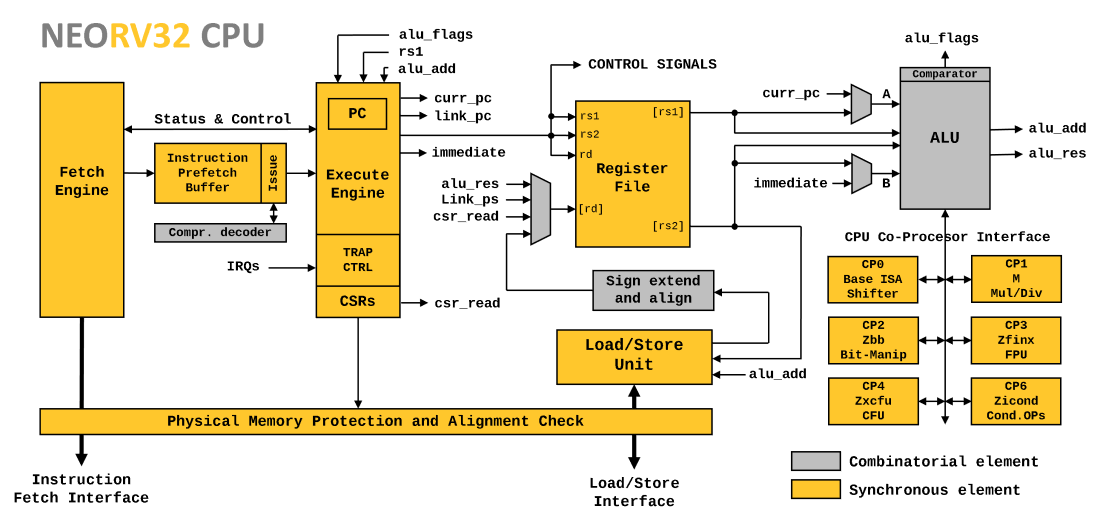

### CPU Features

|

### NEORV32 CPU

|

|

|

|

|

|

|

The CPU is [compliant](https://github.com/stnolting/neorv32_riscv_compliance) to the

|

The CPU is [compliant](https://github.com/stnolting/neorv32_riscv_compliance) to the

|

[official RISC-V specifications (2.2)](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/riscv-spec.pdf) including a subset of the

|

[official RISC-V specifications (2.2)](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/riscv-spec.pdf) including a subset of the

|

| Line 270... |

Line 269... |

| SYSINFO | System configuration information memory | 11 | 9 | 0 | 0 |

|

| SYSINFO | System configuration information memory | 11 | 9 | 0 | 0 |

|

| TRNG | True random number generator | 132 | 105 | 0 | 0 |

|

| TRNG | True random number generator | 132 | 105 | 0 | 0 |

|

| TWI | Two-wire interface | 74 | 44 | 0 | 0 |

|

| TWI | Two-wire interface | 74 | 44 | 0 | 0 |

|

| UART | Universal asynchronous receiver/transmitter | 175 | 132 | 0 | 0 |

|

| UART | Universal asynchronous receiver/transmitter | 175 | 132 | 0 | 0 |

|

| WDT | Watchdog timer | 58 | 45 | 0 | 0 |

|

| WDT | Watchdog timer | 58 | 45 | 0 | 0 |

|

| WISHBONE | External memory interface (`MEM_EXT_REG_STAGES` = 2) | 106 | 104 | 0 | 0 |

|

| WISHBONE | External memory interface | 106 | 104 | 0 | 0 |

|

|

|

|

|

### NEORV32 Processor - Exemplary FPGA Setups

|

### NEORV32 Processor - Exemplary FPGA Setups

|

|

|

Exemplary processor implementation results for different FPGA platforms. The processor setup uses *the default peripheral configuration* (like no _CFUs_ and no _TRNG_),

|

Exemplary processor implementation results for different FPGA platforms. The processor setup uses *the default peripheral configuration* (like no _CFUs_ and no _TRNG_),

|

| Line 419... |

Line 418... |

i_bus_re_o : out std_ulogic; -- read enable

|

i_bus_re_o : out std_ulogic; -- read enable

|

i_bus_cancel_o : out std_ulogic; -- cancel current bus transaction

|

i_bus_cancel_o : out std_ulogic; -- cancel current bus transaction

|

i_bus_ack_i : in std_ulogic := '0'; -- bus transfer acknowledge

|

i_bus_ack_i : in std_ulogic := '0'; -- bus transfer acknowledge

|

i_bus_err_i : in std_ulogic := '0'; -- bus transfer error

|

i_bus_err_i : in std_ulogic := '0'; -- bus transfer error

|

i_bus_fence_o : out std_ulogic; -- executed FENCEI operation

|

i_bus_fence_o : out std_ulogic; -- executed FENCEI operation

|

|

i_bus_priv_o : out std_ulogic_vector(1 downto 0); -- privilege level

|

-- data bus interface --

|

-- data bus interface --

|

d_bus_addr_o : out std_ulogic_vector(data_width_c-1 downto 0); -- bus access address

|

d_bus_addr_o : out std_ulogic_vector(data_width_c-1 downto 0); -- bus access address

|

d_bus_rdata_i : in std_ulogic_vector(data_width_c-1 downto 0) := (others => '0'); -- bus read data

|

d_bus_rdata_i : in std_ulogic_vector(data_width_c-1 downto 0) := (others => '0'); -- bus read data

|

d_bus_wdata_o : out std_ulogic_vector(data_width_c-1 downto 0); -- bus write data

|

d_bus_wdata_o : out std_ulogic_vector(data_width_c-1 downto 0); -- bus write data

|

d_bus_ben_o : out std_ulogic_vector(03 downto 0); -- byte enable

|

d_bus_ben_o : out std_ulogic_vector(03 downto 0); -- byte enable

|

| Line 430... |

Line 430... |

d_bus_re_o : out std_ulogic; -- read enable

|

d_bus_re_o : out std_ulogic; -- read enable

|

d_bus_cancel_o : out std_ulogic; -- cancel current bus transaction

|

d_bus_cancel_o : out std_ulogic; -- cancel current bus transaction

|

d_bus_ack_i : in std_ulogic := '0'; -- bus transfer acknowledge

|

d_bus_ack_i : in std_ulogic := '0'; -- bus transfer acknowledge

|

d_bus_err_i : in std_ulogic := '0'; -- bus transfer error

|

d_bus_err_i : in std_ulogic := '0'; -- bus transfer error

|

d_bus_fence_o : out std_ulogic; -- executed FENCE operation

|

d_bus_fence_o : out std_ulogic; -- executed FENCE operation

|

|

d_bus_priv_o : out std_ulogic_vector(1 downto 0); -- privilege level

|

-- system time input from MTIME --

|

-- system time input from MTIME --

|

time_i : in std_ulogic_vector(63 downto 0) := (others => '0'); -- current system time

|

time_i : in std_ulogic_vector(63 downto 0) := (others => '0'); -- current system time

|

-- interrupts (risc-v compliant) --

|

-- interrupts (risc-v compliant) --

|

msw_irq_i : in std_ulogic := '0'; -- machine software interrupt

|

msw_irq_i : in std_ulogic := '0'; -- machine software interrupt

|

mext_irq_i : in std_ulogic := '0'; -- machine external interrupt

|

mext_irq_i : in std_ulogic := '0'; -- machine external interrupt

|

| Line 442... |

Line 443... |

firq_i : in std_ulogic_vector(3 downto 0) := (others => '0')

|

firq_i : in std_ulogic_vector(3 downto 0) := (others => '0')

|

);

|

);

|

end neorv32_cpu;

|

end neorv32_cpu;

|

```

|

```

|

|

|

|

|

### NEORV32 Processor

|

### NEORV32 Processor

|

|

|

```vhdl

|

```vhdl

|

entity neorv32_top is

|

entity neorv32_top is

|

generic (

|

generic (

|

| Line 475... |

Line 475... |

-- Internal Data memory --

|

-- Internal Data memory --

|

MEM_INT_DMEM_USE : boolean := true; -- implement processor-internal data memory

|

MEM_INT_DMEM_USE : boolean := true; -- implement processor-internal data memory

|

MEM_INT_DMEM_SIZE : natural := 8*1024; -- size of processor-internal data memory in bytes

|

MEM_INT_DMEM_SIZE : natural := 8*1024; -- size of processor-internal data memory in bytes

|

-- External memory interface --

|

-- External memory interface --

|

MEM_EXT_USE : boolean := false; -- implement external memory bus interface?

|

MEM_EXT_USE : boolean := false; -- implement external memory bus interface?

|

MEM_EXT_REG_STAGES : natural := 2; -- number of interface register stages (0,1,2)

|

|

-- Processor peripherals --

|

-- Processor peripherals --

|

IO_GPIO_USE : boolean := true; -- implement general purpose input/output port unit (GPIO)?

|

IO_GPIO_USE : boolean := true; -- implement general purpose input/output port unit (GPIO)?

|

IO_MTIME_USE : boolean := true; -- implement machine system timer (MTIME)?

|

IO_MTIME_USE : boolean := true; -- implement machine system timer (MTIME)?

|

IO_UART_USE : boolean := true; -- implement universal asynchronous receiver/transmitter (UART)?

|

IO_UART_USE : boolean := true; -- implement universal asynchronous receiver/transmitter (UART)?

|

IO_SPI_USE : boolean := true; -- implement serial peripheral interface (SPI)?

|

IO_SPI_USE : boolean := true; -- implement serial peripheral interface (SPI)?

|

| Line 503... |

Line 502... |

wb_stb_o : out std_ulogic; -- strobe

|

wb_stb_o : out std_ulogic; -- strobe

|

wb_cyc_o : out std_ulogic; -- valid cycle

|

wb_cyc_o : out std_ulogic; -- valid cycle

|

wb_ack_i : in std_ulogic := '0'; -- transfer acknowledge

|

wb_ack_i : in std_ulogic := '0'; -- transfer acknowledge

|

wb_err_i : in std_ulogic := '0'; -- transfer error

|

wb_err_i : in std_ulogic := '0'; -- transfer error

|

-- Advanced memory control signals (available if MEM_EXT_USE = true) --

|

-- Advanced memory control signals (available if MEM_EXT_USE = true) --

|

|

priv_o : out std_ulogic_vector(1 downto 0); -- current CPU privilege level

|

fence_o : out std_ulogic; -- indicates an executed FENCE operation

|

fence_o : out std_ulogic; -- indicates an executed FENCE operation

|

fencei_o : out std_ulogic; -- indicates an executed FENCEI operation

|

fencei_o : out std_ulogic; -- indicates an executed FENCEI operation

|

-- GPIO (available if IO_GPIO_USE = true) --

|

-- GPIO (available if IO_GPIO_USE = true) --

|

gpio_o : out std_ulogic_vector(31 downto 0); -- parallel output

|

gpio_o : out std_ulogic_vector(31 downto 0); -- parallel output

|

gpio_i : in std_ulogic_vector(31 downto 0) := (others => '0'); -- parallel input

|

gpio_i : in std_ulogic_vector(31 downto 0) := (others => '0'); -- parallel input

|

| Line 517... |

Line 517... |

spi_sck_o : out std_ulogic; -- SPI serial clock

|

spi_sck_o : out std_ulogic; -- SPI serial clock

|

spi_sdo_o : out std_ulogic; -- controller data out, peripheral data in

|

spi_sdo_o : out std_ulogic; -- controller data out, peripheral data in

|

spi_sdi_i : in std_ulogic := '0'; -- controller data in, peripheral data out

|

spi_sdi_i : in std_ulogic := '0'; -- controller data in, peripheral data out

|

spi_csn_o : out std_ulogic_vector(07 downto 0); -- SPI CS

|

spi_csn_o : out std_ulogic_vector(07 downto 0); -- SPI CS

|

-- TWI (available if IO_TWI_USE = true) --

|

-- TWI (available if IO_TWI_USE = true) --

|

twi_sda_io : inout std_logic := 'H'; -- twi serial data line

|

twi_sda_io : inout std_logic; -- twi serial data line

|

twi_scl_io : inout std_logic := 'H'; -- twi serial clock line

|

twi_scl_io : inout std_logic; -- twi serial clock line

|

-- PWM (available if IO_PWM_USE = true) --

|

-- PWM (available if IO_PWM_USE = true) --

|

pwm_o : out std_ulogic_vector(03 downto 0); -- pwm channels

|

pwm_o : out std_ulogic_vector(03 downto 0); -- pwm channels

|

-- Interrupts --

|

-- Interrupts --

|

mtime_irq_i : in std_ulogic := '0'; -- machine timer interrupt, available if IO_MTIME_USE = false

|

mtime_irq_i : in std_ulogic := '0'; -- machine timer interrupt, available if IO_MTIME_USE = false

|

msw_irq_i : in std_ulogic := '0'; -- machine software interrupt

|

msw_irq_i : in std_ulogic := '0'; -- machine software interrupt

|

mext_irq_i : in std_ulogic := '0' -- machine external interrupt

|

mext_irq_i : in std_ulogic := '0' -- machine external interrupt

|

);

|

);

|

end neorv32_top;

|

end neorv32_top;

|

```

|

```

|

|

|

|

### AXI4 Connectivity

|

|

|

|

Via the [`rtl/top_templates/neorv32_top_axi4lite.vhd`](https://github.com/stnolting/neorv32/blob/master/rtl/top_templates/neorv32_top_axi4lite.vhd)

|

|

wrapper the NEORV32 provides an **AXI4-Lite** compatible master interface. This wrapper instantiates the default

|

|

[NEORV32 processor top entitiy](https://github.com/stnolting/neorv32/blob/master/rtl/core/neorv32_top.vhd) and implements a Wishbone to AXI4-Lite bridge.

|

|

|

|

The AXI4-Lite interface has been tested using Xilinx Vivado 19.2 block designer:

|

|

|

|

|

|

|

|

The processor was packed as custom IP using `neorv32_top_axi4lite.vhd` as top entity. The AXI interface is automatically detected by the packager.

|

|

All remaining IO interfaces are available as custom signals. The configuration generics are available via the "customize IP" dialog.

|

|

In the figure above the resulting IP block is named "neorv32_top_axi4lite_v1_0".

|

|

*(Note: Use Syntheiss option "global" when generating the block design to maintain the internal TWI tri-state drivers.)*

|

|

|

|

The setup uses an AXI interconnect to attach two block RAMs to the processor. Since the processor in this example is configured *without* IMEM and DMEM,

|

|

the attached block RAMs are used for storing instructions and data: the first RAM is used as instruction memory

|

|

and is mapped to address `0x00000000 - 0x00003fff` (16kB), the second RAM is used as data memory and is mapped to address `0x80000000 - 0x80001fff` (8kB).

|

|

|

|

|

|

|

## Getting Started

|

## Getting Started

|

|

|

This overview is just a short excerpt from the *Let's Get It Started* section of the NEORV32 documentary:

|

This overview is just a short excerpt from the *Let's Get It Started* section of the NEORV32 documentary:

|

| Line 735... |

Line 754... |

|

|

#### Proprietary Notice

|

#### Proprietary Notice

|

|

|

"Artix" and "Vivado" are trademarks of Xilinx Inc.

|

"Artix" and "Vivado" are trademarks of Xilinx Inc.

|

|

|

"Cyclone", "Quartus Prime", "Quartus Prime Lite" and "Avalon Bus" are trademarks of Intel Corporation.

|

"Cyclone", "Quartus Prime Lite" and "Avalon Bus" are trademarks of Intel Corporation.

|

|

|

"Artix" and "Vivado" are trademarks of Xilinx, Inc.

|

|

|

|

"iCE40", "UltraPlus" and "Lattice Radiant" are trademarks of Lattice Semiconductor Corporation.

|

"iCE40", "UltraPlus" and "Radiant" are trademarks of Lattice Semiconductor Corporation.

|

|

|

"AXI" and "AXI-Lite" are trademarks of Arm Holdings plc.

|

"AXI", "AXI4" and "AXI4-Lite" are trademarks of Arm Holdings plc.

|

|

|

|

|

|

|

## Acknowledgements

|

## Acknowledgements

|

|

|