| Line 28... |

Line 28... |

### Key Features

|

### Key Features

|

|

|

* RISC-V-[compliant](#Status) 32-bit `rv32i` [**NEORV32 CPU**](#NEORV32-CPU-Features), compliant to

|

* RISC-V-[compliant](#Status) 32-bit `rv32i` [**NEORV32 CPU**](#NEORV32-CPU-Features), compliant to

|

* Subset of the *Unprivileged ISA Specification* [(Version 2.2)](https://github.com/stnolting/neorv32/blob/master/docs/riscv-privileged.pdf)

|

* Subset of the *Unprivileged ISA Specification* [(Version 2.2)](https://github.com/stnolting/neorv32/blob/master/docs/riscv-privileged.pdf)

|

* Subset of the *Privileged Architecture Specification* [(Version 1.12-draft)](https://github.com/stnolting/neorv32/blob/master/docs/riscv-spec.pdf)

|

* Subset of the *Privileged Architecture Specification* [(Version 1.12-draft)](https://github.com/stnolting/neorv32/blob/master/docs/riscv-spec.pdf)

|

* Optional CPU extensions

|

* Optional RISC-V CPU extensions

|

|

* `A` - atomic memory access instructions

|

* `C` - compressed instructions (16-bit)

|

* `C` - compressed instructions (16-bit)

|

* `E` - embedded CPU (reduced register file)

|

* `E` - embedded CPU (reduced register file)

|

* `M` - integer multiplication and division hardware

|

* `M` - integer multiplication and division hardware

|

* `U` - less-privileged *user mode*

|

* `U` - less-privileged *user mode*

|

* `Zicsr` - control and status register access instructions (+ exception/irq system)

|

* `Zicsr` - control and status register access instructions (+ exception/irq system)

|

* `Zifencei` - instruction stream synchronization

|

* `Zifencei` - instruction stream synchronization

|

* `PMP` - physical memory protection

|

* `PMP` - physical memory protection

|

* Full-scale RISC-V microcontroller system (**SoC**) [**NEORV32 Processor**](#NEORV32-Processor-Features) with optional submodules

|

* Full-scale RISC-V microcontroller system / **SoC** [**NEORV32 Processor**](#NEORV32-Processor-Features) with optional submodules

|

* optional embedded memories (instruction/data/bootloader, RAM/ROM)

|

* optional embedded memories (instructions/data/bootloader, RAM/ROM)

|

* timers (watch dog, RISC-V-compliant machine timer)

|

* timers (watch dog, RISC-V-compliant machine timer)

|

* serial interfaces (SPI, TWI, UART)

|

* serial interfaces (SPI, TWI, UART) and general purpose IO

|

* external bus interface (Wishbone / [AXI4](#AXI4-Connectivity))

|

* external bus interface (Wishbone / [AXI4](#AXI4-Connectivity))

|

* [more ...](#NEORV32-Processor-Features)

|

* [more ...](#NEORV32-Processor-Features)

|

* Software framework

|

* Software framework

|

* core libraries for high-level usage of the provided functions and peripherals

|

* core libraries for high-level usage of the provided functions and peripherals

|

* application compilation based on [GNU makefiles](https://github.com/stnolting/neorv32/blob/master/sw/example/blink_led/makefile)

|

* application compilation based on [GNU makefiles](https://github.com/stnolting/neorv32/blob/master/sw/example/blink_led/makefile)

|

| Line 62... |

Line 63... |

For more information take a look at the [NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf) (pdf).

|

For more information take a look at the [NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf) (pdf).

|

|

|

|

|

### Design Principles

|

### Design Principles

|

|

|

* From zero to `main()`: Completely open source and documented.

|

* From zero to *hello_world*: Completely open source and documented.

|

* Plain VHDL without technology-specific parts like attributes, macros or primitives.

|

* Plain VHDL without technology-specific parts like attributes, macros or primitives.

|

* Easy to use – working out of the box.

|

* Easy to use – working out of the box.

|

* Clean synchronous design, no wacky combinatorial interfaces.

|

* Clean synchronous design, no wacky combinatorial interfaces.

|

* Be as small as possible – but with a reasonable size-performance tradeoff.

|

* Be as small as possible – but with a reasonable size-performance tradeoff.

|

* The processor has to fit in a Lattice iCE40 UltraPlus 5k FPGA running at 20+ MHz.

|

* The processor has to fit in a Lattice iCE40 UltraPlus 5k FPGA running at 20+ MHz.

|

| Line 84... |

Line 85... |

| [NEORV32 processor](https://github.com/stnolting/neorv32) | [](https://travis-ci.com/stnolting/neorv32) | [](https://stnolting.github.io/neorv32/files.html) |

|

| [NEORV32 processor](https://github.com/stnolting/neorv32) | [](https://travis-ci.com/stnolting/neorv32) | [](https://stnolting.github.io/neorv32/files.html) |

|

| [Pre-built toolchain](https://github.com/stnolting/riscv_gcc_prebuilt) | [](https://travis-ci.com/stnolting/riscv_gcc_prebuilt) | |

|

| [Pre-built toolchain](https://github.com/stnolting/riscv_gcc_prebuilt) | [](https://travis-ci.com/stnolting/riscv_gcc_prebuilt) | |

|

| [RISC-V compliance test](https://github.com/stnolting/neorv32_riscv_compliance) | [](https://travis-ci.com/stnolting/neorv32_riscv_compliance) | |

|

| [RISC-V compliance test](https://github.com/stnolting/neorv32_riscv_compliance) | [](https://travis-ci.com/stnolting/neorv32_riscv_compliance) | |

|

|

|

|

|

### To-Do / Wish List / [Help Wanted](#Contribute)

|

### To-Do / Wish List / Help Wanted

|

|

|

* Use LaTeX for data sheet

|

* Use LaTeX for data sheet

|

* More support for FreeRTOS

|

* Further size and performance optimization *(work in progress)*

|

* Further size and performance optimization

|

* A cache for the external memory/bus interface *(work in progress)*

|

|

* Burst mode for the external memory/bus interface

|

|

* RISC-V `B` extension ([bitmanipulation](https://github.com/riscv/riscv-bitmanip))

|

* Synthesis results (+ wrappers?) for more/specific platforms

|

* Synthesis results (+ wrappers?) for more/specific platforms

|

|

* More support for FreeRTOS

|

* Maybe port additional RTOSs (like [Zephyr](https://github.com/zephyrproject-rtos/zephyr) or [RIOT](https://www.riot-os.org))

|

* Maybe port additional RTOSs (like [Zephyr](https://github.com/zephyrproject-rtos/zephyr) or [RIOT](https://www.riot-os.org))

|

* Implement further RISC-V (or custom?) CPU extensions (like floating-point operations ('F'))

|

* Implement further RISC-V (or custom?) CPU extensions (like floating-point extension `F`)

|

* ...

|

* ...

|

|

* [Ideas?](#Contribute)

|

|

|

#### Work-in-progress

|

|

|

|

* A cache for the external memory/bus interface (also providing burst mode?)

|

|

* RISC-V `B` extension ([bitmanipulation](https://github.com/riscv/riscv-bitmanip))

|

|

|

|

|

|

## Features

|

## Features

|

|

|

The full-blown data sheet of the NEORV32 Processor and CPU is available as pdf file:

|

The full-blown data sheet of the NEORV32 Processor and CPU is available as pdf file:

|

| Line 129... |

Line 130... |

* custom functions units (**CFU0** and **CFU1**) for tightly-coupled custom co-processors

|

* custom functions units (**CFU0** and **CFU1**) for tightly-coupled custom co-processors

|

* system configuration information memory to check hardware configuration by software (**SYSINFO**, mandatory - not *optional*)

|

* system configuration information memory to check hardware configuration by software (**SYSINFO**, mandatory - not *optional*)

|

|

|

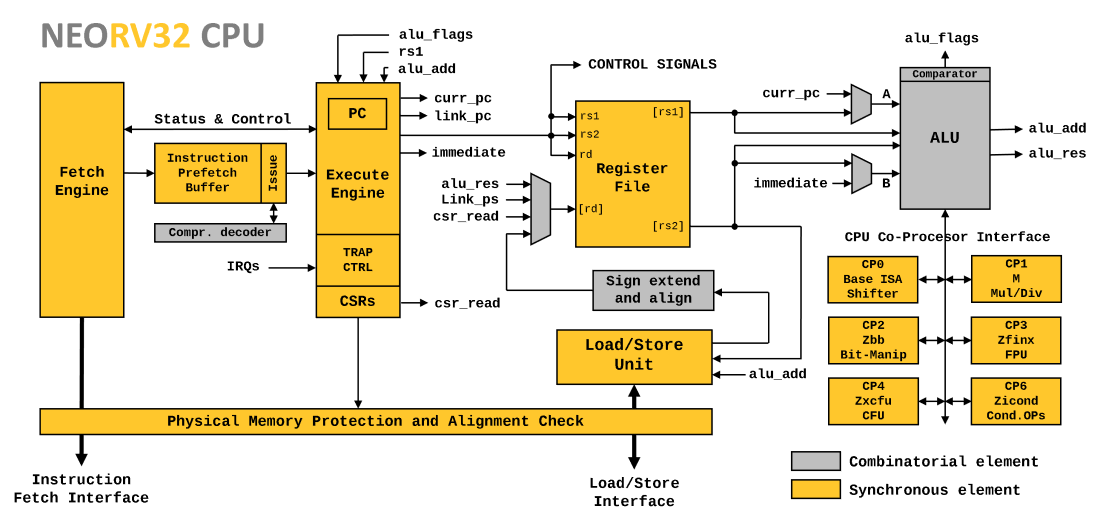

### NEORV32 CPU Features

|

### NEORV32 CPU Features

|

|

|

|

The NEORV32 CPU is [compliant](https://github.com/stnolting/neorv32_riscv_compliance) to the

|

|

|

The CPU is [compliant](https://github.com/stnolting/neorv32_riscv_compliance) to the

|

|

[official RISC-V specifications (2.2)](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/riscv-spec.pdf) including a subset of the

|

[official RISC-V specifications (2.2)](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/riscv-spec.pdf) including a subset of the

|

[RISC-V privileged architecture specifications (1.12-draft)](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/riscv-spec.pdf).

|

[RISC-V privileged architecture specifications (1.12-draft)](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/riscv-spec.pdf).

|

|

|

More information regarding the CPU including a detailed list of the instruction set and the available CSRs can be found in

|

More information regarding the CPU including a detailed list of the instruction set and the available CSRs can be found in

|

the [NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf).

|

the [NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf).

|

| Line 170... |

Line 169... |

* Multiplication instructions: `MUL` `MULH` `MULHSU` `MULHU`

|

* Multiplication instructions: `MUL` `MULH` `MULHSU` `MULHU`

|

* Division instructions: `DIV` `DIVU` `REM` `REMU`

|

* Division instructions: `DIV` `DIVU` `REM` `REMU`

|

* By default, the multiplier and divider cores use an iterative bit-serial processing scheme

|

* By default, the multiplier and divider cores use an iterative bit-serial processing scheme

|

* Multiplications can be mapped to DSPs via the `FAST_MUL_EN` generic to increase performance

|

* Multiplications can be mapped to DSPs via the `FAST_MUL_EN` generic to increase performance

|

|

|

|

**Atomic memory access** (`A` extension):

|

|

* Supported instruction: `LR.W` `SC.W`

|

|

* By default, the multiplier and divider cores use an iterative bit-serial processing scheme

|

|

|

**Privileged architecture / CSR access** (`Zicsr` extension):

|

**Privileged architecture / CSR access** (`Zicsr` extension):

|

* Privilege levels: `M-mode` (Machine mode)

|

* Privilege levels: `M-mode` (Machine mode)

|

* CSR access instructions: `CSRRW` `CSRRS` `CSRRC` `CSRRWI` `CSRRSI` `CSRRCI`

|

* CSR access instructions: `CSRRW` `CSRRS` `CSRRC` `CSRRWI` `CSRRSI` `CSRRCI`

|

* System instructions: `MRET` `WFI`

|

* System instructions: `MRET` `WFI`

|

* Counter CSRs: `cycle` `cycleh` `instret` `instreth` `time` `timeh` `mcycle` `mcycleh` `minstret` `minstreth`

|

* Counter CSRs: `cycle` `cycleh` `instret` `instreth` `time` `timeh` `mcycle` `mcycleh` `minstret` `minstreth`

|

| Line 205... |

Line 208... |

|

|

### Non-RISC-V-Compliant Issues

|

### Non-RISC-V-Compliant Issues

|

|

|

* `misa` CSR is read-only - no dynamic enabling/disabling of synthesized CPU extensions during runtime; for compatibility: write accesses (in m-mode) are ignored and do not cause an exception

|

* `misa` CSR is read-only - no dynamic enabling/disabling of synthesized CPU extensions during runtime; for compatibility: write accesses (in m-mode) are ignored and do not cause an exception

|

* The physical memory protection (**PMP**) only supports `NAPOT` mode, a minimal granularity of 8 bytes and only up to 8 regions

|

* The physical memory protection (**PMP**) only supports `NAPOT` mode, a minimal granularity of 8 bytes and only up to 8 regions

|

|

* The `A` extension only implements `lr.w` and `sc.w` instructions yet. However, these instructions are sufficient to emulate all further AMO operations

|

|

|

|

|

### NEORV32-Specific CPU Extensions

|

### NEORV32-Specific CPU Extensions

|

|

|

The NEORV32-specific extensions are always enabled and are indicated via the `X` bit in the `misa` CSR.

|

The NEORV32-specific extensions are always enabled and are indicated via the `X` bit in the `misa` CSR.

|

| Line 225... |

Line 229... |

This chapter shows exemplary implementation results of the NEORV32 CPU for an **Intel Cyclone IV EP4CE22F17C6N FPGA** on

|

This chapter shows exemplary implementation results of the NEORV32 CPU for an **Intel Cyclone IV EP4CE22F17C6N FPGA** on

|

a DE0-nano board. The design was synthesized using **Intel Quartus Prime Lite 20.1** ("balanced implementation"). The timing

|

a DE0-nano board. The design was synthesized using **Intel Quartus Prime Lite 20.1** ("balanced implementation"). The timing

|

information is derived from the Timing Analyzer / Slow 1200mV 0C Model. If not otherwise specified, the default configuration

|

information is derived from the Timing Analyzer / Slow 1200mV 0C Model. If not otherwise specified, the default configuration

|

of the CPU's generics is assumed (for example no PMP). No constraints were used at all.

|

of the CPU's generics is assumed (for example no PMP). No constraints were used at all.

|

|

|

Results generated for hardware version `1.4.7.0`.

|

Results generated for hardware version `1.4.8.0`.

|

|

|

| CPU Configuration | LEs | FFs | Memory bits | DSPs | f_max |

|

| CPU Configuration | LEs | FFs | Memory bits | DSPs | f_max |

|

|:---------------------------------------|:----------:|:--------:|:-----------:|:----:|:--------:|

|

|:----------------------------------------|:----------:|:--------:|:-----------:|:----:|:--------:|

|

| `rv32i` | 932 | 413 | 2048 | 0 | ~120 MHz |

|

| `rv32i` | 945 | 417 | 2048 | 0 | ~122 MHz |

|

| `rv32i` + `u` + `Zicsr` + `Zifencei` | 1800 | 815 | 2048 | 0 | ~118 MHz |

|

| `rv32i` + `u` + `Zicsr` + `Zifencei` | 1944 | 901 | 2048 | 0 | ~119 MHz |

|

| `rv32im` + `u` + `Zicsr` + `Zifencei` | 2368 | 1058 | 2048 | 0 | ~117 MHz |

|

| `rv32im` + `u` + `Zicsr` + `Zifencei` | 2551 | 1147 | 2048 | 0 | ~117 MHz |

|

| `rv32imc` + `u` + `Zicsr` + `Zifencei` | 2604 | 1073 | 2048 | 0 | ~113 MHz |

|

| `rv32imc` + `u` + `Zicsr` + `Zifencei` | 2800 | 1162 | 2048 | 0 | ~113 MHz |

|

| `rv32emc` + `u` + `Zicsr` + `Zifencei` | 2613 | 1073 | 1024 | 0 | ~113 MHz |

|

| `rv32imac` + `u` + `Zicsr` + `Zifencei` | 1796 | 1165 | 2048 | 0 | ~113 MHz |

|

|

|

|

Setups with enabled "embedded CPU extension" `E` show the same LUT and FF utilization and identical f_max. However, the size of the register file is cut in half.

|

|

|

|

|

### NEORV32 Processor-Internal Peripherals and Memories

|

### NEORV32 Processor-Internal Peripherals and Memories

|

|

|

Results generated for hardware version `1.4.7.0`.

|

Results generated for hardware version `1.4.8.0`.

|

|

|

| Module | Description | LEs | FFs | Memory bits | DSPs |

|

| Module | Description | LEs | FFs | Memory bits | DSPs |

|

|:----------|:-----------------------------------------------------|----:|----:|------------:|-----:|

|

|:----------|:-----------------------------------------------------|----:|----:|------------:|-----:|

|

| BOOT ROM | Bootloader ROM (default 4kB) | 3 | 1 | 32 768 | 0 |

|

| BOOT ROM | Bootloader ROM (default 4kB) | 3 | 1 | 32 768 | 0 |

|

| BUSSWITCH | Mux for CPU I & D interfaces | 63 | 8 | 0 | 0 |

|

| BUSSWITCH | Mux for CPU I & D interfaces | 82 | 8 | 0 | 0 |

|

| CFU0 | Custom functions unit 0 | - | - | - | - |

|

| CFU0 | Custom functions unit 0 | - | - | - | - |

|

| CFU1 | Custom functions unit 1 | - | - | - | - |

|

| CFU1 | Custom functions unit 1 | - | - | - | - |

|

| DMEM | Processor-internal data memory (default 8kB) | 12 | 2 | 65 536 | 0 |

|

| DMEM | Processor-internal data memory (default 8kB) | 6 | 2 | 65 536 | 0 |

|

| GPIO | General purpose input/output ports | 66 | 65 | 0 | 0 |

|

| GPIO | General purpose input/output ports | 66 | 65 | 0 | 0 |

|

| IMEM | Processor-internal instruction memory (default 16kb) | 7 | 2 | 131 072 | 0 |

|

| IMEM | Processor-internal instruction memory (default 16kb) | 6 | 2 | 131 072 | 0 |

|

| MTIME | Machine system timer | 272 | 166 | 0 | 0 |

|

| MTIME | Machine system timer | 282 | 166 | 0 | 0 |

|

| PWM | Pulse-width modulation controller | 72 | 69 | 0 | 0 |

|

| PWM | Pulse-width modulation controller | 71 | 69 | 0 | 0 |

|

| SPI | Serial peripheral interface | 142 | 124 | 0 | 0 |

|

| SPI | Serial peripheral interface | 129 | 124 | 0 | 0 |

|

| SYSINFO | System configuration information memory | 11 | 9 | 0 | 0 |

|

| SYSINFO | System configuration information memory | 9 | 9 | 0 | 0 |

|

| TRNG | True random number generator | 132 | 105 | 0 | 0 |

|

| TRNG | True random number generator | 132 | 105 | 0 | 0 |

|

| TWI | Two-wire interface | 77 | 44 | 0 | 0 |

|

| TWI | Two-wire interface | 77 | 44 | 0 | 0 |

|

| UART | Universal asynchronous receiver/transmitter | 173 | 132 | 0 | 0 |

|

| UART | Universal asynchronous receiver/transmitter | 175 | 132 | 0 | 0 |

|

| WDT | Watchdog timer | 58 | 45 | 0 | 0 |

|

| WDT | Watchdog timer | 59 | 45 | 0 | 0 |

|

| WISHBONE | External memory interface | 106 | 104 | 0 | 0 |

|

| WISHBONE | External memory interface | 129 | 104 | 0 | 0 |

|

|

|

|

|

### NEORV32 Processor - Exemplary FPGA Setups

|

### NEORV32 Processor - Exemplary FPGA Setups

|

|

|

Exemplary processor implementation results for different FPGA platforms. The processor setup uses *the default peripheral configuration* (like no _CFUs_ and no _TRNG_),

|

Exemplary processor implementation results for different FPGA platforms. The processor setup uses *the default peripheral configuration* (like no _CFUs_ and no _TRNG_),

|

| Line 544... |

Line 550... |

to [open a new issue](https://github.com/stnolting/neorv32/issues) or directly [drop me a line](mailto:stnolting@gmail.com). If you'd like to contribute:

|

to [open a new issue](https://github.com/stnolting/neorv32/issues) or directly [drop me a line](mailto:stnolting@gmail.com). If you'd like to contribute:

|

|

|

0. Check out the project's [code of conduct](https://github.com/stnolting/neorv32/tree/master/CODE_OF_CONDUCT.md)

|

0. Check out the project's [code of conduct](https://github.com/stnolting/neorv32/tree/master/CODE_OF_CONDUCT.md)

|

1. [Fork](https://github.com/stnolting/neorv32/fork) this repository and clone the fork

|

1. [Fork](https://github.com/stnolting/neorv32/fork) this repository and clone the fork

|

2. Create a feature branch in your fork: `git checkout -b awesome_new_feature_branch`

|

2. Create a feature branch in your fork: `git checkout -b awesome_new_feature_branch`

|

3. Create a new remote for the upstream repo: `git remote add https://github.com/stnolting/neorv32`

|

3. Create a new remote for the upstream repo: `git remote add upstream https://github.com/stnolting/neorv32`

|

3. Commit your modifications: `git commit -m "Awesome new feature!"`

|

3. Commit your modifications: `git commit -m "Awesome new feature!"`

|

4. Push to the branch: `git push origin awesome_new_feature_branch`

|

4. Push to the branch: `git push origin awesome_new_feature_branch`

|

5. Create a new [pull request](https://github.com/stnolting/neorv32/pulls)

|

5. Create a new [pull request](https://github.com/stnolting/neorv32/pulls)

|

|

|

|

|