| Line 1... |

Line 1... |

[](https://github.com/stnolting/neorv32)

|

[](https://github.com/stnolting/neorv32)

|

|

|

# The NEORV32 RISC-V Processor

|

# The NEORV32 RISC-V Processor

|

|

|

[](https://github.com/stnolting/neorv32/actions?query=workflow%3A%22Processor+Check%22)

|

[](https://github.com/stnolting/neorv32/actions?query=workflow%3A%22Processor+Check%22)

|

[](https://github.com/stnolting/neorv32/actions?query=workflow%3A%22RISC-V+Compliance%22)

|

[](https://github.com/stnolting/neorv32/actions?query=workflow%3A%22RISC-V+Compliance%22)

|

| Line 33... |

Line 33... |

:page_facing_up: For more detailed information take a look at the [NEORV32 data sheet (pdf)](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf).

|

:page_facing_up: For more detailed information take a look at the [NEORV32 data sheet (pdf)](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf).

|

|

|

|

|

### Key Features

|

### Key Features

|

|

|

* RISC-V 32-bit `rv32i` [**NEORV32 CPU**](#NEORV32-CPU-Features), compliant to

|

* RISC-V 32-bit `rv32` [**NEORV32 CPU**](#NEORV32-CPU-Features), compliant to

|

* subset of the *Unprivileged ISA Specification* [(Version 2.2)](https://github.com/stnolting/neorv32/blob/master/docs/riscv-privileged.pdf)

|

* subset of the *Unprivileged ISA Specification* [(Version 2.2)](https://github.com/stnolting/neorv32/blob/master/docs/riscv-privileged.pdf)

|

* subset of the *Privileged Architecture Specification* [(Version 1.12-draft)](https://github.com/stnolting/neorv32/blob/master/docs/riscv-spec.pdf)

|

* subset of the *Privileged Architecture Specification* [(Version 1.12-draft)](https://github.com/stnolting/neorv32/blob/master/docs/riscv-spec.pdf)

|

* the [offcial RISC-V compliance tests](#Status) (*passing*)

|

* the [official RISC-V compliance tests](#Status) (*passing*)

|

* Configurable RISC-V-compliant CPU extensions

|

* Configurable RISC-V-compliant CPU extensions

|

* [`A`](#Atomic-memory-access-a-extension) - atomic memory access instructions (optional)

|

* [`A`](#Atomic-memory-access-a-extension) - atomic memory access instructions (optional)

|

* [`B`](#Bit-manipulation-instructions-B-extension) - Bit manipulation instructions (optional)

|

* [`B`](#Bit-manipulation-instructions-B-extension) - Bit manipulation instructions (optional)

|

* [`C`](#Compressed-instructions-C-extension) - compressed instructions (16-bit) (optional)

|

* [`C`](#Compressed-instructions-C-extension) - compressed instructions (16-bit) (optional)

|

* [`E`](#Embedded-CPU-version-E-extension) - embedded CPU (reduced register file size) (optional)

|

* [`E`](#Embedded-CPU-version-E-extension) - embedded CPU (reduced register file size) (optional)

|

| Line 53... |

Line 53... |

* [`PMP`](#Privileged-architecture---Physical-memory-protection-PMP) - physical memory protection (optional)

|

* [`PMP`](#Privileged-architecture---Physical-memory-protection-PMP) - physical memory protection (optional)

|

* [`HPM`](#Privileged-architecture---Hardware-performance-monitors-HPM-extension) - hardware performance monitors (optional)

|

* [`HPM`](#Privileged-architecture---Hardware-performance-monitors-HPM-extension) - hardware performance monitors (optional)

|

* Full-scale RISC-V microcontroller system / **SoC** [**NEORV32 Processor**](#NEORV32-Processor-Features) with optional submodules

|

* Full-scale RISC-V microcontroller system / **SoC** [**NEORV32 Processor**](#NEORV32-Processor-Features) with optional submodules

|

* optional embedded memories (instructions/data/bootloader, RAM/ROM) and caches

|

* optional embedded memories (instructions/data/bootloader, RAM/ROM) and caches

|

* timers (watch dog, RISC-V-compliant machine timer)

|

* timers (watch dog, RISC-V-compliant machine timer)

|

* serial interfaces (SPI, TWI, UART)

|

* serial interfaces (SPI, TWI, UARTs)

|

* general purpose IO and PWM channels

|

* general purpose IO and PWM channels

|

* external bus interface (Wishbone / [AXI4](#AXI4-Connectivity))

|

* external bus interface (Wishbone / [AXI4](#AXI4-Connectivity))

|

* subsystem for custom co-processors

|

* subsystem for custom co-processors

|

* [more ...](#NEORV32-Processor-Features)

|

* [more ...](#NEORV32-Processor-Features)

|

* Software framework

|

* Software framework

|

| Line 110... |

Line 110... |

* Further size and performance optimization

|

* Further size and performance optimization

|

* Further expand associativity configuration of instruction cache (4x/8x set-associativity)?

|

* Further expand associativity configuration of instruction cache (4x/8x set-associativity)?

|

* Add data cache?

|

* Add data cache?

|

* Burst mode for the external memory/bus interface?

|

* Burst mode for the external memory/bus interface?

|

* RISC-V `F` (using [`Zfinx`](https://github.com/riscv/riscv-zfinx/blob/master/Zfinx_spec.adoc)?) CPU extension (single-precision floating point)

|

* RISC-V `F` (using [`Zfinx`](https://github.com/riscv/riscv-zfinx/blob/master/Zfinx_spec.adoc)?) CPU extension (single-precision floating point)

|

|

* RISC-V `K` CPU extension: [Crypto](https://github.com/riscv/riscv-crypto)

|

* Add template (HW module + SW intrinsics skeleton) for custom instructions?

|

* Add template (HW module + SW intrinsics skeleton) for custom instructions?

|

* Implement further RISC-V CPU extensions?

|

* Implement further RISC-V CPU extensions?

|

* More support for FreeRTOS (like *all* traps)?

|

* More support for FreeRTOS?

|

* Port additional RTOSs (like [Zephyr](https://github.com/zephyrproject-rtos/zephyr) or [RIOT](https://www.riot-os.org))?

|

* Port additional RTOSs (like [Zephyr](https://github.com/zephyrproject-rtos/zephyr) or [RIOT](https://www.riot-os.org))?

|

* Add debugger ([RISC-V debug spec](https://github.com/riscv/riscv-debug-spec))?

|

* Add debugger ([RISC-V debug spec](https://github.com/riscv/riscv-debug-spec))?

|

* Add encryption/decryption/hash accelerator (maybe [XTEA](https://en.wikipedia.org/wiki/XTEA))?

|

|

* ...

|

* ...

|

* [Ideas?](#ContributeFeedbackQuestions)

|

* [Ideas?](#ContributeFeedbackQuestions)

|

|

|

|

|

|

|

| Line 138... |

Line 138... |

|

|

* processor-internal data and instruction memories (**DMEM** / **IMEM**) & cache (**iCACHE**)

|

* processor-internal data and instruction memories (**DMEM** / **IMEM**) & cache (**iCACHE**)

|

* bootloader (**BOOTLDROM**) with UART console and automatic application boot from SPI flash option

|

* bootloader (**BOOTLDROM**) with UART console and automatic application boot from SPI flash option

|

* machine system timer (**MTIME**), RISC-V-compliant

|

* machine system timer (**MTIME**), RISC-V-compliant

|

* watchdog timer (**WDT**)

|

* watchdog timer (**WDT**)

|

* universal asynchronous receiver and transmitter (**UART**) with simulation output option via text.io

|

* two independent universal asynchronous receiver and transmitter (**UART0** & **UART1**) with fast simulation output option

|

* 8/16/24/32-bit serial peripheral interface controller (**SPI**) with 8 dedicated chip select lines

|

* 8/16/24/32-bit serial peripheral interface controller (**SPI**) with 8 dedicated chip select lines

|

* two wire serial interface controller (**TWI**), with optional clock-stretching, compatible to the I²C standard

|

* two wire serial interface controller (**TWI**), with optional clock-stretching, compatible to the I²C standard

|

* general purpose parallel IO port (**GPIO**), 32xOut & 32xIn, with pin-change interrupt

|

* general purpose parallel IO port (**GPIO**), 32xOut & 32xIn, with pin-change interrupt

|

* 32-bit external bus interface, Wishbone b4 compliant (**WISHBONE**), *standard* or *pipelined* handshake/transactions mode

|

* 32-bit external bus interface, Wishbone b4 compliant (**WISHBONE**), *standard* or *pipelined* handshake/transactions mode

|

* wrapper for **AXI4-Lite Master Interface** (see [AXI Connectivity](#AXI4-Connectivity))

|

* wrapper for **AXI4-Lite Master Interface** (see [AXI Connectivity](#AXI4-Connectivity))

|

| Line 335... |

Line 335... |

| PWM | Pulse-width modulation controller | 71 | 69 | 0 | 0 |

|

| PWM | Pulse-width modulation controller | 71 | 69 | 0 | 0 |

|

| SPI | Serial peripheral interface | 138 | 124 | 0 | 0 |

|

| SPI | Serial peripheral interface | 138 | 124 | 0 | 0 |

|

| SYSINFO | System configuration information memory | 11 | 10 | 0 | 0 |

|

| SYSINFO | System configuration information memory | 11 | 10 | 0 | 0 |

|

| TRNG | True random number generator | 132 | 105 | 0 | 0 |

|

| TRNG | True random number generator | 132 | 105 | 0 | 0 |

|

| TWI | Two-wire interface | 77 | 46 | 0 | 0 |

|

| TWI | Two-wire interface | 77 | 46 | 0 | 0 |

|

| UART | Universal asynchronous receiver/transmitter | 176 | 132 | 0 | 0 |

|

| UART0/1 | Universal asynchronous receiver/transmitter 0/1 | 176 | 132 | 0 | 0 |

|

| WDT | Watchdog timer | 60 | 45 | 0 | 0 |

|

| WDT | Watchdog timer | 60 | 45 | 0 | 0 |

|

| WISHBONE | External memory interface | 129 | 104 | 0 | 0 |

|

| WISHBONE | External memory interface | 129 | 104 | 0 | 0 |

|

|

|

|

|

### NEORV32 Processor - Exemplary FPGA Setups

|

### NEORV32 Processor - Exemplary FPGA Setups

|

| Line 488... |

Line 488... |

This overview is just a short excerpt from the *Let's Get It Started* section of the NEORV32 documentary:

|

This overview is just a short excerpt from the *Let's Get It Started* section of the NEORV32 documentary:

|

|

|

[:page_facing_up: NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf)

|

[:page_facing_up: NEORV32 data sheet](https://raw.githubusercontent.com/stnolting/neorv32/master/docs/NEORV32.pdf)

|

|

|

|

|

### Toolchain

|

### 1. Get Toolchain

|

|

|

At first you need the **RISC-V GCC toolchain**. You can either [download the sources](https://github.com/riscv/riscv-gnu-toolchain)

|

At first you need a **RISC-V GCC toolchain**. You can either [download the sources](https://github.com/riscv/riscv-gnu-toolchain)

|

and build the toolchain by yourself, or you can download a prebuilt one and install it.

|

and build the toolchain by yourself, or you can download a prebuilt one and install it.

|

|

|

To build the toolchain by yourself, follow the official [build instructions](https://github.com/riscv/riscv-gnu-toolchain).

|

To build the toolchain by yourself, follow the official [build instructions](https://github.com/riscv/riscv-gnu-toolchain).

|

Make sure to use the `ilp32` or `ilp32e` ABI.

|

Make sure to use the `ilp32` or `ilp32e` ABI.

|

|

|

**Alternatively**, you can download a prebuilt toolchain. I have uploaded the toolchains I am using to GitHub. These toolchains

|

**Alternatively**, you can download a prebuilt toolchain. I have uploaded the toolchains I am using to GitHub. These toolchains

|

were compiled on a 64-bit x86 Ubuntu 20.04 LTS (Ubuntu on Windows, actually). Download the toolchain of choice:

|

were compiled on a 64-bit x86 Ubuntu 20.04 LTS (Ubuntu on Windows, actually). Download the toolchain of choice:

|

[:octocat: github.com/stnolting/riscv-gcc-prebuilt](https://github.com/stnolting/riscv-gcc-prebuilt)

|

[:octocat: github.com/stnolting/riscv-gcc-prebuilt](https://github.com/stnolting/riscv-gcc-prebuilt)

|

|

|

You can also use the toolchains provided by [SiFive](https://github.com/sifive/freedom-tools/releases). These are 64-bit toolchains that can also emit 32-bit

|

You can also use the toolchains provided by [SiFive](https://github.com/sifive/freedom-tools/releases). These are 64-bit toolchains that can also emit 32-bit

|

RISC-V code. They were compiled for more sophisticated machines (`imac`) so the according hardware extensions are *mandatory*

|

RISC-V code. They were compiled for more sophisticated machines (`rv32imac`) so make sure the according NEORV32 hardware extensions are enabled.

|

|

|

:warning: Keep in mind that – for instance – a `rv32imc` toolchain only provides library code compiled with compressed and

|

:warning: Keep in mind that – for instance – a `rv32imc` toolchain only provides library code compiled with compressed and

|

`mul`/`div` instructions! Hence, this code cannot be executed (without emulation) on an architecture without these extensions!

|

`mul`/`div` instructions! Hence, this code cannot be executed (without emulation) on an architecture without these extensions!

|

|

|

|

To check everything works fine, make sure `GNU Make` and a native `GCC` compiler are installed.

|

|

Test the installation of the RISC-V toolchain by navigating to an [example program project](https://github.com/stnolting/neorv32/tree/master/sw/example) like

|

|

`sw/example/blink_led` and running:

|

|

|

|

neorv32/sw/example/blink_led$ make check

|

|

|

### Dowload the NEORV32 Project

|

|

|

### 2. Dowload the NEORV32 Project

|

|

|

Get the sources of the NEORV32 Processor project. The simplest way is using `git clone` (suggested for easy project updates via `git pull`):

|

Get the sources of the NEORV32 Processor project. The simplest way is using `git clone` (suggested for easy project updates via `git pull`):

|

|

|

$ git clone https://github.com/stnolting/neorv32.git

|

$ git clone https://github.com/stnolting/neorv32.git

|

|

|

Alternatively, you can either download a specific [release](https://github.com/stnolting/neorv32/releases) or get the most recent version

|

Alternatively, you can either download a specific [release](https://github.com/stnolting/neorv32/releases) or get the most recent version

|

of this project as [`*.zip` file](https://github.com/stnolting/neorv32/archive/master.zip).

|

of this project as [`*.zip` file](https://github.com/stnolting/neorv32/archive/master.zip).

|

|

|

|

|

### Create a new Hardware Project

|

### 3. Create a new Hardware Project

|

|

|

Create a new project with your FPGA design tool of choice. Add all the `*.vhd` files from the [`rtl/core`](https://github.com/stnolting/neorv32/blob/master/rtl)

|

Create a new project with your FPGA design tool of choice. Add all the `*.vhd` files from the [`rtl/core`](https://github.com/stnolting/neorv32/blob/master/rtl)

|

folder to this project. Make sure to add these files to a **new design library** called `neorv32`.

|

folder to this project. Make sure to add these files to a **new design library** called `neorv32`.

|

|

|

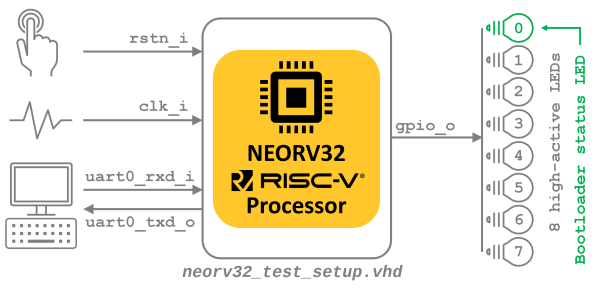

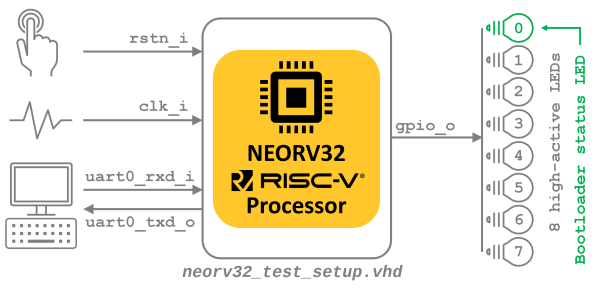

You can either instantiate the [processor's top entity](https://github.com/stnolting/neorv32/blob/master/rtl/core/neorv32_top.vhd) or one of its

|

You can either instantiate the [processor's top entity](https://github.com/stnolting/neorv32/blob/master/rtl/core/neorv32_top.vhd) or one of its

|

| Line 529... |

Line 535... |

you can use the simple [test setup](https://github.com/stnolting/neorv32/blob/master/rtl/top_templates/neorv32_test_setup.vhd) as top entity.

|

you can use the simple [test setup](https://github.com/stnolting/neorv32/blob/master/rtl/top_templates/neorv32_test_setup.vhd) as top entity.

|

|

|

|

|

|

|

|

|

This test setup instantiates the processor and implements most of the peripherals and some ISA extensions. Only the UART lines, clock, reset and some GPIO output signals are

|

This test setup instantiates the processor and implements most of the peripherals and some ISA extensions. Only the UART0 lines, clock, reset and some GPIO output signals are

|

propagated as actual entity signals. Basically, it is a FPGA "hello world" example:

|

propagated as actual entity signals. Basically, it is a FPGA "hello world" example:

|

|

|

```vhdl

|

```vhdl

|

entity neorv32_test_setup is

|

entity neorv32_test_setup is

|

port (

|

port (

|

-- Global control --

|

-- Global control --

|

clk_i : in std_ulogic := '0'; -- global clock, rising edge

|

clk_i : in std_ulogic := '0'; -- global clock, rising edge

|

rstn_i : in std_ulogic := '0'; -- global reset, low-active, async

|

rstn_i : in std_ulogic := '0'; -- global reset, low-active, async

|

-- GPIO --

|

-- GPIO --

|

gpio_o : out std_ulogic_vector(7 downto 0); -- parallel output

|

gpio_o : out std_ulogic_vector(7 downto 0); -- parallel output

|

-- UART --

|

-- UART0 --

|

uart_txd_o : out std_ulogic; -- UART send data

|

uart0_txd_o : out std_ulogic; -- UART0 send data

|

uart_rxd_i : in std_ulogic := '0' -- UART receive data

|

uart0_rxd_i : in std_ulogic := '0' -- UART0 receive data

|

);

|

);

|

end neorv32_test_setup;

|

end neorv32_test_setup;

|

```

|

```

|

|

|

|

|

### Check the Toolchain

|

### 4. Compile an Example Program

|

|

|

Make sure `GNU Make` and a native `GCC` compiler are installed. To test the installation of the RISC-V toolchain navigate to an example project like

|

|

`sw/example/blink_led` and run:

|

|

|

|

neorv32/sw/example/blink_led$ make check

|

|

|

|

|

The NEORV32 project includes several [example program project](https://github.com/stnolting/neorv32/tree/master/sw/example) from

|

|

which you can start your own application. There are example programs to check out the processor's peripheral like I2C or the true-random number generator.

|

|

And yes, there is also a port of [Conway's Game of Life](https://github.com/stnolting/neorv32/tree/master/sw/example/game_of_life) available! :wink:

|

|

|

### Compiling an Example Program

|

Simply compile one of these projects using

|

|

|

The NEORV32 project includes some [example programs](https://github.com/stnolting/neorv32/tree/master/sw/example) from

|

|

which you can start your own application. Simply compile one of these projects. This will create a NEORV32

|

|

*executable* `neorv32_exe.bin` in the same folder:

|

|

|

|

neorv32/sw/example/blink_led$ make clean_all exe

|

neorv32/sw/example/blink_led$ make clean_all exe

|

|

|

|

This will create a NEORV32 *executable* `neorv32_exe.bin` in the same folder, which you can upload via the bootloader.

|

|

|

### Upload the Executable via the Bootloader

|

|

|

|

You can upload a generated executable directly from the command line using the makefile's `upload` target. Replace `/dev/ttyUSB0` with

|

|

the according serial port.

|

|

|

|

sw/exeample/blink_example$ make COM_PORT=/dev/ttyUSB0` upload

|

### 5. Upload the Executable via the Bootloader

|

|

|

A more "secure" way is to use a dedicated terminal program. This allows to directly interact with the bootloader console.

|

Connect your FPGA board via UART to your computer and open the according port to interface with the fancy NEORV32 bootloader. The bootloader

|

Connect your FPGA board via UART to your computer and open the according port to interface with the NEORV32 bootloader. The bootloader

|

|

uses the following default UART configuration:

|

uses the following default UART configuration:

|

|

|

* 19200 Baud

|

* 19200 Baud

|

* 8 data bits

|

* 8 data bits

|

* 1 stop bit

|

* 1 stop bit

|

* No parity bits

|

* No parity bits

|

* No transmission / flow control protocol (raw bytes only)

|

* No transmission / flow control protocol (raw bytes only)

|

* Newline on `\r\n` (carriage return & newline) - also for sent data

|

* Newline on `\r\n` (carriage return & newline) - also for sent data

|

|

|

Use the bootloader console to upload the `neorv32_exe.bin` executable and run your application image.

|

Use the bootloader console to upload the `neorv32_exe.bin` executable gerated during application compiling and run your application.

|

|

|

```

|

```

|

<< NEORV32 Bootloader >>

|

<< NEORV32 Bootloader >>

|

|

|

BLDV: Nov 7 2020

|

BLDV: Nov 7 2020

|