Raptor64

Project maintainers

Details

Created: Apr 26, 2012

Updated: Feb 16, 2013

SVN Updated: Feb 18, 2013

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:Verilog

Development status:Planning

Additional info:

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

Raptor64 is a 64-bit multi-context RISC cpu that supports hyper-threading. There are 16 register sets that the processor automatically switches between at high speed. The processor is fully pipelined with a nine-stage pipeline. Stages: IF/RF/EX/M1/M2/M3/M4/WB/TR. Communication with memory is via a 32 bit MIG bus. The processor has a 8kB instruction cache and 16kB data cache. Also included is a 16 entry TLB for memory management. The processor uses 32 bit instructions.

I've created two versions of the processor a non-hyper-threaded version (sc) in addition to the hyper-threaded multi-context(mc) one.

Features

- 32 entry 64 bit general register file

- 32 bit opcodes (4 per 128 bits)

- SQRT,Multiply/Divide/bit field/ + all the regulars

- conditional move, exec,

- explicit I/O instructions ( also useful for uncached access)

- immediate constants may be built using SETLO,SETMID,SETHI instructions

- two address modes, displacement (d15[ra]) and scaled indexed (d2[ra+rb*scale])

- 16 segmentation registers

- SimpleMMU - 32 tasks supported with mapping of 128MB space into 256kB pages

- 64 single bit semaphores

- 8kiB instruction cache, 16kiB data cache

- 8 way 8 entry set associative TLB

- single cycle execution of most instructions (loads stall the pipeline)

- branch prediction with a 256 entry branch history table

- return address stack prediction

- internal Harvard architecture

- communicates externally using a 64-bit WISHBONE bus

Software

In the works is currently a high level language compiler for a language similar to 'C'. Several additional keywords have been added (eg. interrupt). Well I finally fed the output of the compiler through the assembler. A couple of bug fixes later the sieve is able to run from SD Card.

There is also an assembler (also a work in progress).

Tiny Basic is available in the boot rom. Works with a few bugs yet.

Status

Currently the processor is running code in an FPGA. The bootrom is slowly expanding. Numerous software and processor fixes have taken place. Still a long way to go. The processor is being revamped to use a 32 bit ISA, it was originally a 42 bit ISA.

The core is running on an Atlys board, and now able to load a boot program from an SD Card. Hopefully that will speed the software development up. Prior, the only software was updated by updating a Verilog source file, requiring the entire system to be rebuilt for a software update.

The ISA is still under constant review; it may change to use an 8-bit master opcode field as opposed to 7-bits. There's lots of instructions I'd like to add, and no room with only 7 bits.

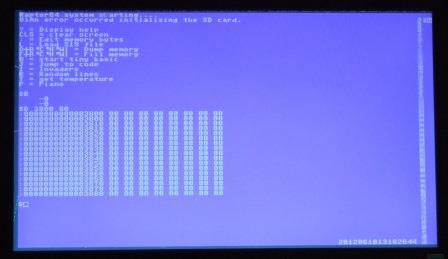

Pics