Theia: ray graphic processing unit

Architecture Overview

THEIA Architecture Overview

Theia has a multicore architecture approach.

Each core is an independent physical entity, capable of performing by itself the full RENDER of an image.

Theia's architecture uses multiple cores working simultaneously, to benefit from the parallelism of ray cast.

Each core runs a local copy of the shader code, written on THEIA's assembly programming language, gets its

inputs from the T-Memory and Vertex Memory, and writes its output into one of the banks of the O-Memory.

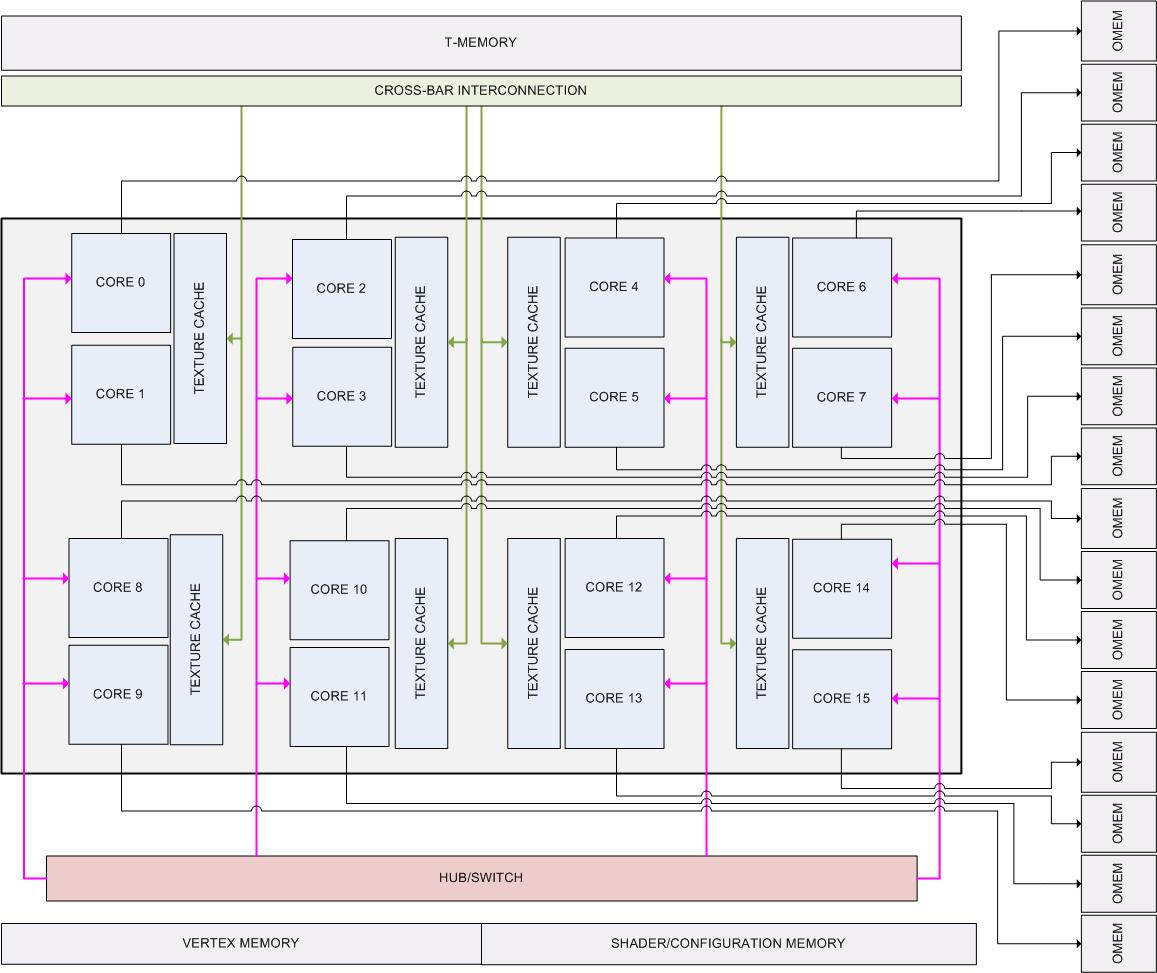

GPU Architecture Block diagram

The Next diagram ilustrates the GPU architecure.

The previous diagram shows a configuration with 16 cores. This number of

cores may be different from the current SVN trunk, however the RTL

has been written to allow modifying this number.

VERTEX MEMORY stores the geometry primitives which describe the

scene. The HUB/SWITCH Block broadcasts the current geometry primitive

to all the cores.

T-MEMORY is an n-way interleaved memory which stores the textures

Each core has the ability to read from T-MEMORY. The cores can not

write into T-MEMORY. A Cross-Bar interconnects each core with the

T-MEMORY to maximize concurrent reads. Each pair of cores also shares

a TEXTURE CACHE to further accelerate the texture reading.

OMEM is a collection of N Memory banks, where N is equal to the

number of cores. Each core is assign a unique OMEM Bank. Each core

writes it's results into its corresponding OMEM. Each core can only

access 1 OMEM block for writing. The cores can not read from OMEM.

Each core has a local copy of the Code to execute. The internal CORE

memory is not shown for simplicity.

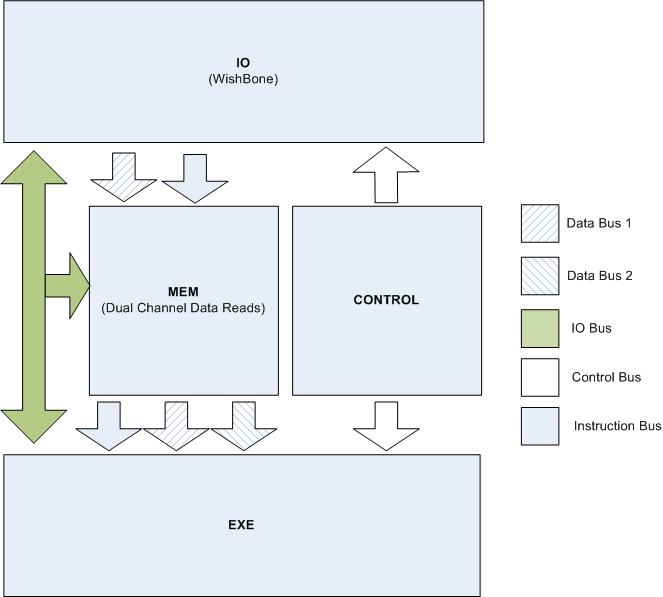

CORE Architecture Block diagram

Each core has the following basic building blocks.

Each core has 4 main blocks: EXE, IO, CONTROL and MEM.

MEM: Contains a Code default ROM, a user code RAM which partially or totally overwrites the ROM, as well as Registers and IO mapped memory.

EXE: Execution unit, contains Fetch unit, decode Unit, ALU and Write Back. It is Pipe-lined.

IO: Input output Unit. Implement Wishbone master and slave blocks.

CONTROL: Main control FSM for the core.