Edge Processor (MIPS)

Project maintainers

Details

Name: edge

Created: Mar 1, 2014

Updated: Jun 29, 2014

SVN Updated: Mar 2, 2014

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Created: Mar 1, 2014

Updated: Jun 29, 2014

SVN Updated: Mar 2, 2014

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Star4you like it: star it!

Other project properties

Category:Processor

Language:Verilog

Development status:Alpha

Additional info:

WishBone compliant: No

WishBone version: n/a

License: LGPL

Language:Verilog

Development status:Alpha

Additional info:

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

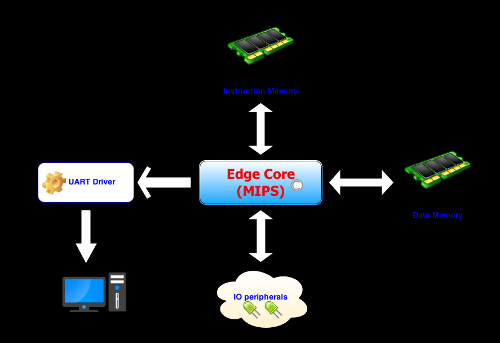

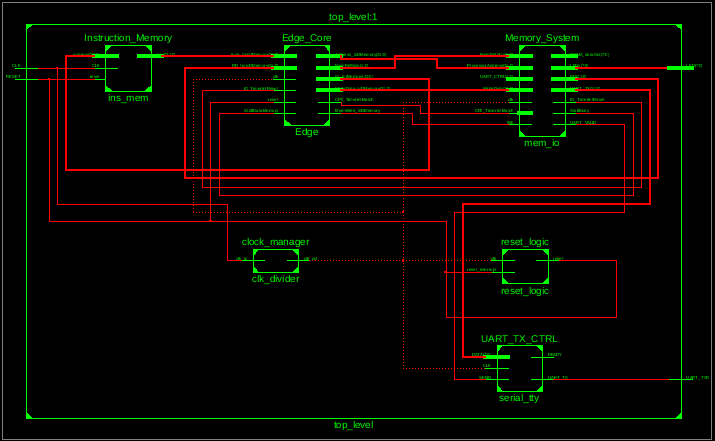

Edge is a microarchitecture implementation for mips1 ISA.

It has a 32 bit datapath divided into five pipeline stages operating at 50 MHz frequency.

Supporting timer and other interrupt types and exceptions is implemented through co-processor0.

Edge has been tested and verified on Atlys that has a Spartan-6 XC6SLX45 FPGA.

For the Atlys board, UART driver is provided to communicate with PC at 115200 baud rate.

Youtube link for simple C programs running [1]

https://www.youtube.com/watch?v=Hxwq2KWzycU

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.