Classic NES controller interface

Project maintainers

Details

Created: Mar 23, 2021

Updated: Mar 24, 2021

SVN Updated: Mar 24, 2021

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:Verilog

Development status:Stable

Additional info:

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

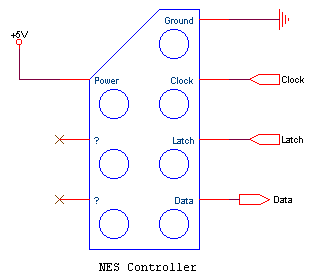

Nintendo NES controller serial -> parallel IP.

This IP interfaces up to TWO (or more, if you like) old-school (so not the USB ones) controllers and performs the serial to parallel conversion upon receiving a 'frame' start bit. Once the 'busy' flag goes low the results will appear on q0 and q1. Reading q0 and q1 while the controller is busy will yield partial / old results. The order keys appear in are:

- bit #0 - right

- bit #1 - left

- bit #2 - down

- bit #3 - up

- bit #4 - select

- bit #5 - start

- bit #6 - b

- bit #7 - a

NOTE: The original controller uses a 5V shift register which means you'll have to use some sort of level-shifter if you want to use it at 3.3v. Pull-ups are built into the controller so the signals are active low.

Pinouts can be found on the internet, or here:

The url of the svn repository is: https://opencores.org/websvn/listing/nescontroller/nescontroller