openGFX430

Project maintainers

Details

Created: Aug 3, 2016

Updated: Mar 21, 2021

SVN Updated: Nov 3, 2016

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:Verilog

Development status:Alpha

Additional info:FPGA proven

WishBone compliant: No

WishBone version: n/a

License: BSD

Overview

Introduction

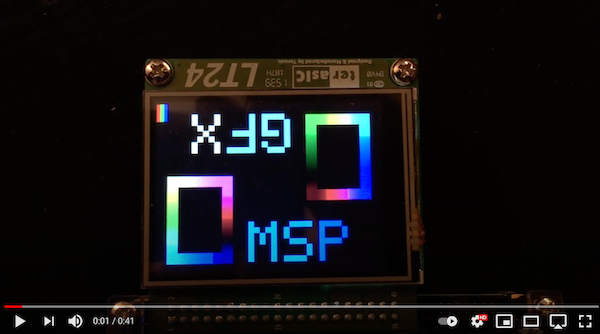

The openGFX430 is a synthesizable Graphic controller written in Verilog and tailored for the openMSP430 core.

An example implementation based on the DE0-Nano-SoC and LT24 daughter board from Terasic can be found in the openMSP430 FPGA section (see here).

Features & TODOs

Features

Support of the following graphic modes:

16bpp

- 8bpp

- 4bpp

- 2bpp

1bpp

Smart address generation unit for fast indirect memory access.

- GPU allowing hardware FILL, COPY and COPY_TRANSPARENT operations.

- Supports the LT24 Terasic daughter card.

TODOs

In no particular priority order:

RTL:

Add support popular video interfaces (i.e. probably SPI and VGA in addition to LT24).

- Character processing unit.

Hardware cursor

Others:

Add proper block level verification environment.

- Documentation.

Download

Design

The complete tar archive of the project can be downloaded here (OpenCores account required).

The following SVN command can be run from a console (or GUI):

svn export http://opencores.org/ocsvn/opengfx430/opengfx430/trunk/ opengfx430

ChangeLog

- The Core's ChangeLog lists the Video Controller updates.

- Subscribe to the following RSS feed to keep yourself informed about ALL updates.