2D FHT

Project maintainers

Details

Name: two_dimensional_fast_hartley_transform

Created: May 1, 2009

Updated: Aug 25, 2017

SVN Updated: Jul 28, 2011

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 1 reported / 0 solved

Created: May 1, 2009

Updated: Aug 25, 2017

SVN Updated: Jul 28, 2011

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 1 reported / 0 solved

Star7you like it: star it!

Other project properties

Category:Arithmetic core

Language:Verilog

Development status:Alpha

Additional info:FPGA proven

WishBone compliant: No

WishBone version: n/a

License: LGPL

Language:Verilog

Development status:Alpha

Additional info:FPGA proven

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

RTL Verilog code to perform Two Dimensional Fast Hartley Transform (2D-FHT) for 8x8 points.

Presented algorithm is FHT with decimation in frequency domain.

Main Features

Discrete Hartley Transform is used in a wide variety of signal processing applications such as filtering, convolution, correlation, compression and so on.

The most popular usage of the Hartley Transform is image processing applications.

Functional Description

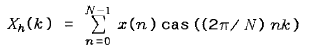

The N-point Discrete Hartley Transform is given by the next formula:

where

.

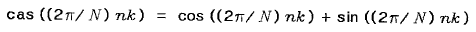

.RTL Verilog code which is presented here was designed to calculate 2D-FHT (8x8 points) algorithm with decimation in frequency domain.

Block Diagram

Verification

This IP was verified using OVM-like verification environment. Main focus was made to compare RTL output data with golden reference model output data.

As a result: RTL is fully identical with golden reference model.

Implementation Result

| Xilinx FPGA | Slices | DSP48 | BRAM | Freq., MHz |

|---|---|---|---|---|

| Virtex-4 xc4vlx60 | 818 | 4 | 1 | 200 |

Status

RTL Verilog release of the Two Dimensional Fast Hartley Transform Algorithm.

Verilog RTL - 1st version released. Refer to repository for latest revision.

Verification - If you have any question please feel free to send me message.

Testbench - If you have any question please feel free to send me message.

Documentation - If you have any question please feel free to send me message.

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.