UART observer

Project maintainers

Details

Created: Apr 21, 2018

Updated: Sep 22, 2018

SVN Updated: Oct 21, 2018

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:Verilog

Development status:Stable

Additional info:

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

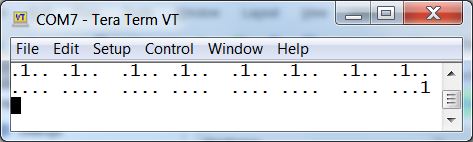

This module observes binary inputs, representing them in a user-friendly way inside UART terminal. The output is formatted, human readable and the content is only updated (re-sent) when the inputs change. Terminal control sequences are used for producing more user friendly output:

It is connected the way

wire [63:0] observables; // You can also have more bits if required uart_observer #(.CLOCK_FREQ (90_000_000), .BAUDS(921600), .BITS(64) ) U0( // Clock .clk (CLK_AM), // Values to observer .observables(observables), // UART .TXD(USB_UART_RX_FPGA_TX_LS), // data .RTS(USB_UART_RTS_O_B_LS), // request to send .CTS(USB_UART_CTS_I_B_LS) // clear to send );

The module accepts the binary vector and clock as input and provides three standard UART (8N1) control lines as output (request, permission to send and data). It is self-sufficient and does not need any additional frameworks or IP cores to run. As all logic is implemented in, the module could potentially use any free input and two outputs or be replicated multiple times, regardless of how many (or if any) dedicated UART devices are available.

The module has been tested on the physical Kintex Ultrascale KCU116 board with speeds up to 921600 bauds and can be used for observing much more binary data than it is possible with the help of LEDs on the evaluation board. This is ideal for projects that focus on logic rather than on timing. Hardware specific dependencies are in constraint files only, the module should work also with other FPGAs (clock frequency is the parameter).

The project provides the uart observer module and a simple demo module that uses it and constraint files that work with KCU116, both written in Verilog. The demonstrator uses the user push buttons on the board as the input.

These plain text files can be easily imported into Vivado or any other tool. In the provided constraint files the clock is wired to the 90 MHz FPGA_EMCCLK on the board.

The later releases also contain UART reader that takes input from the same terminal. The observer input is now connected to the output of this reader.