ZTEX USB-FPGA Module 2.13

Project maintainers

Details

Name: usb_fpga_2_13

Created: Apr 10, 2014

Updated: Jul 31, 2014

SVN Updated: Apr 11, 2014

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Created: Apr 10, 2014

Updated: Jul 31, 2014

SVN Updated: Apr 11, 2014

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Star1you like it: star it!

Other project properties

Category:Prototype board

Language:Verilog

Development status:Stable

Additional info:

WishBone compliant: No

WishBone version: n/a

License: GPL

Language:Verilog

Development status:Stable

Additional info:

WishBone compliant: No

WishBone version: n/a

License: GPL

Description

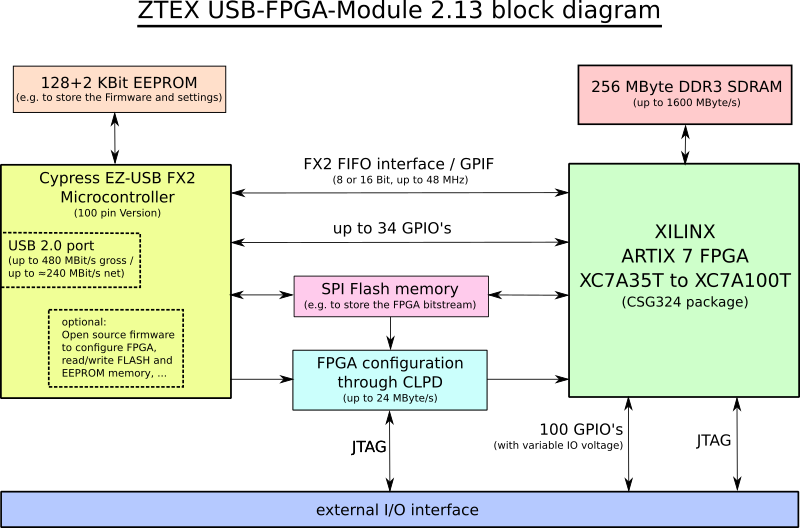

USB-FPGA Module 2.13 is an Artix 7 FPGA Board with USB 2.0 controller, 256 MB DDR3 SDRAM, Flash, many GPIO's and on-board voltage regulators. It's available in 4 variants with different FPGA types: XC7A35T, XC7A50T, XC7A75T and XC7A100T

Features

- Four Xilinx Artix 7 FPGA variants: XC7A35T, XC7A50T, XC7A75T and XC7A100T

- USB 2.0 interface using Cypress CY7C68013A EZ-USB FX2 Microcontroller (100 pin version)

- Four Xilinx Artix 7 FPGA variants: XC7A35T, XC7A50T, XC7A75T and XC7A100T

- External I/O connector (consisting in two female 2x32 pin headers with 2.54mm grid) provides:

- 100 General Purpose I/O's (GPIO) connected to FPGA

- JTAG signals

- Reset signal

- External power (4.5 V .. 16 V) input

- 3.3V output

- I/O voltage output or input

-

256 MByte DDR3 SDRAM:

- Up to 400 MHz clock frequency

- 16 Bit bus width

- Up to 1600 MByte/s data rate

- Usable with the Xilinx Memory Interface Generator (MIG), examples are included in the SDK

- 128 MBit on-board Flash memory

- Allows Bitstream loading from Flash to FPGA (up to 16.5 MByte/s)

- Accessible from EZ-USB FX2 and from FPGA

- 128 Kbit EEPROM memory (e.g. used to store the EZ-USB firmware)

- 2 Kbit MAC-EEPROM: contains a unique non erasable MAC-address and is used to store firmware settings

- Fast FPGA configuration via USB using CPLD: up to 24 MByte/s

- On-Board power supply:

- 3.3 V: 2000 mA

- 1.8 V: 1000 mA

- 1.5 V: 2000 mA

- 1.0 V; 4000 mA

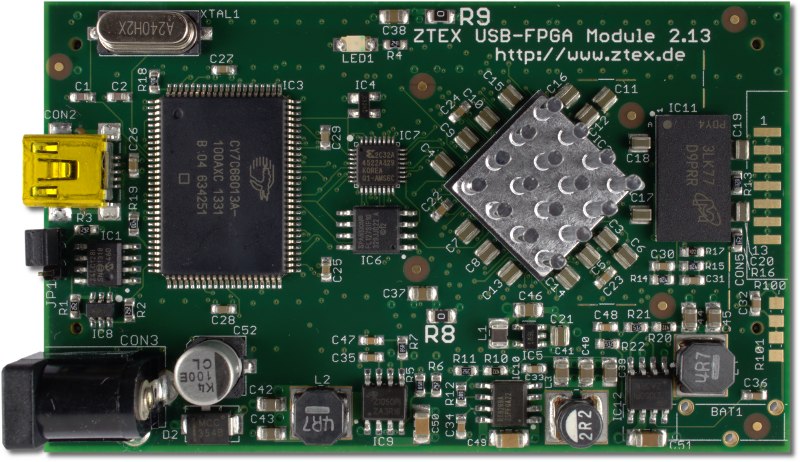

- XC7A50T, XC7A75T and XC7A100T variants only: Heat sink for high performance / high speed applications included

- Optional:

- Battery to store a key for bitstream encryption

- On-board JTAG connector

Block Diagram

Images

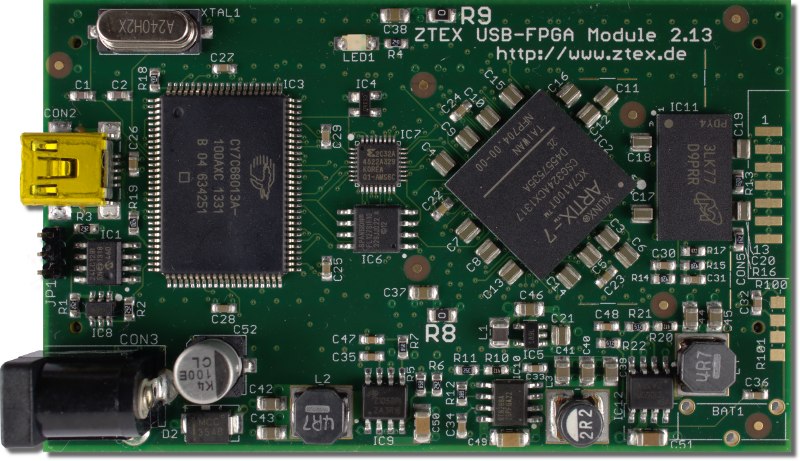

Click on the images for larger versions.

Top side of USB-FPGA Module 2.13d with Artix 7 XC7A100T FPGA, 256 MB DDR3 SDRAM and USB 2.0 interface. |

USB-FPGA Module 2.13 with heat sink as delivered with XC7A50T to XC7A100T variants. |

References

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.