v586

Project maintainers

Details

Created: Oct 12, 2014

Updated: Oct 16, 2016

SVN Updated: Oct 15, 2016

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:Verilog

Development status:Beta

Additional info:FPGA proven

WishBone compliant: No

WishBone version: n/a

License: BSD

Description

This project is a soft processor core compatible with 586 instruction set.

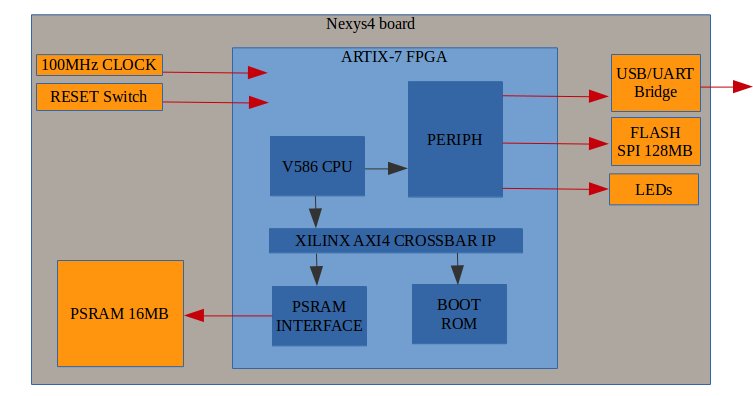

The processor core has AXI4 interface and uses XILINX AXI4 IPs such as AXI4 CROSSBAR and MIG with AXI 4 interface.

The platform boots linux kernel with a ramdisk contained in the SPI flash.

The package contains code for NEXYS4 DDR and ESA-11-7a100t-v1.1 boards , with artix7 device inside

external DDR2/3 size 128MB DDR and 128Mbit SPI Flash.

** CORE DETAILS:

* Features:

- 586 instruction set implementation, conditional mov added.

- MMU with protected and paged mode supported with 4KB page size.

- TLB 16 entries.

- CPUID (0x0617)and CMPXCHG8B are implemented, with conditional mov.

- pre-fetch queue is 32 bytes long.

- 16kB Instruction cache, 16kB Data cache, 128bit loaded at once into prefetch queue.

- Hardware multiplication and Division.

- 32 bit AXI4 interface with bursts.

- ~17DMIPS or ~30500 dhrystones v2.1 @ 100MHz with -O2 option under gcc 4.8, no register.

* Known limitations:

- no FPU, but emulation mechanism with "device not available" fault #7, whetsone gives 0.125 MIPS score with emulation.

- some instruction are missing, but not used in Linux/GCC : like the decimal adjust.

- Protected and Paged mode are supported, there are some limitation in the protected mode implementation like segment limit.

- bits and features for MSR/TSC/PAE/NX bit not implemented.

- MMU page size is 4KB , no PSE / PSE36 bit supported.

- Segment prefix in protected mode are the default or GS descriptor, FS prefix in protected mode is not used in Linux 32b.

**PLATFORM DETAILS:

HARDWARE:

- RESET is the CPU Push buttton on NEXYS4.

- Minimal set of peripherals : timer and interrupt controller.

- one 16750 interface with 64byte fifo , re-used from uart16750 opencore project.

- IT87xx SuperIO chip implemented only for GPIOs parts. 16x GPIOs Connected to leds of nexys4.

( GPIO Linux driver fot IT87 compatible with userspace interface. )

- SPI interface serial-in , parallel out

- Bus Interface Unit to arbitrate between instruction fetch and data operations and

also MMU specific operation like updating the bit for page directory/table entries.

- The Platform mapping in the Artix7-100 fills 42% and clock frequency used in the project is 100MHz

- clock divider for timer and uart are hard coded for 100MHz base clock.

- if an SD car is present on NEXYS4 DDR SD slot it can be mounted with "mount /dev/mmcblk /mnt"

SOFTWARE:

- internal ROM to boot and copy SPI flash into RAM, provide minimal description

and configuration for Linux with command line to configure TTY console on uart

at 115200 baud.

- SPI image with Linux 3.19 ( 3.17/3.14/3.12/2.6.x were tested as well) and initramfs

with busybox built from buildroot 2016.02 with dhrystone/whetstone/e2fs/micropython.

- Kernel has been built on regular PC UBUNTU 14.04LTS with regular GCC 4.8 as well.

- patch for linux and .config file for the kernel included, settings optimized for size and FPU emulation on plus device declaration.

Links

videos on youtube can be found here : https://www.youtube.com/channel/UCNbm8Bah54cwhedmCRWyXMAvideos