UART to Bus

UART to Bus

Project maintainers

Details

Name: uart2bus

Created: Feb 12, 2010

Updated: Dec 12, 2018

SVN Updated: Jan 19, 2017

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 12 reported / 9 solved

Created: Feb 12, 2010

Updated: Dec 12, 2018

SVN Updated: Jan 19, 2017

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 12 reported / 9 solved

Star26you like it: star it!

Other project properties

Category:Communication controller

Language:Verilog & VHDL

Development status:Mature

Additional info:Design done, FPGA proven, Specification done

WishBone compliant: No

WishBone version: n/a

License: BSD

Language:Verilog & VHDL

Development status:Mature

Additional info:Design done, FPGA proven, Specification done

WishBone compliant: No

WishBone version: n/a

License: BSD

Description

Have you ever needed a fast and easy way to test your new FPGA board?

You know you have all the interfaces but it will take time to finish the software or the verification just to start debugging.

This core might be what you are looking for.

The UART to Bus IP Core is a simple command parser that can be used to access an internal bus via a UART interface. The parser supports two modes of operation: text mode commands and binary mode commands. Text mode commands are designed to be used with a hyper terminal software and enable easy access to the internal bus. Binary mode commands are more efficient and also support buffered read & write operations with or without automatic address increment.

VHDL version now available

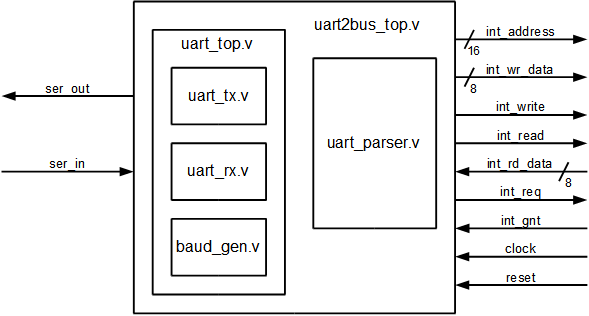

Block Diagram

For detailed information download the Core Specifications 1.0 document.

Synthesis Results

| Manufacturer | Family | Device | Device Utilization | Elements Utilization | Fmax |

|---|---|---|---|---|---|

| Xilinx | Spartan 3 | xc3s50-5pq208 | 25% | 195 Slices | >150MHz |

| Xilinx | Virtex 5 | xc5vlx30-3ff324 | 2% | 99 Slices | >200MHz |

| Altera | Cyclone III | ep3c5f256c6 | 5% | 235 LEs | >200MHz |

| Altera | Startix III | ep3sl50f484c2 | 165 Registers, 186 ALUTs | >200MHz | |

| Lattice* | MachXO | LCMXO2280C-4T144C | 10% | 116 Slices | >100MHz |

* Lattice device synthesis results provided by Paul V. Shatov

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.