high throughput and low area aes core

Project maintainers

Details

Created: Mar 3, 2010

Updated: Apr 1, 2012

SVN Updated: May 6, 2013

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:Verilog

Development status:Stable

Additional info:FPGA proven, Specification done

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

The High Throughput Low Area AES IP core implements the Rijndael encryption & decryption algorithm used in the AES standard. The standalone core implements the basic ECB mode described in publication 800-38A by NIST. Other modes can be easily implemented using the core.

The core implements both key expansion, required each time the key is changed (also after reset or power-up), and encryption/decryption algorithms. The core supports all three key lengths: 128, 192 & 256 bits, selected by an input signal. Encryption or decryption modes of operation are also selected on the fly using an input signal.

The core can achieve data rates of about 880Mbps with 256 bits key length, 1Gbps with 192 bits key length and 1.2Gbps with 128 bits key length when operated at a clock of 100MHz.

Test bench for basic simulation is provided to demonstrate the core functionality and interfaces. An additional test bench is supplied for verification of the core using the KAT test vectors files for ECB mode.

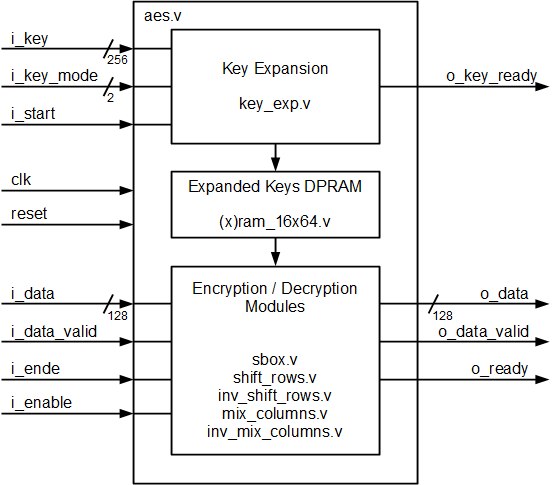

Block Diagram

Simplified core block diagram:

For detailed information download the Core Specifications 0.2 document.

Synthesis Results

| Manufacturer | Family | Device | Device Utilization | Elements Utilization | Fmax |

|---|---|---|---|---|---|

| Xilinx | Spartan 3 | xc3s1500-4fg456 | 23% | 3,110 Slices | >100MHz |

| Xilinx | Virtex 5 | xc5vlx30-3ff324 | 45% | 1,408 Slices | >135MHz |

| Altera | Cyclone III | ep3c10f256c6 | 44% | 4,657 LEs | >110MHz |

| Altera | Arria II GX | ep2agx45cu17i3 | 13% | 1,806 Registers 3,247 ALUTs |

>145MHz |