AHBmaster for FPGA of microsemi

Project maintainers

Details

Created: Jun 30, 2018

Updated: Jul 4, 2018

SVN Updated: Jul 4, 2018

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:VHDL

Development status:Alpha

Additional info:

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

microsemi用のAHBmaster.vhd

microsemiのIPコアのほとんどは、AMBA(AHB,APB)によるインタフェースで提供されているため、AMBA規格に対応したHDLを設計できれば応用を効かせることが期待できます。しかし、残念ながらmicrosemiはAHBmasterとなるIPコアをほとんど提供していません。

そこで、AHBmasterの開発(?)を行いました。

中身はmicrosemiが公開しているAHBmaster.vをVHDLコードに書き直したもので、適当にモデファイしています。

利用できるAMBAのバス通信は、バースト等はできずシングル転送のみです。

使い方(Usage)

microsemiのLiberoSocでプロジェクトを作成します。

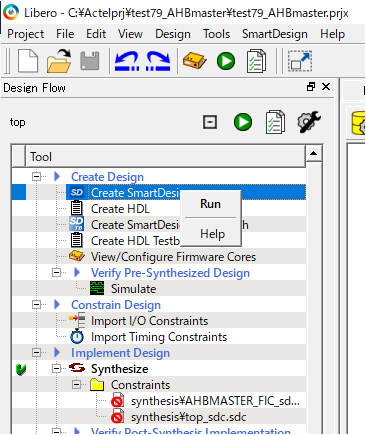

TOP層は、HDLではなくsmartgenで作成することをお薦めします。

理由としては、モジュール間の接続や変更が容易であること。また、定数やNOT回路、unusedの設定もすることができ大変便利だからです。

smartgenは、最後に生成ボタンを押すことで自動的に対応するVHDLコードを生成してくれますので、移植性も損ないません。

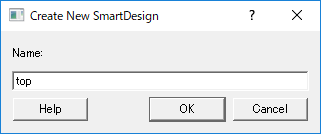

適当に名前をつけます。ここでは「top」とします。

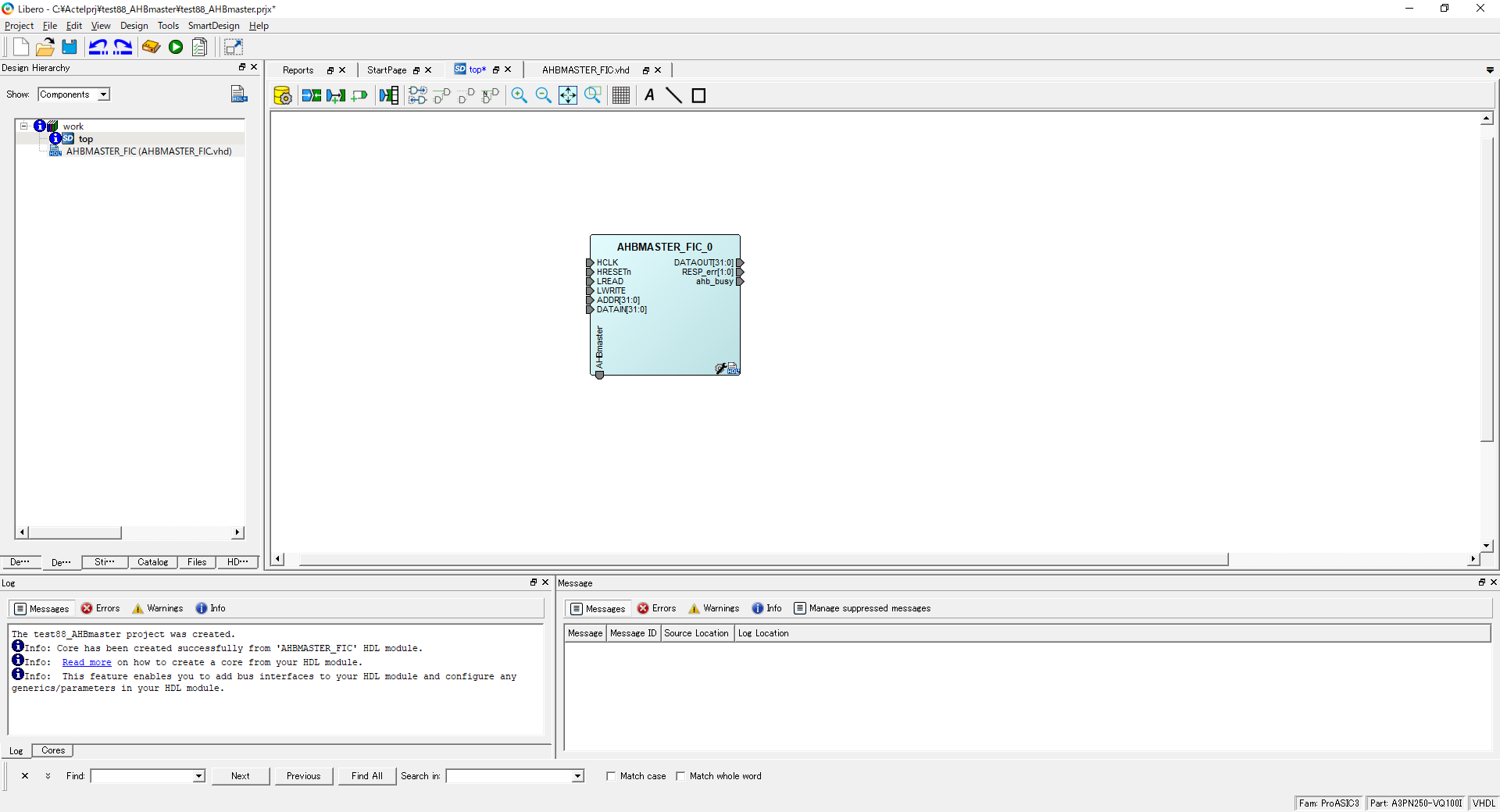

次に「Design Hierachy」上で、ダウンロードした「AHBMASTER_FIC.vhd」をインポートします。

インポートすると、以下のように表示されます。smartgenで作成したtopとAHBMASTER_FIC.vhdが見えています。

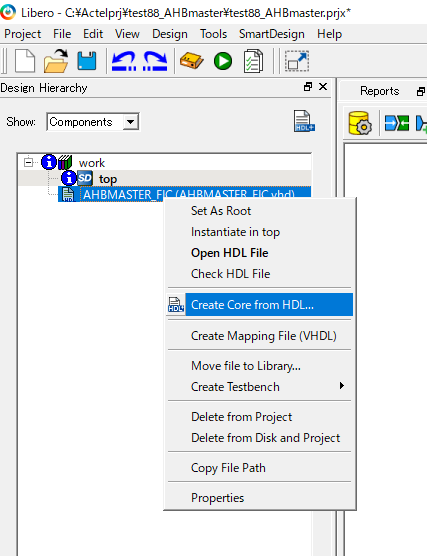

AHBMASTER_FIC.vhdはAMBAのポートを有するので、AMBAポートとして設定します。

これを設定しないと、smartgen上でmicrosemi製のIPコアと接続出来ません。

AHBMASTER_FIC上で右クリックし、「Create Core from HDL...」を選択してください

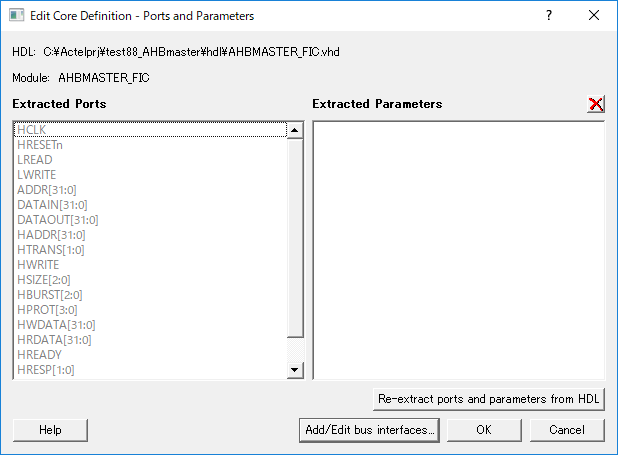

下のような画面が表示されます。

中央下の「Add/Edit bus interfaces...」ボタンを押します。

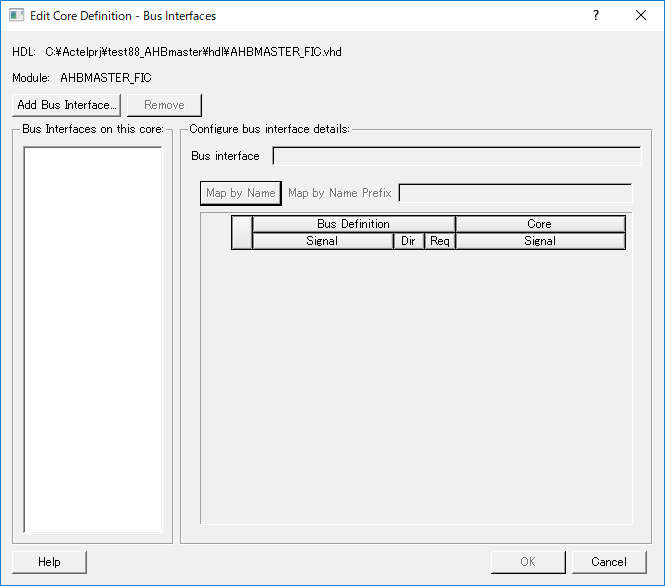

すると、以下のような画面が表示されます。

左上の「Add Bus Interface...」ボタンを押します。

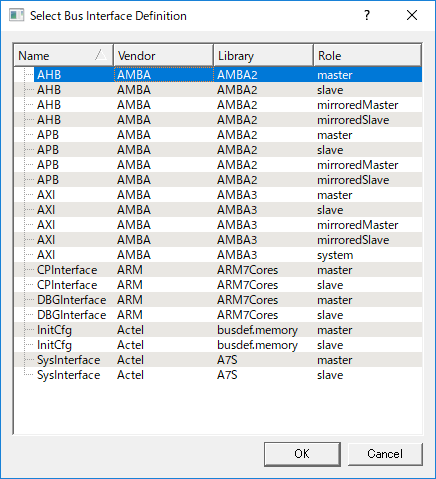

下のような画面が表示されますので、一番上の「AHB AMBA AMBA2 master」を選択し、OKを押します。

自動的にポートがセッティングされます。

「Bus interface(AHB)」と「Map by Name Prefix」を適当に設定します。

初期値のままでも問題ありませんが、慣習的(?)に以下のような名前にしておくことをお薦めします。

最後にOKボタンを押します。

ポートの設定が完了しましたので、「Design Hierachy」からAHBMASTER_FICを右側にドラック&ドロップします。

そうすると、以下のような画面となります。

あとは、ユーザーの好きなように「Catalog」からmicrosemiのIPコアを同じようにドラック&ドロップしてつなぎ合わせて行きます。