Asynchronous SPI master

Project maintainers

Details

Created: Jan 18, 2017

Updated: Jun 20, 2017

SVN Updated: Jan 23, 2017

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:Verilog

Development status:Alpha

Additional info:Design done

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

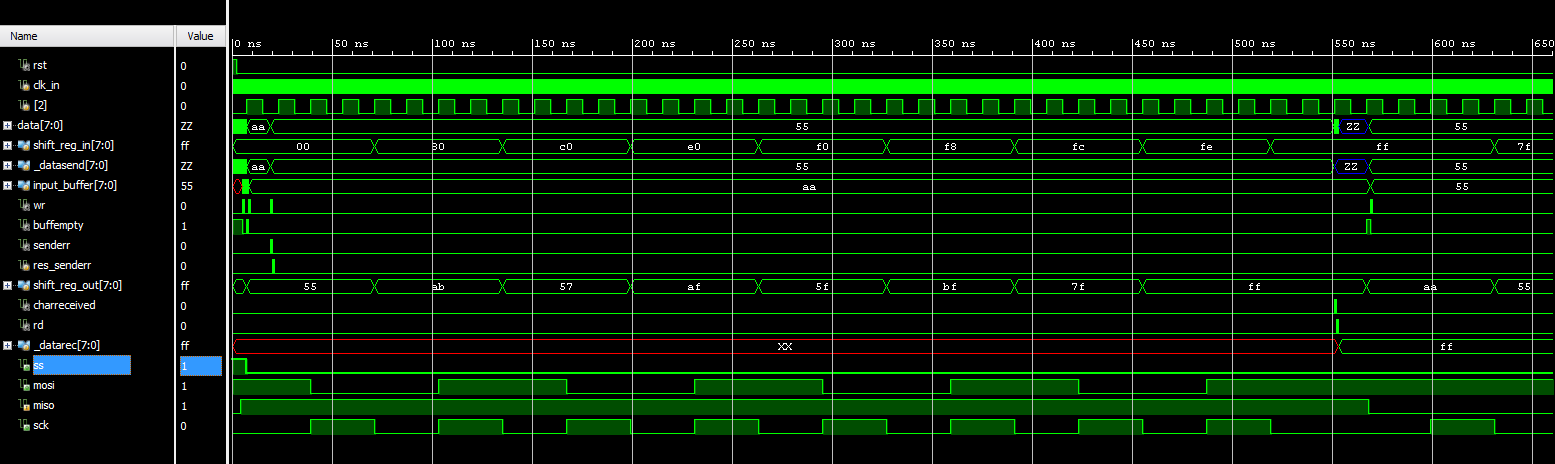

This is a Verilog language asynchronous SPI, this mean that the controller can have a different clock frequency than SPI module. On the simulate file I put the SPI clock = system clk/8 to show the propagation of signals a different clock rate. The signals to control the interface are:

clk,/* Peripheral clock/not necessary to be core clock, the core clock can be different (input) */

rst,/* Asynchronus reset, is mandatory to provide this signal, active on posedge (input) */

data,/* In/Out data(bidirectional) */

wr,/* Send data, asynchronus with 'clk' , active on posedge or negedge selected by defining 'WRITE_ON_NEG_EDGE'(input) */

rd,/* Read data, , asynchronus with 'clk' , active on posedge or negedge selected by defining 'READ_ON_NEG_EDGE'(input) */

buffempty,/* '1' if transmit buffer is empty (output) */

prescaller,/* The prescaller divider is = (1 << prescaller) value between 0 and 7 for dividers by:1,2,4,8,16,32,64,128 and 256 (input)*/

sck,/* SPI 'sck' signal (output) */

mosi,/* SPI 'mosi' signal (output) */

miso,/* SPI 'miso' signal (input) */

ss,/* SPI 'ss' signal (if send buffer is maintained full the ss signal will not go high between between transmit chars)(output) */

lsbfirst,/* If '0' msb is send first, if '1' lsb is send first (input) */

mode,/* All four modes is supported (input) */

senderr,/* If you try to send a character if send buffer is full this bit is set to '1', this can be ignored and if is '1' does not affect the interface (output) */

res_senderr,/* To reset 'senderr' signal write '1' wait minimum half core clock and and after '0' to this bit, is asynchronous with 'clk' (input)*/

charreceived/* Is set to '1' if a character is received, if you read the receive buffe this bit will go '0', if you ignore it and continue to send data this bit will remain '1' until you read the read register (output) */

The signal for buffer empty is different from the signal that indicate the receive of a new character, this let user to implement the send section separate from the receive section of a program.

The below image is truncated on right edge to see it entirely click right and press view image.