DDR2 SDRAM Controller

Project maintainers

Details

Created: Aug 20, 2011

Updated: Jun 3, 2012

SVN Updated: Jun 3, 2012

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:VHDL

Development status:Stable

Additional info:

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

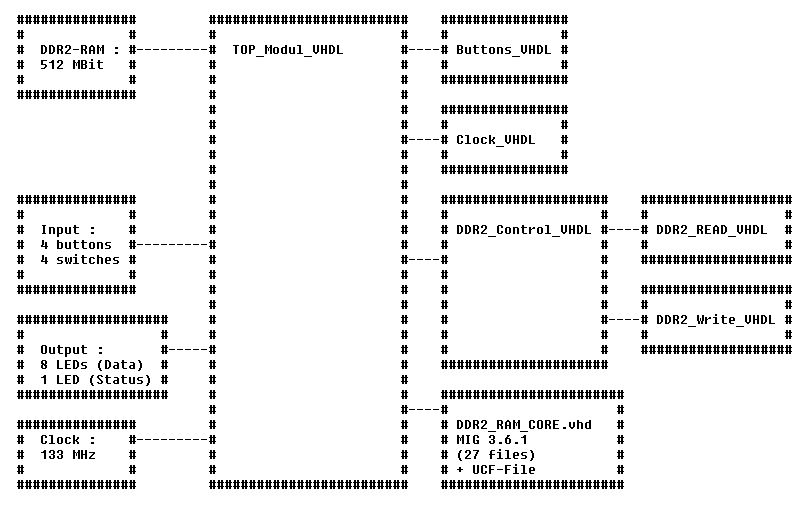

This project implements a DDR2-SDRAM Controller on a Xilinx Spartan-3A Board

Moduls

Function

After a Power on :

==================

1. Init-Sequenz for the RAM

2. Automaic Write-Sequenz (writes 16 Datawords each 64Bit to the RAM)

3. Automatic Read-Sequenz (reads the first Dataword from the RAM)

4. Display the Dataword at the 8Bit LEDs

Switch-0 :

==========

> SW0 is used as a Reset-Switch

Switch-1 to 3 :

===============

> SW1 to SW3 selects witch part of the Dataword

is shown at the LEDs

Button north :

==============

> increments the Adresspointer

Button south :

==============

> decrements the Adresspointer

Button east :

=============

> reads a single Dataword (64Bit) from the actual adress

Button west :

=============

> writes a fixed Dataword (64Bit) to the actual adress

Status LED :

============

> LED is permanent blinking

Project Options

Plattform : XILINX Spartan-3A

FPGA : XC3S700A-FGG484

Language : VHDL

ISE : ISE-Design-Suite V:13.1

IP-Core : MIG V:3.6.1

DDR2-SDRAM : MT47H32M16 (64 MByte)

Limitation

Burst Length = 4

Data Width = 16 Bit

> with these settings each Data access reads (and writes)

a 64Bit Dataword (4 x 16 Bit)

Read/Write speed

Read :

======

> to Read one Dataword (64Bit)

22 Clockzycles are needed

Write :

=======

> to Write one Dataword (64Bit)

25 Clockcycles are needed

Status

20.08.2011 : Version 7.0 : Project start