A Linked List Run-Length-Based Single-Pass Connected Component Analysis

Project maintainers

Details

Created: Apr 21, 2016

Updated: May 7, 2025

SVN Updated: Apr 26, 2016

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 2 reported / 1 solved

Other project properties

Language:Verilog

Development status:Stable

Additional info:Design done, FPGA proven

WishBone compliant: No

WishBone version: n/a

License: LGPL

Repo Migration

LinkRunCCA has been migrated to GitHub for further development (as of May 2025).

Special thanks to Topi for contributing to LinkRunCCA.

Description

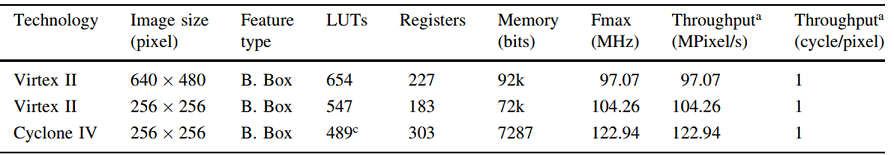

LinkRunCCA is a real-time single-pass connected component analysis/ connected component labeling (CCA/CCL) implemented in Verilog HDL. It can be easily connected to any image pixel streaming interface in FPGA design, producing bounding boxes of ALL (no number of box limitation) connected components as soon as completed box is detected. It can operate in maximum streaming throughput (one pixel per cycle) and has very low memory requirement. This implementation is based on the state-of-the-art algorithm from publication in http://dx.doi.org/10.1007/s11554-016-0590-2

Features

LinkRunCCA uses combination of linked list and run-length-based techniques to label and extract components' feature (bounding box in this case) in one scan. This hardware module accepts binary image/video stream as input and produces bounding boxes of each connected component in the image/video. Bounding box of each connected component is produced immediately as soon as the component is completed. The size of image/video is parametrizable, hence the memory requirement is varied based on image/video size.

Download command (linux):

svn co http://opencores.org/ocsvn/linkruncca/linkruncca/trunk

Port and Parameter Descriptions:

Input Ports:

clk - clock sink

rst - reset sink

pix_in - input binary image/video stream (1 bit)

datavalid - valid bit for input stream

Output Ports:

box_out - bounding box of each component

datavalid_out - valid bit for each bounding box

Parameters:

imwidth - image width

imheight - image height

Performances:

Algorithm detail is described in the following paper:

*Please kindly cite this paper in any published work if you use this implementation

Tang, J. W., et al. "A linked list run-length-based single-pass connected component analysis for real-time embedded hardware." Journal of Real-Time Image Processing: 1-19. 2016. doi:10.1007/s11554-016-0590-2.

Author email:

jaytang1987@hotmail.com

Simulation

Simulation using Verilator tool is included due to its faster simulation for image processing. Several binary test images are available for testing. The bounding box image is created after the simulation.

A simulation script is provided. Prior to simulation, the script detects the simulating image size and generates appropriate headers/parameters for both simulation and verilog hardware.