miniMIPS Superscalar

Project maintainers

Details

Created: Dec 21, 2018

Updated: Jul 13, 2020

SVN Updated: Jul 6, 2020

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:VHDL

Development status:Alpha

Additional info:

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

The miniMIPS Superscalar processor project started in March 2017 for a college project that explores levels of parallelism in various granularities. The objective was to insert parallelism in the level of instructions. Computer Engineering - UERGS - Brazil

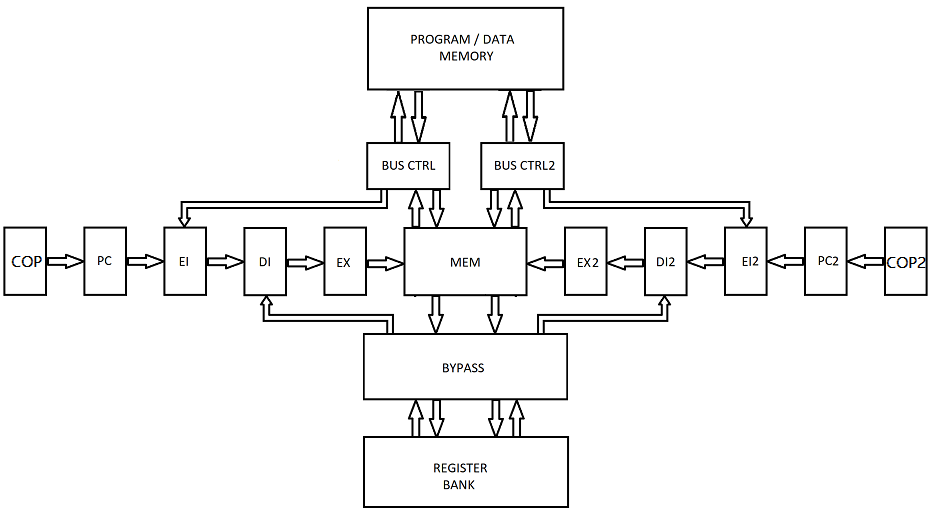

The Superscalar miniMIPS processor is a 32-bit processor that has 2 pipelines. This processor was fully based on the "miniMIPS" processor that was created in 2004 and is hosted here at OPENCORES. The miniMIPS had its data path duplicated and can execute two instructions per clock cycle.

It is compatible with the miniMIPS ISA that implements the MIPS I microarchitecture. A new multiplication instruction has been created for operations with 16-bit operands and the result is saved directly to the general purpose register bank as the other logical and arithmetic instructions.

The GASM assembly that was created by the miniMIPS authors can be used to create programs. Was made available a modified version of GASM that assembles a multiplication instruction which operands are 16-bit wide.

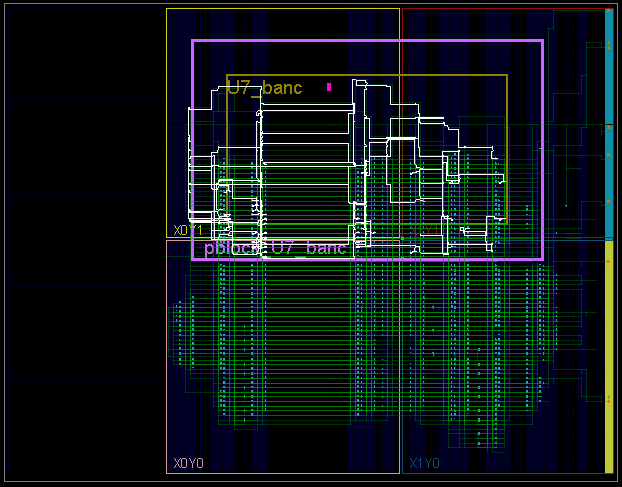

Update: FPGA proven on CORA Z7 board, it was hard to hit the best run to fix instabilities because of the compromised QoR (congested routes, auto placement, ...) on this amazing device.

device XC7Z007S-1CLG400C @ 50MHz and BRAM as system memory. Ran matrix multiplication + checksum, fir filter, fft.