Natalius 8 bit RISC

Project maintainers

Details

Created: Jun 1, 2012

Updated: Jun 8, 2012

SVN Updated: Jun 5, 2012

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:Verilog

Development status:Beta

Additional info:FPGA proven

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

Natalius is a compact, capable and fully embedded 8 bit RISC processor core described 100% in Verilog. It occupies about 268 Slices, 124 FFs, 503 LUTs (4 input) in Xilinx Spartan3E1600 (around 1.67% slices). Natalius offers an assembler that can run on any python console.

The instruction memory is implemented in two Xilinx BlockRAM Memories, it stores 2048 instructions, each instruction has a width of 16 bits (2048x16). Each instruction takes 3 clock cycles to be executed.

Documentation

Click here to read the documentation: Doc

Features

1. 8 Bit ALU

2. 8x8 Register File

3. 2048x16 Instruction Memory

4. 32x8 Ram Memory

5. 16x11 Stack Memory

6. Three CLK/Instruction

7. Carry and Zero flags

8. No operation Instruction (nop)

9. 8 bit Address Port (until 256 Peripherals)

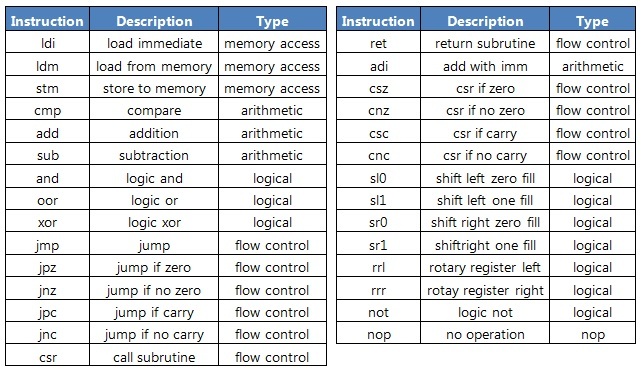

10. LDI, LDM, STM (Memory Access Instructions)

11. CMP, ADD, ADI, SUB (Arithmetic Instructions)

12. AND, OOR, XOR, NOP, SL0, SL1, SR0, SR1, RRL, RRR (Logical Instructions)

13. JMP, JPZ, JNZ, JPC, JNC, CSR, RET, CSZ, CNZ, CSC, CNC (Flow Control Instructions)