PLB-to-WB Bridge

Project maintainers

Details

Created: Aug 13, 2010

Updated: Feb 23, 2014

SVN Updated: Aug 14, 2010

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:VHDL

Development status:Alpha

Additional info:FPGA proven

WishBone compliant: Yes

WishBone version: n/a

License: LGPL

Description

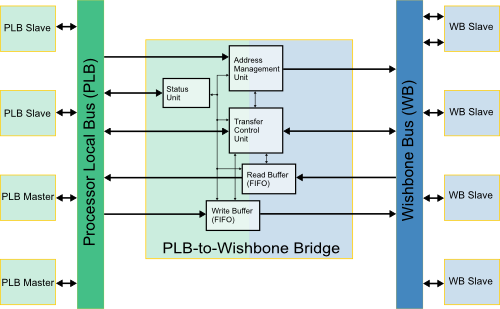

The intention of the project is the development of a bus bridge, which enables the usage of WB compliant IP cores in a system, which uses the Processor Local Bus (PLB) as system and peripheral bus. The PLB-to-WB (PLB2WB) Bridge enables the access to slaves on the WB side for masters on the PLB side.

Features:

- separate clock domains for PLB and WB

- separate resets for PLB and WB possible

- PLB address pipelining (optional)

- PLB fixed length burst transfers (only words, optional)

- PLB line transfers (optional)

- WB B.3 classic cycles (block and single, block cyckes are optional)

- flexible address offset

- handling of delayed write errors on WB side

- transfers interrupts to PLB side

File and Folder Structure

You can checkout all files with the following command:

svn co http://opencores.org/ocsvn/plb2wbbridge/plb2wbbridge/trunk/

Because this bridge was intended to be used with Xilinx Platform Studio (XPS), the file and folder structure is a little bit different to other OpenCores projects. But if you are going to use XPS, just add

systems/EDK_Libs

to your module search path.If you are not going to use XPS, you can find all VHDL source files in

systems/EDK_Libs/WishboneIPLib/pcores/plb2wb_bridge_v1_00_a/hdl/vhdl/

Some simulation systems for testing the functionality are located in

systems/test_system_sim/

andsystems/dev_system_sim/

contains a simulation system to implement new features.If you are using a Xilinx toolchain with Xilinx FPGAs, the folder

coregen/fifo_generator/

contains a Ruby script and a configuration file to auto-generate all necessary FIFOs (see documentation for more information).Last but not least, you will find the documentation in

doc/

Development Status

PLEASE NOTE: THIS PROJECT HAS NOT BEEN UPDATED SINCE 2010. THE PLB BUS IS NOT USED ANYMORE IN CURRENT XILINX SOCS AND THERE IS NO MORE NEED FOR THIS PROJECT.

This project was started as a student work at HS-Pforzheim University (Germany).

The project was finished in the middle of august 2010.

The PLB-to-WB Bridge is implemented and all functionality is tested via RTL simulation.

In addition, basic functionality is tested in a SoC for a Virtex-5 FPGA.

Because there is never an end, the following list shows some open issues

- Implementation of WB B.4 interface

- Implementation of WB registered feedback bus cycles