Versatile counter

Project maintainers

Details

Name: versatile_counter

Created: Mar 27, 2009

Updated: Jul 14, 2010

SVN Updated: Jan 27, 2011

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 1 reported / 0 solved

Created: Mar 27, 2009

Updated: Jul 14, 2010

SVN Updated: Jan 27, 2011

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 1 reported / 0 solved

Star2you like it: star it!

Other project properties

Category:Arithmetic core

Language:Verilog

Development status:Mature

Additional info:Design done, FPGA proven, Specification done

WishBone compliant: No

WishBone version: n/a

License: LGPL

Language:Verilog

Development status:Mature

Additional info:Design done, FPGA proven, Specification done

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

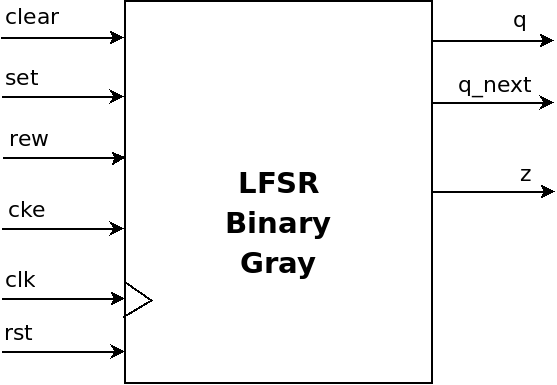

A versatile counter that can be defined as a binary, gray or LFSR counter. Usage include baudrate generator, address generator for FIFO and much more.

As a user you edit a define file to make the counter fit your project demands. You the generate a tailored counter. The performance and area can hereby be optimezed for the given application

Pros and cons with different types of counter

- LFSR

- extremely low area usage

- high performance

- one cycle shorter count cycle compared to binary versions

- typically used for interval timer and as adress generator for FIFO

- Binary

- The standard type, usefule for various types of implementation

- Gray

- The Gray type counter toggles only one bit per update

- Implemented as a normal binary counter with an extra output stage converting the state to Gray encoding

- Typical usage is adress generator for asynchroinous FIFOs

This module is written in Verilog and uses pre processor commands.

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.