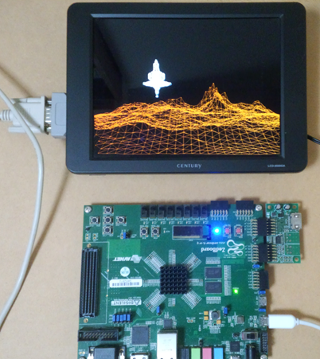

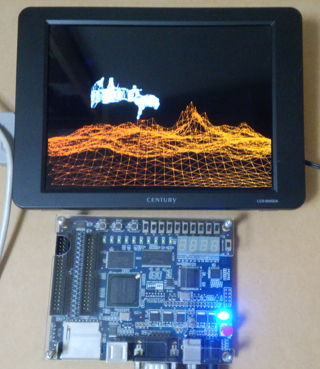

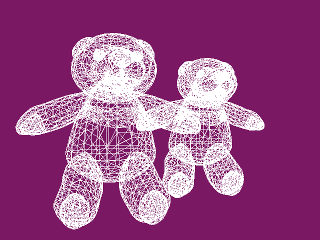

Wire-Frame 3D Graphics Accelerator IP Core

Project maintainers

Details

Created: Sep 30, 2015

Updated: Dec 30, 2025

SVN Updated: Dec 30, 2025

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:Verilog

Development status:Stable

Additional info:Design done, FPGA proven

WishBone compliant: Yes

WishBone version: n/a

License: BSD

Description

WF3D is a real-time 3D graphics rendering IP Core.

The IP Core reads 3D triangle vertices from memory, then transforms them into 2D space,

and writes 2D triangle’s edge line to memory. Note that this IP Core only supports Wire-Frame 3D graphics.

In other words, the IP Core does not have traditional 3D graphics rendering features,

such as polygon filling, texture mapping, lighting, etc.

Instead of lacking these features, this IP Core has several advantages,

such as small logic consumption and low-bandwidth memory access.

Features

- Hardware Geometry Engine and Rasterizer

- Model-View-Projection matrix transformation

- Clipping

- Back-face culling

- Viewport mapping

- Wire-Frame rasterization with 8 bit color

- DMAC for reading 3D object vertices

- Screen size: up to 2014 x 1536(QXGA)

- Small logic consumption

- Low bandwidth requirement

WF3D does NOT support:

- Memory clear DMAC

- Filled triangle rasterization

- Texture mapping

- Lighting

Additional resources

- Sample FPGA system implementation(ZedBoard/DE0), with original VGA controller

- Demo applications

- C API for controlling 3D scene

- 3D model convert script

News

2016/10/30 Tested on Vivado 2016.x. 2016/09/19 ZedBoard sample implementation is added. 2016/08/16 new demo is added. fm_geo_tri.v bufgix. (bit reduction was missed for outcode evaluation.)

2025/12/30 Resolve compilation errors in vpi.c for Icarus Verilog 12.0 (macOS Tahoe 26.2).

Screen Shot