Oscilloscope for Xilinx Spartan-3E at 160MSPS

Project maintainers

Details

Created: Oct 4, 2018

Updated: Feb 12, 2019

SVN Updated: Feb 12, 2019

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:VHDL

Development status:Alpha

Additional info:

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

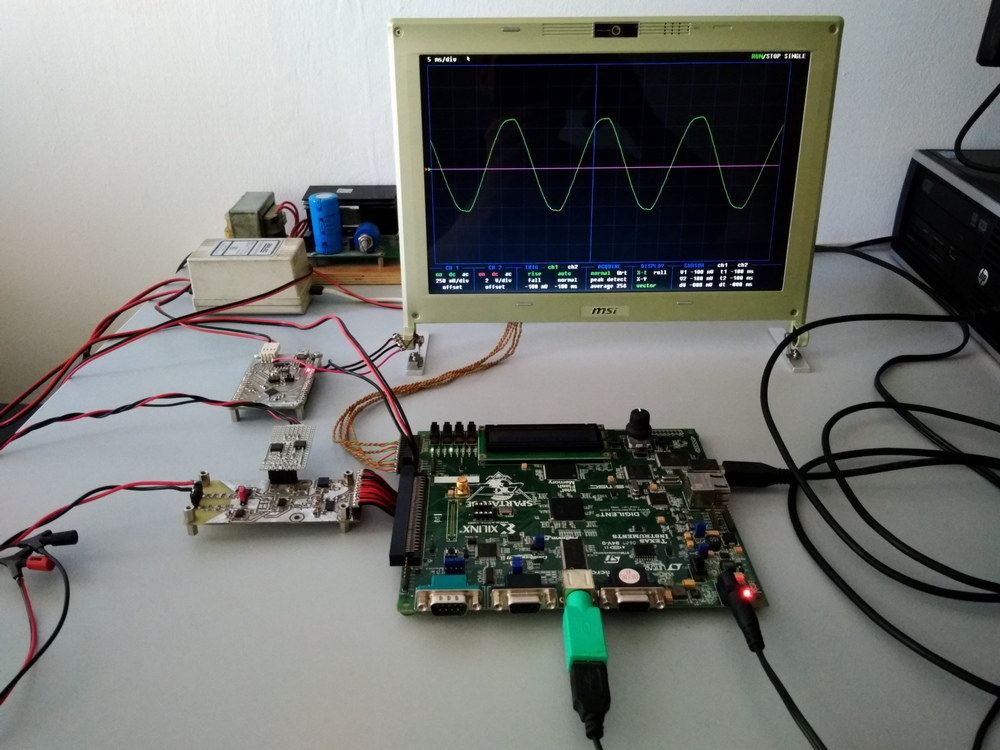

This is an experimental oscilloscope VHDL design working on the Xilinx Spartan-3E starter board.

The analog signal is sampled with a TI ADC08200 converter currently at 160MSPS (max. feasible fs in this setup is TBD).

The output is displayed on a 12" Samsung LCD (LTN121W1-L03) of an old laptop with 1280x800 pixels, the interface is FPD-link (3+1 channels LVDS) operating at 280MHz (=7*pixel_frequency).

The user interface controller is a PS2 mouse: positioning, buttons and scroll wheel.

Both the FPGA and the LCD are more than 10 years old, but the design could be ported to a newer platform operating at higher frequency.

The design is not complete or bug-free, but can be used for various measurements.

Current features and limitations:

- 2 channels (only 1 channel was tested until now)

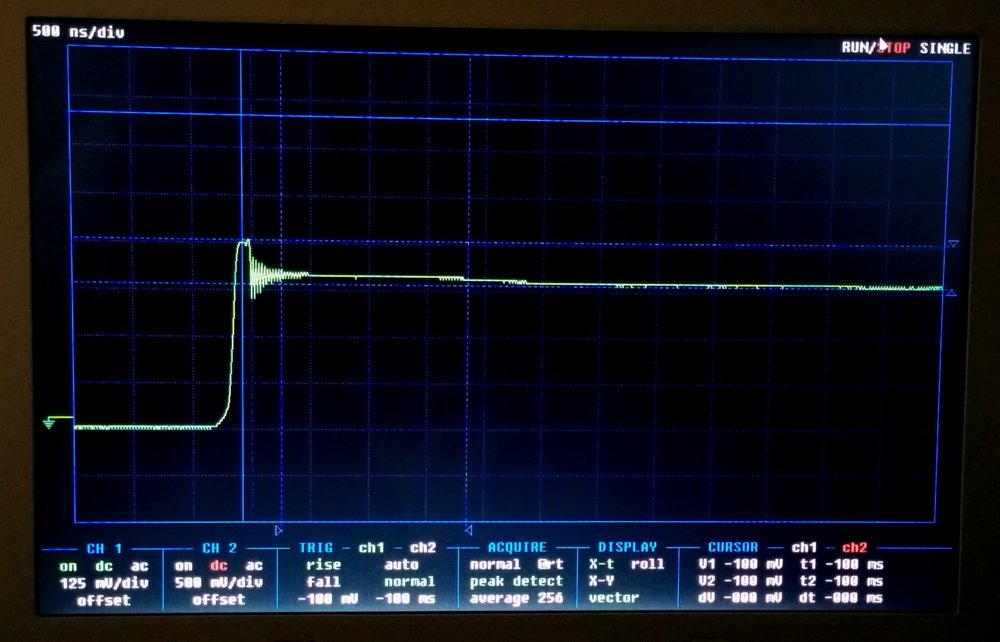

- Time base from 500ns/div, that is 1 pixel/sample at 160MSPS and 80pixels/div (interpolation is not applied)

- RUN/STOP modes (Single measurement is to be implemented)

- Trigger modes: rising or falling edge; auto or normal; trigger level and delay positioning in the waveform window with the mouse

- Acquisition modes: normal or peak detect. (averaging is to be implemented)

- Display modes: X-t, roll. (X-Y is to be implemented)

- The vertical resolution and the trigger and cursor positions are not to scale - requires binary to decimal string conversion.

Photos

Overview:

The small board on the left is a differential probe. It contains the AD converter (ADC08200), an instrumentation amplifier made of 3 high-speed opamps (AD8057) and their power supplies (3.3V for the ADC and +/-5V for the amplifiers).

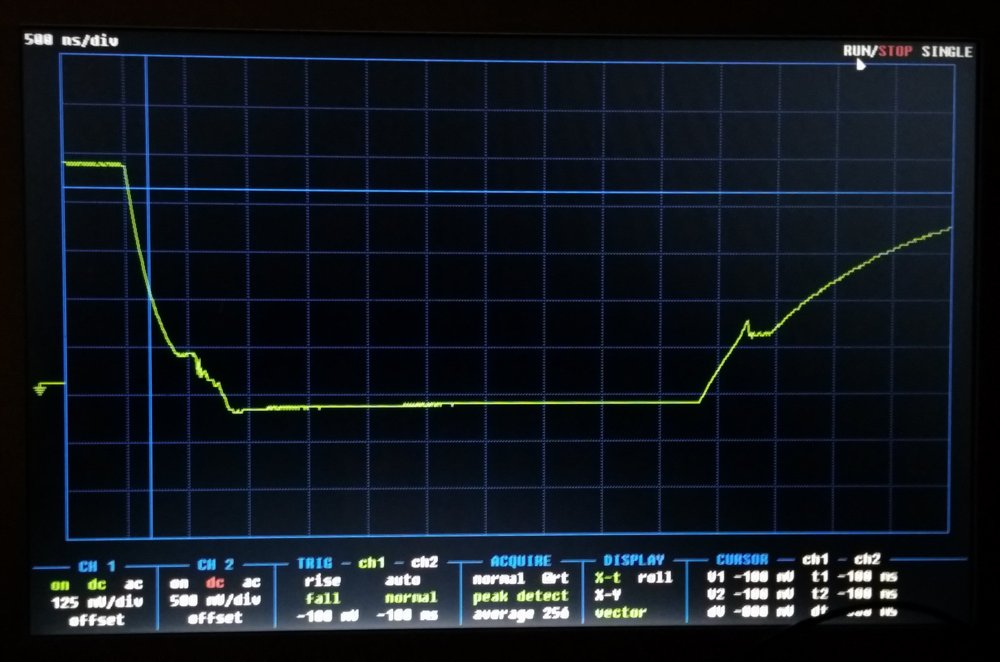

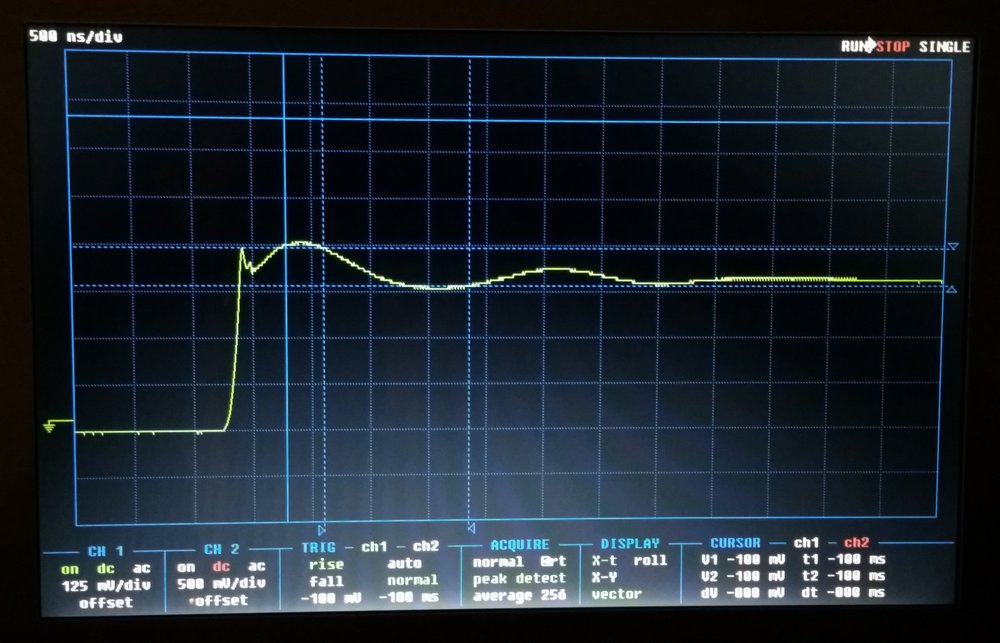

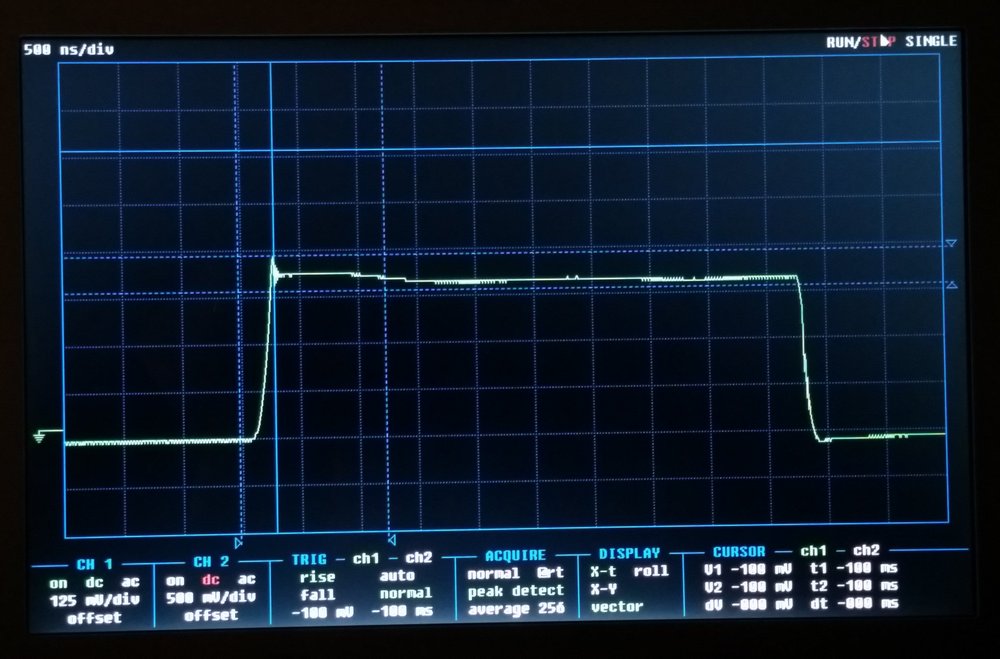

Measuring Vgs and Vds of power MOSFETs in BLDC motor drives: