Uart2BusTestBench

Project maintainers

Details

Name: uart2bus_testbench

Created: Jan 24, 2016

Updated: Jun 22, 2017

SVN Updated: Jul 22, 2017

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 1 reported / 1 solved

Created: Jan 24, 2016

Updated: Jun 22, 2017

SVN Updated: Jul 22, 2017

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 1 reported / 1 solved

Star4you like it: star it!

Other project properties

Category:Testing / Verification

Language:Other

Development status:Stable

Additional info:ASIC proven, Design done, FPGA proven, Specification done

WishBone compliant: No

WishBone version: n/a

License: LGPL

Language:Other

Development status:Stable

Additional info:ASIC proven, Design done, FPGA proven, Specification done

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

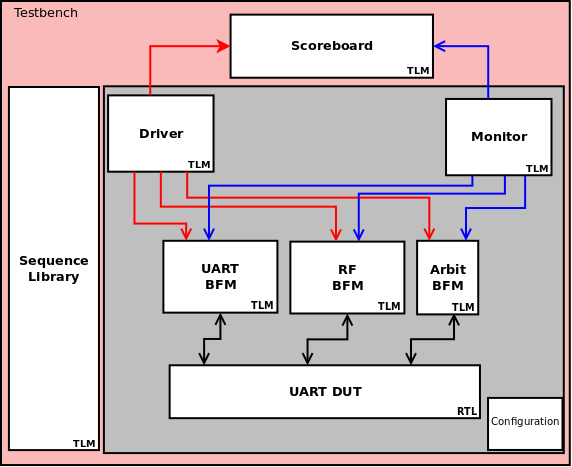

Uart2BusTestBench is implemented using Universal Verification Methodology to perform the functional verification to the RTL design released by Moti Litochevski and Steve MULLER (check this link ).

The Main Features :

- Additional C++ program is attached to facilitate baud frequency calculations.

- Includes UART BFM which in turn act as UART driver and includes all standard routines which makes it possible to bury it into another Testbench (Like UART VIP).

- Includes Register-File BFM which act as slave memory and includes all non-standard routines

- Support inserting idle time between transactions.

General Test-bench Architecture

You can download The Architecture Specifications from here

Environment Configurations

| Field | Description | Possible Choices |

| Active Edge | The active clock edge at which, the data is changed on the UART buses |

|

| First Bit | Represent the sequence through which the byte is serialized |

|

| Data Mode | The data representation through the text commands |

|

| Number of stop bits | The number of stop bits sent after the latest bit of each byte |

|

| Number of bits | The number of bits through each field transfer |

|

| Parity Mode | The used parity type through each byte |

|

| Response Time | Represent the maximum allowable time through which dut should respond to the driven request. |

No Limitations |

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.