Core1990: Interlaken protocol

Project maintainers

Partner team

Details

Created: Mar 19, 2018

Updated: Jan 23, 2020

SVN Updated: Jan 23, 2020

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:VHDL

Development status:Alpha

Additional info:FPGA proven

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

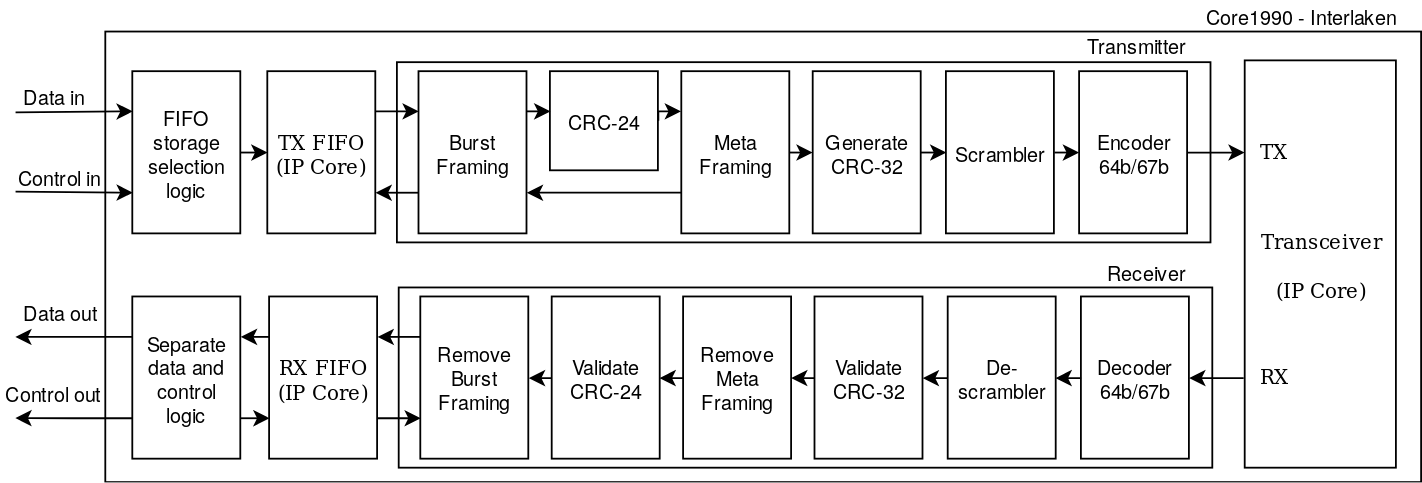

Core1990 is a point-to-point communication protocol using the royalty-free Interlaken protocol as its foundation.

It is designed by engineers and students of the Electronics Department of Nikhef (Amsterdam, The Netherlands) with large experiments at CERN (e.g. ATLAS) in mind.

The development of Core1990 was intended to explore and publish an open source protocol providing high throughput with a small percentage of overhead.

Certain features like flow control and error detection will be included.

The Interlaken protocol

Core1990 is developed according to the Interlaken Protocol Definition revision 1.2 which was published on October 7, 2008.

Here are some pointers to the official Interlaken alliance:

Official website

Protocol Definition v1.2

Copyright © 2006 Cortina Systems, Inc. and Cisco Systems, Inc.

Status

This is the current status of the project:

* Data is packed into bursts and metaframes and is unpacked by the receiver

* CRC-24/32 are generated and checked

* Data is encoded/decoded (including scrambling)

* Hardware implementation targets Xilinx devices (Tested on VC707 and VC709 boards)

* Verified with an official Xilinx Interlaken IP-Core

Last update January 2020

To Do

* Hardware implementation for Altera (Intel PSG) devices

* Support other FPGA platforms

* Implement channel bonding