DDS Synthesizer

Project maintainers

Details

Created: Dec 22, 2008

Updated: Feb 23, 2016

SVN Updated: Apr 5, 2013

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:VHDL

Development status:Stable

Additional info:Design done, FPGA proven

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

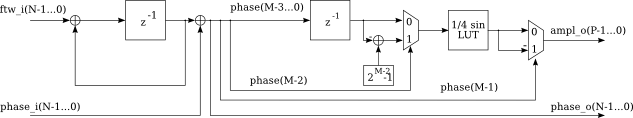

The DDS IP core (dds_synthesizer) is a implementation of a direct digital frequency synthesizer (DDS) (also called number controlled oscillator, NCO) which produces a sinewave at the output with a specified frequency and phase (adjustable at runtime). Only one quater of the sinewave is stored in the LUT, the rest is computed by simple operations (negating, subtraction), resulting in a reduced memory requirement. The resolution of the frequency tuning word (FTW), the phase and the amplitude defined seperately. Several precomputed look-up tables are provided as combinations from 8 to 16 bit phase and amplitude resolution. The frequency resolution can is defined as generic. A matlab script for generating the LUTs for different resolutions is included. The design is fully pipelined for maximum throughput.

If you find something interesting, feel free to contact me: pluto[at]ls68.de