Hardware Assisted IEEE 1588 IP Core

Project maintainers

Details

Created: Mar 6, 2012

Updated: Apr 11, 2018

SVN Updated: Jun 3, 2014

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 5 reported / 3 solved

Other project properties

Language:Verilog

Development status:Beta

Additional info:Design done, Specification done

WishBone compliant: Yes

WishBone version: n/a

License: LGPL

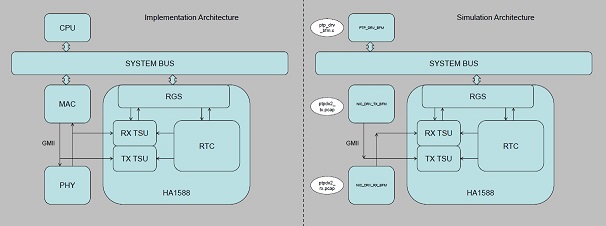

Architecture

Description

Hardware Assisted IEEE 1588 IP Core. The necessary FPGA logic to assist SW protocol stack in implementing the Precision Time Protocol (IEEE 1588-2008) on 1000M/100M/10M Ethernet networks. PTP packets transmitting and receiving should be implemented by PTP SW protocol stack (PTPd) with existing MAC function; This IP Core implements the Real-Time Clock (RTC) and Time Stamping (TSU) of PTP event packets.

Feature Description

RTC: Real Time Clock.

* Standard PTP clock output with 2^48s and 2^32ns time format.

* 1PPS output for clock accuracy measurement.

* Tunable accumulator based clock with 2^-8ns time resolution and 2^-32ns period resolution.

** Direct time write, with 2^-8ns resolution.

** Direct frequency write, with 2^-32ns resolution.

** Timed temporary time adjustment, with 2^-8ns resolution and 32bit timer.

* Variable input clock frequency.

* Clock Domain Crossing hand-shaking, for SW read and write access.

TSU: Time Stamping Unit.

* Two-Step PTP operation.

* GMII/MII interface monitor with line-speed PTP packet parsing.

* Variety of PTP packet formats supported.

** Layer2 IEEE 802.3 PTP packet, with stacked VLAN tags.

** Layer4 IPv4/UDP and IPv6/UDP PTP packet, with stacked VLAN tags and/or stacked MPLS labels.

* Configurable 8bit one-hot mask to selectively timestamp PTP event packet based on message type value.

** mask bit 0: Sync

** mask bit 1: Delay_Req

** mask bit 2: Pdelay_Req

** mask bit 3: Pdelay_Resp

** mask bit 4 to 7: Reserved for future PTP event message types

* 32bit packet parser datapath for easier timing closure.

* 15-entry timestamp queue.

* 128bit timestamp format.

** 16bit extra information.

** 80bit timestamp.

** 32bit packet identity data.

SystemVerilog DPI based simulation environment is included for SW driver development and co-simulation.

(sim/top/ptp_drv_bfm/ptp_drv_bfm.c) (sim/top/ptp_drv_bfm/ptp_drv_bfm.v)

PCAP file based stimulus input is included for verification with real-world traffic.

(sim/top/nic_drv_bfm/ptpdv2_tx.pcap) (sim/top/nic_drv_bfm/ptpdv2_rx.pcap)

The IP Core can be used as an IP Component in Altera Qsys, Xilinx XPS or WishBone.

(rtl/bus/qsys) (rtl/bus/xps/pcores) (rtl/bus/wishbone)

The only FPGA vendor dependent module is the timestamp queue. Both Altera and Xilinx's DCFIFOs are provided in the PAR folder.

(par/altera/ip/dcfifo_128b_16.v) (par/xilinx/ip/dcfifo_128b_16.v)

Bonus Tool

A tool to analyze the transaction timing of captured PTPv2 packets. The tool is written and run in Scilab. The captured PTPv2 packets are results of running PTPdv2 between two PCs.

(doc/tool/ptpv2_timing_analyzer/ptpv2_timing_analyzer.sce)

TODO

It is complained that there is a lack of documentation for the HA1588 project. This will be fulfilled for the next release. Here are two requests for those who requested:

1. Read the RTC and TSU memory map under the /doc folder, with the detailed operation procedure in the /sim/top/ptp_drv_bfm/ptp_drv_bfm.c

2. Give feedback of what should be included in the documentation as bug-fix requests