openHMC

Project maintainers

Details

Created: Sep 30, 2014

Updated: May 12, 2015

SVN Updated: Aug 10, 2016

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:Verilog

Development status:Stable

Additional info:Design done, FPGA proven, Specification done

WishBone compliant: No

WishBone version: n/a

License: LGPL

Description

openHMC is an open-source project developed by the Computer Architecture Group (CAG) at the University of Heidelberg in Germany. It is a vendor-agnostic, AXI-4 compliant Hybrid Memory Cube (HMC) controller that can be parameterized to different data-widths, external lane-width requirements, and clock speeds depending on speed and area requirements.

The main objective of developing the HMC controller is to lower the barrier for others to experiment with the HMC, without the risks of using commercial solutions.

For more information check the official openHMC documentation, available here on opencores.org or on the official project website openHMC Home

The openHMC controller

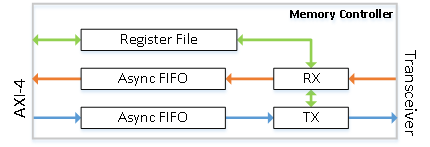

The openHMC controller is presented as a high-level block diagram in the figure below. The asynchronous input and output FIFOs allow the user to access the memory controller from a different clock domain. On the transceiver side, a registered output holds the data reordered on a lane-by-lane basis; allowing seamless integration with any transceiver types. A register-file provides access to control and monitor the operation of the memory controller.

***** Features *****

The openHMC controller implements the following features as described in the HMC specification Rev 2.0:

- Full link-training, sleep mode, and link retraining

- 16Byte up to 128Byte read and write (posted and non-posted) transactions

- Posted and non-posted bit-write and atomic requests

- Mode Read and Write

- Full packet flow control

- Packet integrity checks (sequence number, packet length, CRC)

- Full link retry