SBA - Simple Bus Architecture

Project maintainers

Details

Created: Sep 4, 2012

Updated: Nov 23, 2018

SVN: Check description below for external links

Bugs: 1 reported / 0 solved

Other project properties

Language:VHDL

Development status:Stable

Additional info:FPGA proven

WishBone compliant: No

WishBone version: n/a

License: LGPL

Library Repository

You can download the official library repository from: https://github.com/mriscocSBA-Library

Description

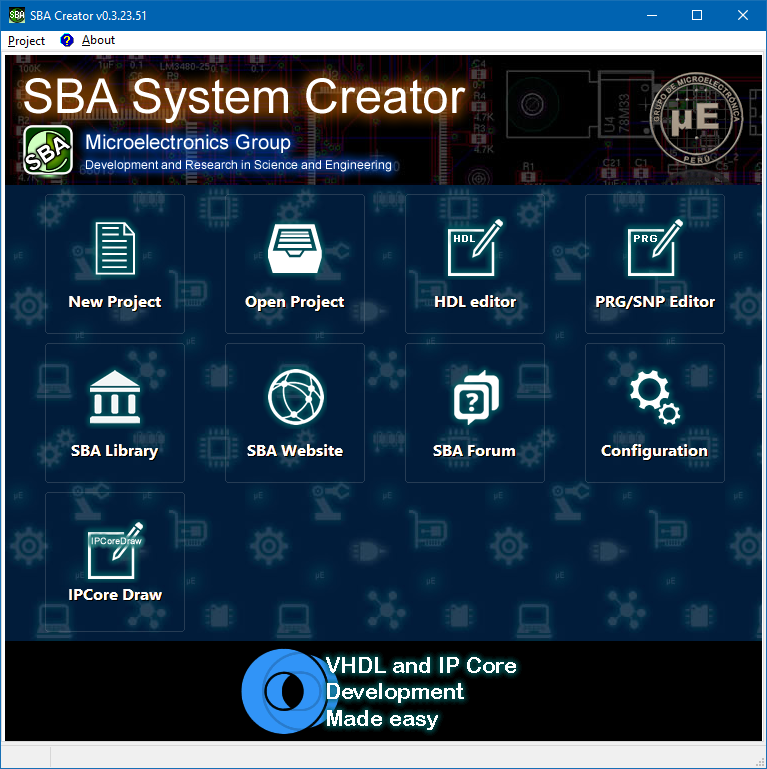

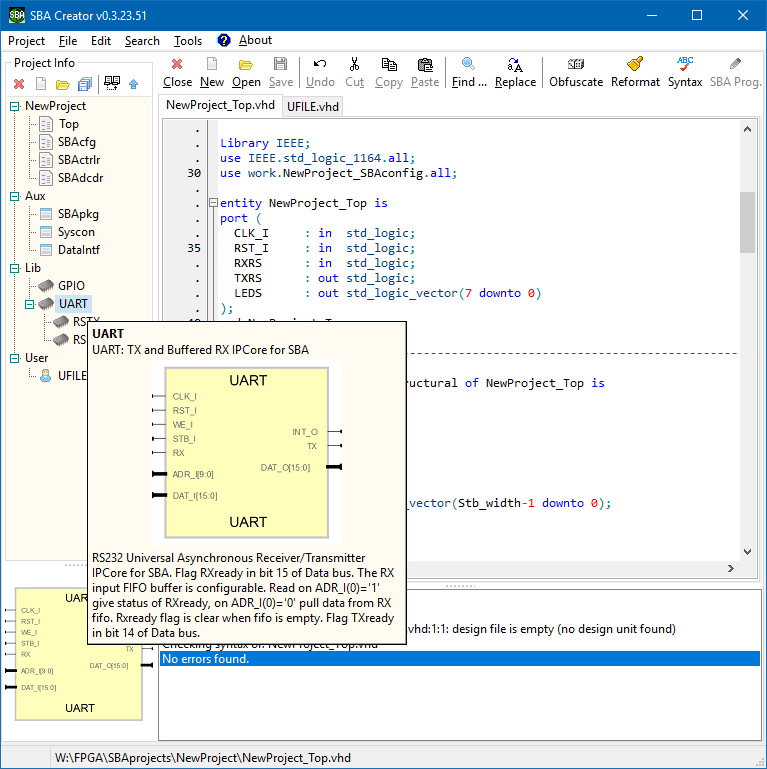

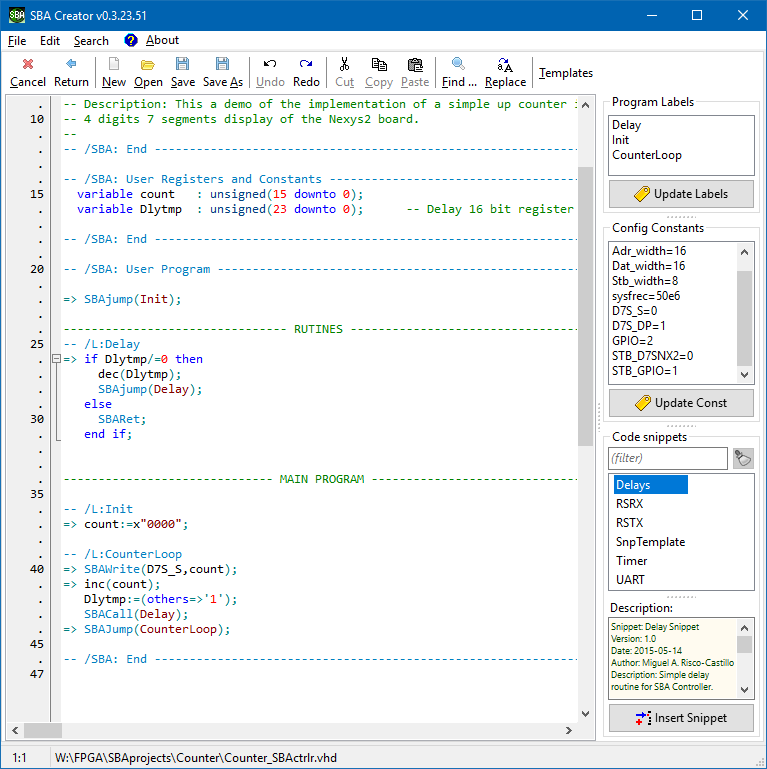

The Simple Bus Architecture (SBA) is an architecture made up software tools and intellectual property cores (IP Cores) interconnected by buses set through simple and clear rules, that allow the implementation of an embedded system (SoC); additionally, basic templates are provided to achieve a rapid design. Its structure gives it an inherent educative value. The VHDL code that implements this architecture is highly portable.

The master core developed as special state machine, has the ability to perform basic data flow and processing, similar to microprocessor but without the high consumption of logic resources of it.

The SBA is an application and simplified version of the Wishbone specification. The SBA implements the minimum essential subset of Wishbone signals interface, and can be easily connected with simple Wishbone IP Cores. The SBA defines three types of cores: masters, slaves and auxiliaries. Several slaves IP Cores were developed following the SBA architecture, many of them to implement virtual instruments.