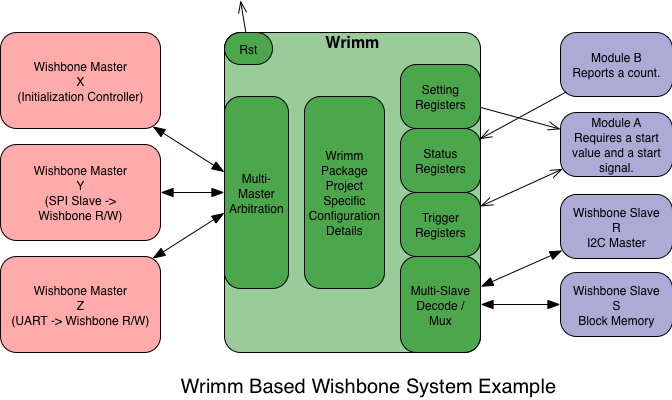

Wishbone Register Bank Intercon Multi-master Multi-slave

Project maintainers

Details

Created: Jun 28, 2014

Updated: Jul 27, 2014

SVN Updated: Jul 28, 2014

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:VHDL

Development status:Beta

Additional info:Design done, FPGA proven

WishBone compliant: Yes

WishBone version: n/a

License: BSD

Concept

Overview

If your projects are like ours, you always need the capability to set configuration bits for internal components, or externally monitor the status of other components. We have implemented this in many different ways across dozens of projects. We hope Wrimm is the last time we re-develop this same functionality.

Every new design needs a different set of registers. Frequently improving an existing design requires adding or changing a register which also requires some level of re-development of the register logic.

The goal of Wrimm is a fully tested logic block that doesn't change from design to design or during design revision. Everything necessary to add and configure general purpose registers is contained in constant declarations in a VHDL package file.

Along the way we also incorporated some other Wishbone functionality we frequently find useful.

Capabilities

- Wishbone Support - All the registers and other functions are readable and writeable via Wishbone compatible masters.

- Parametric Wishbone Bus - Wishbone address and data bus widths are configurable with a constant setting.

- Glueless Interface - Wishbone masters and slaves connect to Wrimm with the standard Wishbone Interface. All required glue logic is automatically generated inside Wrimm.

- Parametric Register Configuration - The bit size and address locations for all the following register types are configurable in the project package file. Register fields of different types may even share the same address (in different bit locations).

- Setting Registers - Setting registers offer bit vector outputs to provide configuration to non-Wishbone modules.

- Status Registers - Status registers offer bit vector inputs to collect status information from non-Wishbone modules and provide that data via Wishbone reads.

- Trigger Registers - Trigger registers are single bit registers used to launch other non-Wishbone on-chip processes. The triggers are then cleared by those functions.

- Wishbone Record Type Interfaces - The multi-signal wishbone interface is represented in two custom record types for a shorter, cleaner interface.

- Multi Wishbone Master Support - Any number of masters can be connected. Round robbin arbitration is provided for all masters.

- TBD- Multi Wishbone Slave Support - Any number of wishbone slaves may be attached to the Wrimm component. Partial address decoding support is provided. Data, Ack, Rty, and Err signals are automatically muxed together to respond to the master with the grant.

- TBD- Wishbone Reset Support - Automatically drive Rst when requests go unanswered.

- Adaptive Testbench - Test bench also uses constant data from the package file to enable testing of the project specific configuration.

- 100% Synthesizeable VHDL - All custom configuration is done in VHDL no other scripting language or intermediate compilation is required.

Documentation

All documentation outside this brief description is contained in WrimmManual.pdf.

Description

Wrimm provides Wishbone interconnect functionality, multi-master arbitration, multi-slave partial address deccoding and bus multiplexing. Wrimm also incoporates configurable register bits for controlling and monitoring non-Wishbone functions.