Adjustable Frequency Divider

Project maintainers

Details

Name: freq_div

Created: May 9, 2010

Updated: Jan 21, 2016

SVN Updated: Jul 23, 2010

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 2 reported / 0 solved

Created: May 9, 2010

Updated: Jan 21, 2016

SVN Updated: Jul 23, 2010

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 2 reported / 0 solved

Star9you like it: star it!

Other project properties

Category:Other

Language:Verilog

Development status:Stable

Additional info:ASIC proven, Design done, Specification done

WishBone compliant: No

WishBone version: n/a

License: LGPL

Language:Verilog

Development status:Stable

Additional info:ASIC proven, Design done, Specification done

WishBone compliant: No

WishBone version: n/a

License: LGPL

Usage and Operation

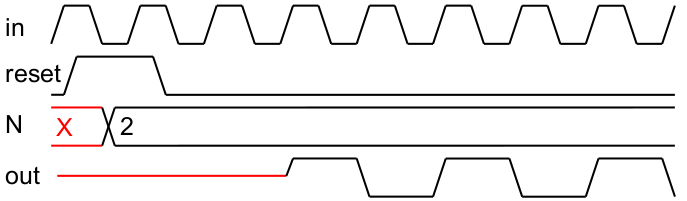

In order to operate the circuit correctly it must first be reset (asynchronously).

Below is a timing diagram that illustrates the reset pulse timing requirements.

Note: the circuit only needs to be reset once to operate properly. Every time the divide factor N changes, the circuit automatically resets itself.

Specifications

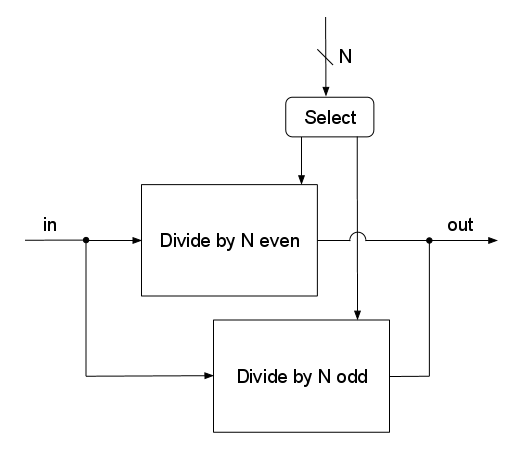

The adjustable frequency divider is designed in two parts:

- Even Divider When the input signal 'N' is set to an even number the even divider is used because the output will be synchronized with the rising edges of the input clock. The even divider has a much simpler architecture consisting of basically cascaded flip-flops.

- Odd Divider When 'N' is odd the output needs to be synchronized with both the rising and falling edges of the input clock in order to achieve a 50% duty cycle output. The odd divider is much more complex than the even divider and requires two internal counters that are offset from each other.

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.