I2C Multiple Bus Controller

Project maintainers

Details

Created: Apr 29, 2016

Updated: Jul 2, 2022

SVN Updated: Jun 30, 2016

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 4 reported / 4 solved

Other project properties

Language:VHDL

Development status:Stable

Additional info:Design done, FPGA proven, Specification done

WishBone compliant: Yes

WishBone version: n/a

License: BSD

Description

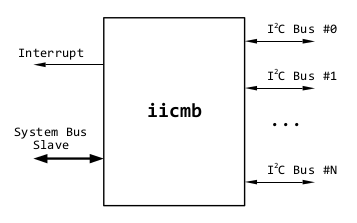

The IICMB core provides low-speed, two-wire, bidirectional serial bus interfaces compliant to industry standard I2C protocol.

The key feature of the core is its ability to control several connected I2C buses effectively reducing complexity of the system.

Features

- Compatible with Philips' I2C standard

- Works with up to 16 distinct I2C buses

- Statically configurable system bus clock frequency

- Statically configurable desired clock frequencies of I2C buses

- Multi-master clock synchronization

- Multi-master arbitration

- Clock stretching

- Digital filtering of SCL and SDA inputs

- Standard (up to 100 kHz) and Fast (up to 400 kHz) mode operation

- Example connection as 8-bit slave on Wishbone bus

- Example connection as 32-bit slave on Avalon-MM bus

- Sequencer-based example, working without any system bus

Limitations

Currently supported master mode only.