Potato Processor

Project maintainers

Details

Name: potato

Created: Apr 8, 2015

Updated: Nov 27, 2015

SVN Updated: Nov 14, 2015

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 9 reported / 7 solved

Created: Apr 8, 2015

Updated: Nov 27, 2015

SVN Updated: Nov 14, 2015

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 9 reported / 7 solved

Star3you like it: star it!

Other project properties

Category:Processor

Language:VHDL

Development status:Alpha

Additional info:Design done, FPGA proven

WishBone compliant: Yes

WishBone version: n/a

License: BSD

Language:VHDL

Development status:Alpha

Additional info:Design done, FPGA proven

WishBone compliant: Yes

WishBone version: n/a

License: BSD

The Potato Processor

Development of the Potato Processor has moved to GitHub, check it out on https://github.com/skordal/potato

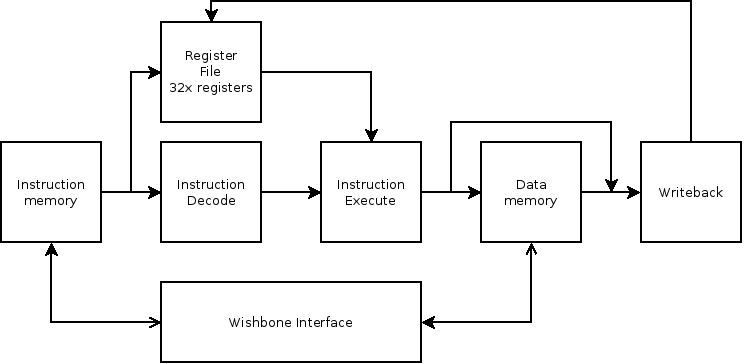

The Potato Processor is a lightweight implementation of the RISC-V 32-bit integer ISA. It is implemented in VHDL, with a classic 5-stage RISC pipeline.

The processor datasheet can be downloaded here.

Notable features are:

- Supports the full RV32I subset of the RISC-V ISA, version 2.0.

- Supports machine mode as defined by the RISC-V supervisor extensions, version 1.7.

- Provides support for handling up to 8 IRQs without needing a separate interrupt controller.

- Single-cycle execution of all instructions except memory load/store.

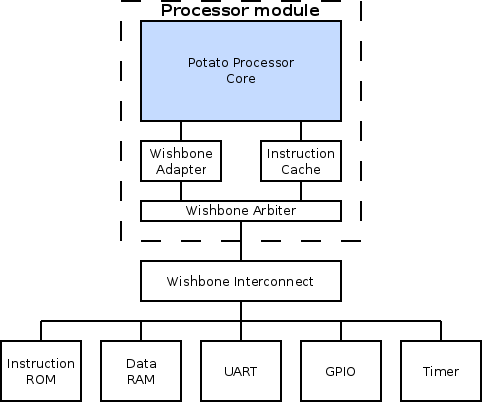

- Includes a Wishbone compatible interface for integration into Wishbone-based systems.

The processor has been tested on a Nexys 4 board from Digilent. The design used for testing is included in the source distribution, with instructions on how to get it up and running.

Example Design

An example design is included in the source distribution of the processor. Instructions on how to build and test this design is located in the example/ subdirectory of the Potato sources.

© copyright 1999-2018 OpenCores.org, equivalent to Oliscience, all rights reserved. OpenCores®, registered trademark.