System-On-Chip based on bare Rocket-chip (RISC-V ISA)

Project maintainers

Details

Created: Mar 4, 2016

Updated: Sep 27, 2018

SVN Updated: Nov 17, 2018

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 1 reported / 1 solved

Other project properties

Language:VHDL

Development status:Beta

Additional info:Design done, FPGA proven

WishBone compliant: No

WishBone version: n/a

License: BSD

Repository

System-on-Chip source is hosted on Sergey Khabarov's github page.

Clone a copy of the repository with git like so:

$ git clone https://github.com/sergeykhbr/riscv_vhdl.git

Link to the documentation in pdf-format.Overview

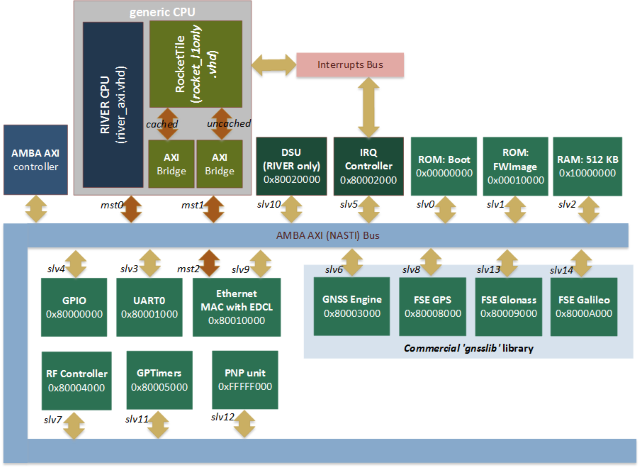

The IP Library is an integrated set of reusable IP cores, designed for system-on-chip (SOC) development. The IP cores are centered around a common on-chip AMBA AXI system bus and BSD licensed "Rocket Chip" implementing open RISC-V ISA. All IP cores use a coherent method for simulation and synthesis. This library is vendor independent, with support for different CAD tools and target technologies. Inherited from gaisler GRLIB library plug&play method was further developed and used to configure and connect the IP cores without the need to modify any global resources.

Description

Common top-level structure.

* CPU: Single core "Rocket-chip": 64-bits CPU (RISC-V ISA) with L1/L2 caches, MMU, TLBs, 128-bits data bus and etc.

* General set of peripheries: GPIO, LEDs, UART, IRQ controller etc.

* Portable asynchronous FIFO implementation allowing to connect modules to the System BUS from a separate clock domains (ADC clock domain):

Fast Search Engines

* Ethernet MAC 10/100Mb (gigabit MAC by request) with the debug function (EDCL) that allows redirect UDP requests directly on system BUS.

* Debug Support Unit (DSU) provides access to all processors CSRs.

* Satellite navigation modules are distributed as a netlist files (in *.ngc format) or as a stubs.