sd card controller

sd card controller

Project maintainers

Details

Created: Mar 27, 2009

Updated: Feb 11, 2017

SVN Updated: Oct 15, 2010

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 17 reported / 7 solved

Other project properties

Language:Verilog

Development status:Stable

Additional info:Design done, FPGA proven, Specification done

WishBone compliant: Yes

WishBone version: n/a

License: LGPL

Introduction

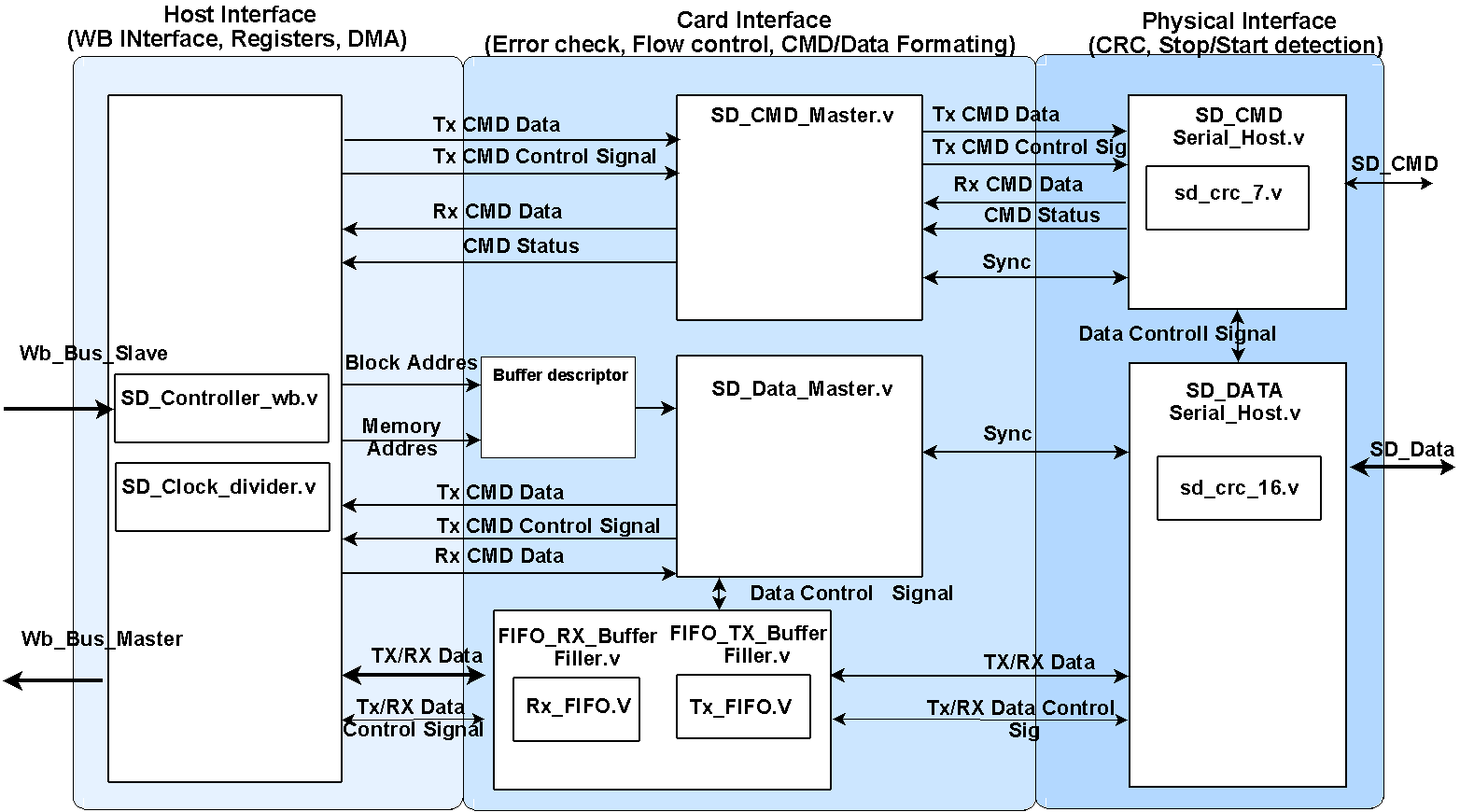

The "sd card controller" is a Secure Digital Card Host Controller, which main focus is to provide fast and simple interface to SD/SDHC cards. One of the main goal with this project is that the controller should be usable as a system disk contain a file system. Therefore the core has been developed with features a system with operative system will benefit from.

The design also include a simplified model of a SD-card to test against.

Description

The core is a combined SD/SDHC controller, for Secure Digital-card.

Two designs is available, one full-feature core utilizing DMA and one smaller for PIO.

The idea with the full-feature design is that it should provide as much performance as possible. Therefore it's build to stall the CPU as little as possible and offload it some computations, this is archived by:

- Error and flow control performed mainly in hardware i.e user specify when sending a command what kind of error check he wants to be performed. Result is then set in the response registers also can be set to generate interrupt.

- Command generation for writing/reading block of data is performed in hardware

- Buffer descriptors is used to to queue read/write data transmissions (Less delay between data transmissions)

- DMA for minimal CPU interruption as possible.

Features

Full-feature core

- 32-bit Wishbone Interface

- DMA

- Buffer Descriptor

- Compliant with SD Host Controller Spec version 2.0

- Support SD 4-bit mode

- Interrupt-on completion of Data and Command transmission

- Write/Read FIFO with variable size

- Internal implementation of CRC16 for data lines and CRC7 for command line

Small-FIFO core

- 8-bit Wishbone Interface

- PIO

- Compliant with SD Host Controller Spec version 2.0

- Support SD 4-bit mode

- Simple SW interface, 4 FIFO + 4 Registers

Limitations

Data block length fixed to 512 Byte

No SD 1-bit mode

No SPI mode

No Hot Insertion (i.e. inserting a card when the bus is operating)

No multiple block operations/pre erase