VHDL Whisbone Test Bench

Project maintainers

Details

Created: Jul 17, 2018

Updated: Apr 19, 2021

SVN Updated: Apr 19, 2021

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:VHDL

Development status:Stable

Additional info:Design done, FPGA proven, Specification done

WishBone compliant: Yes

WishBone version: B.3

License: LGPL

CAUTION: Latest version download does not work. Use SVN:Browse instead

Description

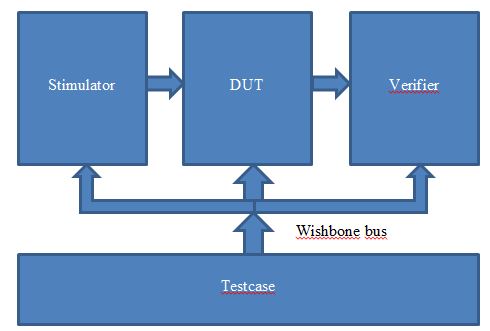

For the development of IP cores a test bench is needed. The given project provides a test bench written in VHDL which controls the stimulus,the verifier and the DUT via a common wishbone bus function model. The bfm acts like a virtual CPU performing read and write accesses to the control wishbone bus.

tc-files(uses wb_bfm_procedures) => wishbone_bus ->

-> stimulator (writes or generates DUT inputs)

-> verifier (reads or checks DUT outptus)

-> DUT (configures DUT via WB accesses)

In contrast to Ken Campbells "The VHDL Test Bench"(https://opencores.org/project/vhld_tb) we do not use an interpreter for the bfm functions. We use plain VHDL which requires VHDL knowledge for test definitions, but also provides more flexibility.

Testbench architecture:

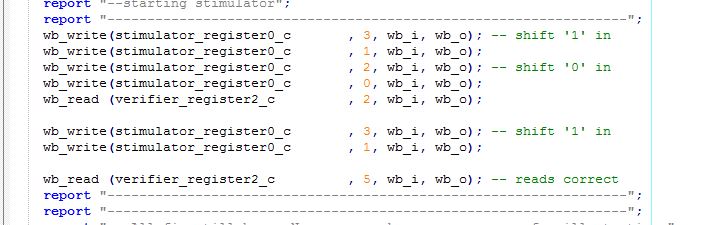

Example test flow programming (reads and writes via wb):

Please report problems and suggestions for improvements..