YAC - Yet Another CORDIC Core

Project maintainers

Details

Created: Mar 2, 2014

Updated: Jun 22, 2015

SVN Updated: Jun 22, 2015

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 0 reported / 0 solved

Other project properties

Language:VHDL

Development status:Alpha

Additional info:Design done, FPGA proven, Specification done

WishBone compliant: Yes

WishBone version: n/a

License: LGPL

Description

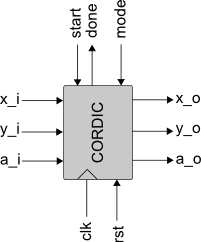

CORDIC is the acronym for COordinate Rotation DIgital Computer and allows a hardware efficient calculation of various functions like

- atan, sin, cos

- atanh, sinh, cosh,

- division, multiplication.

Hardware efficient means, that only shifting, additions and substractions in combination with table-lookup is required. This makes it suitable for a realization in digital hardware. Good introductions can be found in [1][2][3][4].

The following six CORDIC modes are supported:

- trigonometric rotation

- trigonometric vectoring

- linear rotation

- linear vectoring

- hyperbolic rotation

- hyperbolic vectoring

Furthermore, the CORDIC algorithm is implemented for iterative processing which means, that the IP-core is

started with a set of input data and after a specific amount of clock cycles, the result is

available. No parallel data can be processed.

In addition to an IP-core written in VHDL, a bit-accurate C-model is provided. This C-model can be compiled as mex for a usage with Octave or Matlab. Therefore, this C-model allows a bit-accurate analysis of the CORDIC performance on a higher level.

Status

- C-model implementation is done

- RTL model implementation is done

- RTL model is verified against C-model

- Wishbone-bus wrapper is added

- Included into a small SoC, tested on a spartan-3 FPGA

Open issues and future steps

The next steps are

- Circuit optimizations

- Numerical optimizations

and the future plans are

- Hyperbolic range extension

- Floating point CORDIC

Bibliography

[1] Andraka, Ray; A survey of CORDIC algorithms for FPGA based computers, 1989

[2] Hu, Yu Hen; CORDIC-Based VLSI Architectures for Digital Signal Processing, 1992

[3] CORDIC on wikibook: http://en.wikibooks.org/wiki/Digital_Circuits/CORDIC

[4] CORDIC on wikipedia:http://en.wikipedia.org/wiki/CORDIC

[5] David, Herbert; Meyr, Heinricht; CORDIC Algorithms and Architectures

http://www.eecs.berkeley.edu/newton/Classes/EE290sp99/lectures/ee290aSp996_1/cordic_chap24.pdf